VHDL9:quartusII工程下调用另一个工程下vhd文件并仿真,vhdl中component的使用

目录

1. 示例说明

2. job1: 建立job_single工程

3. job1: 在job_single工程下创建job_single.vhd源码文件

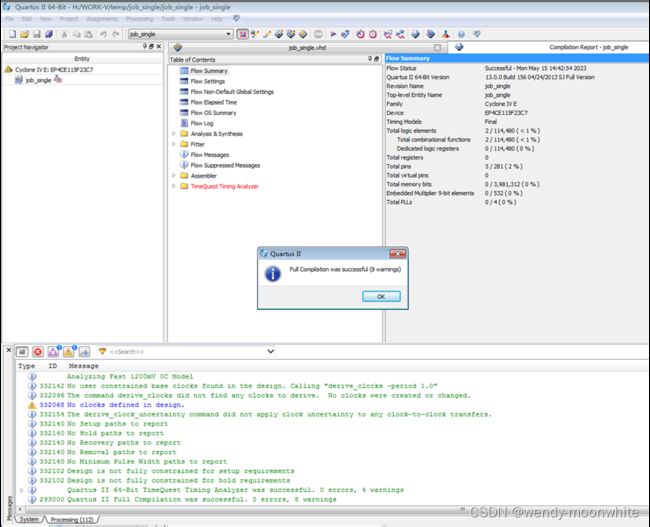

4. job1: 工程job_single编译结果

5. job2: 建立job_total工程

6. job2: 在job_total工程下创建 job_total.vhd源码文件

7. job2: 工程job_total下引入job_single工程目录

8. job2: 工程job_total编译结果

9. job2: 功能仿真结果

10. 文件引用说明

1. 示例说明

本例是两个quartus II的工程文件:

job_single.qpf - 包含job_single.vhd文件

job_total.qpf - 包含job_total.vhd文件

其中实现的是在job_total工程目录里下引入job_single工程的过程。

工程调用调用关系如下:

2. job1: 建立job_single工程

3. job1: 在job_single工程下创建job_single.vhd源码文件

job_single源码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity job_single is

port(

X : in STD_LOGIC;

Y : in STD_LOGIC;

C_in : in STD_LOGIC;

Sum : out STD_LOGIC;

C_out : out STD_LOGIC);

end job_single;

architecture behav of job_single is

begin

process(X, Y, C_in)

begin

Sum <= (X xor Y) xor C_in;

C_out <= (X and Y) or (C_in and X) or (C_in and Y);

end process;

end behav;

4. job1: 工程job_single编译结果

5. job2: 建立job_total工程

6. job2: 在job_total工程下创建 job_total.vhd源码文件

job_total.vhd源码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity job_total is

port(

X : in STD_LOGIC_VECTOR(1 downto 0);

Y : IN STD_LOGIC_VECTOR(1 downto 0);

C_in : in STD_LOGIC;

Sum : out STD_LOGIC_VECTOR(1 downto 0);

C_out : out STD_LOGIC);

end job_total;

architecture behav of job_total is

component job_single

port(

X: in STD_LOGIC;

Y: in STD_LOGIC;

C_in: in STD_LOGIC;

Sum: out STD_LOGIC;

C_out: out STD_LOGIC

);

end component;

signal C_temp: std_logic;

begin

A1: job_single

port map(X(0), Y(0), C_in, Sum(0), C_temp);

A2: job_single

port map(X(1), Y(1), C_in, Sum(1), C_out);

end behav;