FPGA设计时序约束十一、others类约束之Set_Maximum_Time_Borrow

目录

一、序言

二、Set Maximum Time Borrow

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、参考资料

一、序言

在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序路径分析,以Vivado2022.1版本为例,主要包括以下4类,本文将介绍其中的最后一个Set_Maxium_Time_Borrow,示例的为Vivado2022.1

二、Set Maximum Time Borrow

2.1 基本概念

Set_maximum_time_borrow约束是指当分析锁存器Latch的时序时,设置可以从线nets中获取的最大时间值(纳秒即)。存储电路设计有两种类型:触发器(Flip Flop)和锁存器(Latch)。

a)使用触发器的设计

数据从时钟的上升沿启动,必须在下一个时钟上升沿到达前的set up时间内到达目的触发器,如果两个触发器的组合逻辑时延太大,那么数据将没法被捕获触发器所捕获,捕获的数据将不稳定,如果数据到达的时间太早,造成时间资源浪费

b)使用锁存器的设计

当锁存器是传输状态时将透传数据,如果锁存器前的组合逻辑时延较大时,将借用下一个周期的时间,所以当需要设计有较高的性能时,会使用锁存器

时间借用的场景:从设计中的锁存器借用,借用的时间用于设计中的触发器。

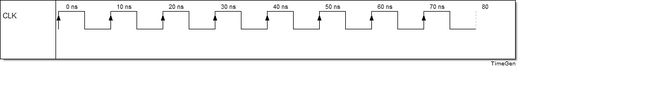

时钟波形如下,周期为10ns,占空比为50%。

当数据从触发器FF1出发,理想情况下(setup、hold和时钟延迟,时钟偏斜都为0)在下一个时钟周期10ns后到达触发器FF2,如果数据到达FF2的时间大于10ns,则无法被FF2捕获,同样的在20ns后到达FF3被捕获。

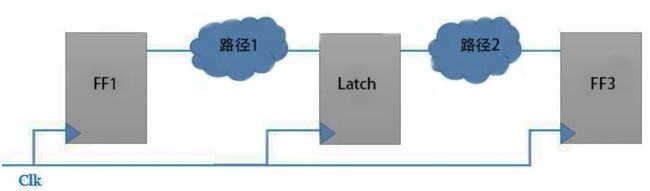

将路径图中的FF2换成锁存器Latch,如下图

如果数据从FF1出发到达Latch的输入端口D早于10ns,此时锁存器由于CLK为低电平不工作,不会影响数据的获取,和使用FF的场景相同。

如果数据从FF1出发到达Latch的输入端口D大于10ns,如12ns时到达,如果Latch为FF2时数据将无法被捕获,此时为锁存器,只有数据在10ns-15ns时到达,数据依旧传输到了FF3,这时通过借用下一个周期的时间,12ns到达时相比使用寄存器FF2,锁存器提供了2ns的优势。

在这个例子中锁存器所能借用的最大时间为5ns(一个周期中高电平的有效时间),但从锁存器到寄存器FF3的时间减少了,原先是10ns,借用后必须8ns内到达,以便FF3在20ns时能获取到数据,因为从FF1到FF3总的20ns时间关系是不变的。

因此,在使用寄存器的设计中,组合逻辑的延时不能超过一个时钟周期,除非一些特殊设置,如多周期约束路径和false路径。在使用锁存器的设计中,大的组合逻辑延时可以通过下一级更短的组合逻辑延时来补偿。

2.2 设置界面

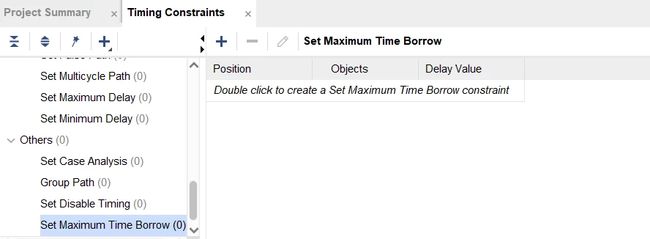

进入Timing Constraints界面,在左侧Others栏中选中Set Maximum Time Borrow,右侧即显示Set Maximum Time Borrow

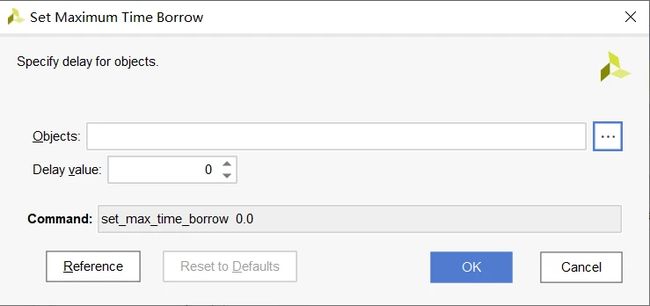

设置界面中需设置对象objects和借用的时延值delay value

约束设置子界面需设置Objects,可为clocks或cells

2.3 命令语法

命令格式

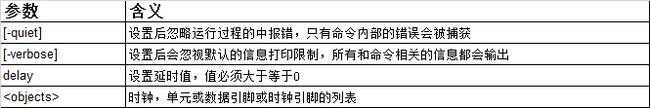

set_max_time_borrow [‑quiet] [‑verbose] 参数含义

2.4 命令示例

1、约束所有时钟相关的锁存器允许借用的时间为0,这等于阻止了整个设计的时间借用

set_max_time_borrow 0.0 [all_clocks]2、约束了顶层net允许借用20个时间单元

set_max_time_borrow 20 {top/*}三、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt