FPGA设计时序约束十二、Set_Clock_Sense

目录

一、序言

二、Set Clock Sense

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、工程示例

3.1 工程代码

3.2 无set_clock_sense

3.3 设置set_clock_sense

四、参考资料

一、序言

本章将介绍Set_Clock_Sense约束,在介绍约束之前,大家需对时序弧以及timing sense有一定的基础了解,具体可参考另一篇文章《FPGA设计时序分析概念之Timing Arc》

链接:https://blog.csdn.net/zyp626/article/details/134890605?spm=1001.2014.3001.5501

二、Set Clock Sense

2.1 基本概念

Set_Clock_Sense约束用于定义时钟引脚的单边性Unateness,并且只能用于时钟网络中单边性状态为non-unate的引脚,该引脚上的时钟信号是无法确定的,在设置约束后,约束的时钟单边性状态将从约束的引脚向前传输。

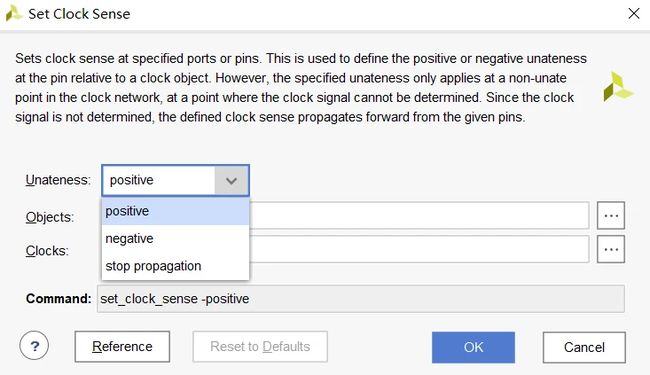

2.2 设置界面

进入Timing Constraints界面,在左侧Others栏中选中Set Clock Sense,右侧即显示Set Clock Sense

设置界面中需设置单边性Unateness,可为positive/negative/stop propagation

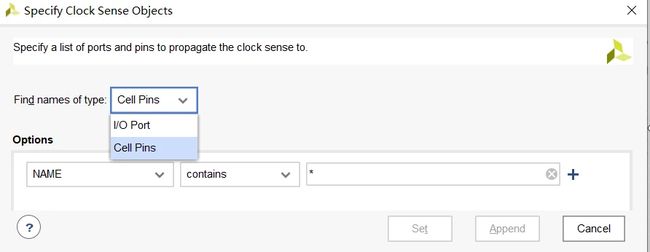

约束设置子界面中Objects,可为I/O port或cell pins

Clock中选定设置clock sense的时钟

2.3 命令语法

命令格式

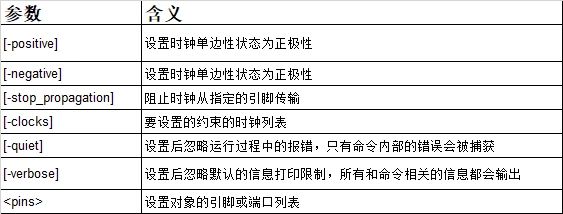

set_clock_sense [‑positive] [‑negative] [‑stop_propagation] [‑clocks ] [‑quiet] [‑verbose] 参数含义

2.4 命令示例

1、约束xor门中输出引脚z与初始时钟的极性状态为正极性positive unate

set_clock_sense -positive [get_pins xor_a.z]三、工程示例

3.1 工程代码

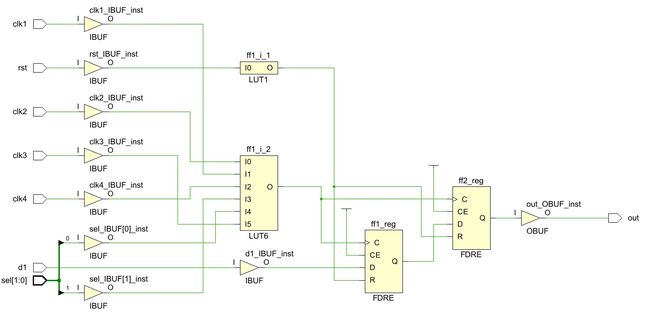

设计中四路输入时钟通过一个多路选择器为两个级联的触发器提供时钟信号

module set_clock_sense(d1,clk1,clk2,clk3,clk4,rst,sel,out);

output out;

input d1,rst;

input [1:0] sel;

input clk1,clk2,clk3,clk4;

reg mux,ff1,ff2;

wire mux_n;

always@(sel)

begin

case(sel)

2'b00:mux<=clk1;

2'b01:mux<=clk2;

2'b10:mux<=clk3;

2'b11:mux<=clk4;

endcase

end

assign mux_n=mux;

always@(posedge mux_n)

begin

if(!rst)

ff1<=1'b0;

else

ff1<=d1;

end

always@(posedge mux_n)

begin

if(!rst)

ff2<=1'b0;

else

ff2<=ff1;

end

assign out=ff2;

endmodule综合网表连接图,多路选择器是用一个LUT6实现

3.2 无set_clock_sense

约束文件:

create_clock -period 1.000 -name clk1 -waveform {0.000 0.500} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

create_clock -period 7.000 -name clk3 -waveform {0.000 3.500} [get_ports clk3]

create_clock -period 3.000 -name clk4 -waveform {0.000 1.500} [get_ports clk4]

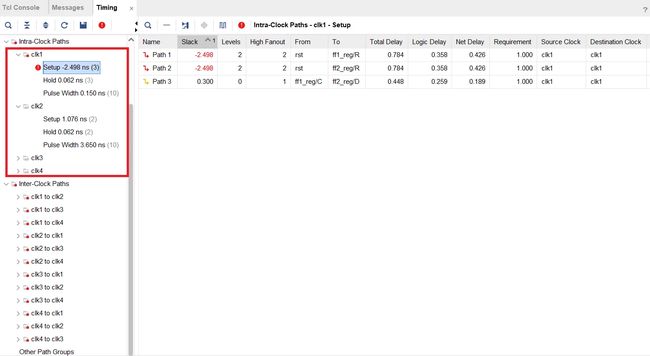

时序报告结果如下,

3.3 设置set_clock_sense

约束文件中对clk1不设set_clock_sense约束,clk2,clk3,clk4分别设置参数positive,negative,stop_propagation,注意:约束的位置需约束单元的Timing Sense状态为Unateness的输出引脚才行,如LUT,XOR异或门单元等,此处为ff1_i_2/O,即LUT的输出

create_clock -period 1.000 -name clk1 -waveform {0.000 0.500} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

create_clock -period 7.000 -name clk3 -waveform {0.000 3.500} [get_ports clk3]

create_clock -period 3.000 -name clk4 -waveform {0.000 1.500} [get_ports clk4]

set_clock_sense -positive -clocks [get_clocks clk2] [get_pins ff1_i_2/O]

set_clock_sense -negative -clocks [get_clocks clk3] [get_pins ff1_i_2/O]

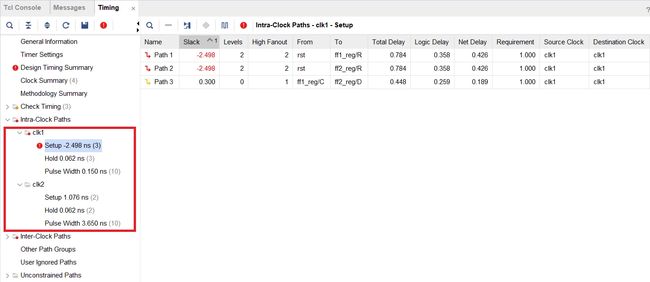

set_clock_sense -stop_propagation -clocks [get_clocks clk4] [get_pins ff1_i_2/O]时序报告结果中同步时钟域中只剩下clk1,clk2。clk4的时序路径不存在是因为设置了stop_propagation,该条路径断开,clk3断开是由于只支持极性为positive的时序切换传输,因此,设置为negative也是路径断开,clk2设置的positive正常传输

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt