FPGA平台以太网学习:涉及1G/2.5G Ethernet 和Tri Mode Ethernet MAC两个IP核的学习记录(一)——知识补给

学习不能稀里糊涂,要学会多思考,发散式学习以及总结:

FPGA作为一种器件,只是实现目的的一种方法,过度追求实现的技术细节(用hdl还是hls,用啥芯片,用啥接口)容易只见树木不见森林。工具软件的用法也好,器件的架构也好,语言孰优孰劣的争论也罢。工程应用里大概更多应该去考虑适合的实现方式,现在software define network/flash/xxx,已然大势所趋,算法是纲,纲举目张。是因为在实现上需要有流水线,多路并行,快速部署的目的所以考虑使用FPGA,而不是为了使用而使用。

不管实现目的的方法是FPGA还是DSP甚至是GPU,这些都是工具,工程师的核心竞争力除了在于熟练地掌握开发的技巧。更重要的在于信号与系统、数字信号处理、图像处理之类的让你了解算法、优化算法的基石;以及数字电路、微机原理、处理器体系结构这些让你了解为什么这些工具要这样设计,要这样发展的课程(系统学习一点体系结构,那么这些数据级并行、指令级并行、线程级并行的处理器就不再陌生了)工程师应该顶天(了解应用,了解算法)也应该立地(了解工具,掌握技巧)。

——引用某个大佬的话,作为学习共勉

简单来说就是:FPGA是工具用来搬砖,更多的知识在FPGA之外

不会添加跳转目录,为了方便大家一目了然,手打目录(右下角可以跳转对应区域)

一、FPGA平台以太网构架学习(知识普及)

二、MAC侧与PHY间的通信

三、PHY与RJ-45间的通信

四、千兆网协议帧(链路层MAC,编写FPGA代码时重点学习)

五、实际中以太网通信方式

一、FPGA平台以太网构架学习(知识普及)

本系列文章是基于FPGA的以太网IP进行学习,通过查阅资料,根据自己的理解进行整合,作为自己的总结学习;

在使用IP核之前,做好以太网知识的基础学习,想要了解深入的,我都会添加部分链接。

首先要了解下网络的七层协议,就如上图所示,数据封装的过程是从上往下,数据的解封装则是从下到上,本次基于FPGA的以太网IP核的学习只涉及到数据链路层和物理层;

数据链路层:定义了链路上如何传输数据,如何将数据组合成数据块,在数据链路层中称这种数据块为帧,帧是数据链路层的传送单位,通过一些规程或协议来控制这些数据的传输,以保证被传输数据的正确性。

数据链路层的芯片可以称为:MAC(即本次学习的FPGA端)

物理层:处于最底层,却是整个开放系统的基础,物理层为设备之间的数据通信提供传输媒体及互连设备,为数据传输提供可靠的环境,提供传送数据通路(物理媒体)、传输数据(实体)。

物理层的芯片可以称为:PHY

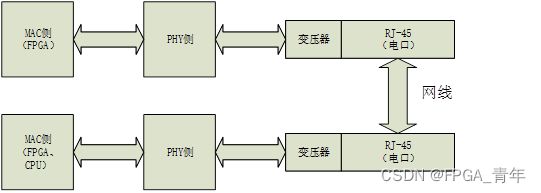

网络变压器的作用是为了转换数据类型适配所有的网线(可有可无);RJ-45就是我们通常用到的网线头,在这里我们先上一个图,后续会详细讲解:

其他的协议层暂时没有涉及到,用了再进行补充,了解的话可以参考此链接:

封装与解封装_封装解封装_李林楠的博客-CSDN博客

二、MAC侧与PHY间的通信

以太网的通信离不开物理层PHY芯片的支持,以太网MAC和PHY之间有一个接口,常用的接口有MII、RMII、GMII、RGMII、SGMII等。

MII(MediumIndependent Interface,媒体独立接口):MII支持10Mbps和100Mbps 的操作,数据位宽为4位,在100Mbps传输速率下,时钟频率为25Mhz。

RMII(Reduced MII):RMII是MII的简化版,数据位宽为2位,在100Mbps 传输速率下,时钟频率为50Mhz。

GMII(Gigabit MII):GMII接口向下兼容MII接口,支持10Mbps、100Mbps和1000Mbps 的操作,数据位宽为8位,在1000Mbps传输速率下,时钟频率为125Mhz。

RGMII(Reduced GMII):RGMII是 GMII 的简化版,数据位宽为4位,在1000Mbps传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据。在100Mbps和10Mbps 通信速率下,为单个时钟沿采样。

SGMII(Serial GMII,串行GMII):收发各一对差分信号线,1000Mbps传输速率下,时钟频率125MHz,在时钟信号的上升沿和下降沿均采样,采用的接口比RGMII少。

详细对比可以参考此大佬写的文章:

Xilinx- FPGA平台以太网接口(二)系统架构_fpga实现以太网接口_子墨祭的博客-CSDN博客

在千兆以太网中,常用的接口为RGMII和GMII接口。RGMII接口的优势是同时适用于 10M/100M/1000Mbps通信速率,同时占用的引脚数较少。但RGMII接口也有其缺点,就是在PCB布线时需要尽可能对时钟、控制和数据线进行等长处理,且时序约束相对也更为严格。我们在这里简单介绍下RGMII的接口含义:

RGMII接口

ETH_RXC:接收数据参考时钟,1000Mbps速率下,时钟频率为125MHz,时钟为上下沿同时采样; 100Mbps速率下,时钟频率为25MHz;10Mbps速率下,时钟频率为2.5MHz,ETH_RXC 由 PHY 侧提供。

ETH_RXCTL(ETH_RX_DV):接收数据控制信号。

ETH_RXD:四位并行的接收数据线。

ETH_TXC:发送参考时钟,1000Mbps速率下,时钟频率为125MHz,时钟为上下沿同时采样;100Mbp速率下,时钟频率为25MHz;10Mbps速率下,时钟频率为2.5MHz,ETH_TXC由MAC侧提供。

ETH_TXCTL(ETH_TXEN):发送数据控制信号。

ETH_TXD:四位并行的发送数据线。

ETH_RESET_N:芯片复位信号,低电平有效。

ETH_MDC:数据管理时钟(Management Data Clock),该引脚对ETH_MDIO信号提供了一个同步的时钟。

ETH_MDIO:数据输入/输出管理(ManagementData Input/Output),该引脚提供了一个双向信号用于传递管理信息。

ETH_MDC和ETH_MDIO为MDIO接口引脚,用于配置PHY芯片内部寄存器,ETH_RST_N为PHY芯片硬件复位信号,PHY芯片的内部寄存器在默认配置下也可以正常工作。

本次学习使用FPGA的以太网IP核(1G/2.5GEthernet PCS/PMA or SGMII),不涉及此部分的知识,采用的是高速GT接口,后续将详细介绍,所以在此不再做深入了解,如果使用到的以太网IP核是三速以太网(Tri Mode Ethernet MAC)时,再对这些接口进行时序分析等,现目的是了解。关于三速以太网的知识可以参考以下链接:

Xilinx- FPGA平台以太网接口(三)IP核配置及接口介绍_xilinx 以太网ip_子墨祭的博客-CSDN博客

浅析Xilinx 三速以太网MAC IP核(仿真篇) - 没落骑士 - 博客园 (cnblogs.com)

三、PHY与RJ-45间的通信

1、以太网PHY芯片知识:

PHY是TCP/IP协议栈中的物理层器件,也就是我们常说的PHY芯片,如88E1111,支持不同形式的数据转换,例如支持1000BASE-T、100BASE-T、10BASE-T类型的以太网传输。

这里就要简单了解下1000BASE的传输介质的标准,可以分为BASE-X(X可以换成LX,ZX,SX和CX)单/多模光纤以及BASE-T Cat网线;

Base-X 光口(光纤) 例10/100/1000Base-X;

Base-T 电口(同轴电缆) 例10/100/1000Base-T;

Base-TX 电口(双绞线) 例10/100/1000Base-TX;

关于1000BASE的区别可以参考此链接:

1000BASE_百度百科 (baidu.com)

从硬件的角度来说,以太网接口电路主要由MAC(Media Access Control)控制器和物理层接口PHY(Physical Layer,PHY)两大部分构成。MAC指媒体访问控制子层协议,它和 PHY接口既可以整合到单颗芯片内,也可以独立分开。

PHY 在发送数据的时候,接收MAC发过来的数据(对PHY来说,没有帧的概念,都是数据而不管什么地址,数据还是CRC),把并行数据转化为串行流数据,按照物理层的编码规则把数据编码转换为模拟信号发送出去,接收数据时的流程反之。PHY还提供了和对端设备连接的重要功能,并通过LED灯显示出自己目前的连接状态和工作状态。当我们给网卡接入网线的时候,PHY芯片不断发出脉冲信号来检测对端是否有设备,它们通过标准的“语言”交流,互相协商并确定连接速度、双工模式、是否采用流控等。通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式。这个技术被称为Auto Negotiation,即自协商。

关于PHY芯片中的协议知识,可以参考以下文章,将对我们使用IP时候有很好的帮助。

FPGA平台以太网学习:MAC与PHY间通信_FPGA_青年的博客-CSDN博客

2、RJ-45知识:

下图是目前项目中正在使用的一个MCH交换卡,在本章的第五节我会讲讲一下交换机的一些知识。网口可以分为光口(SFP)和电口(RJ-45)。详细介绍可以参考以下链接:

SFP端口是什么?有什么作用?可以接RJ45吗?_audrey-luo的博客-CSDN博客

以太网通信离不开连接端口的支持,网络数据连接的端口就是以太网接口。以太网接口类型有RJ45接口,RJ11接口(电话线接口),SC光纤接口等。其中 RJ45 接口是我们现在最常见的网络设备接口(如:电脑网口)。

RJ45接口俗称“水晶头”,专业术语为RJ45连接器,由插头(接头、水晶头)和插座(母座)组成,属于双绞线以太网接口类型。RJ45插头只能沿固定方向插入,设有一个塑料弹片与 RJ45 插槽卡住以防止脱落。

RJ45 插头(左)、插座(右)

RJ45接口定义以及各引脚功能在不同通信速率下的定义有区别,在10M/100M通信速率下的定义,由下图可知,RJ45插座只使用了1、2、3、6这四根线,其中1、2这组负责传输数据(TX+、TX-),而3、6这组负责接收数据(RX+、RX-),另外四根线是备用的。

RJ45 插座 10M/100M 接口定义

而在1000M的通信速率下,RJ45插座的8根线都有用到,且都是双向引脚。需要说明的是,支持千兆网通信的RJ45接口是向下兼容的,即也支持10M/100M通信速率,只不过不同的通信速率,其引脚功能有区别。千兆网各引脚功能如下图所示:

RJ45 插座 1000M 接口定义

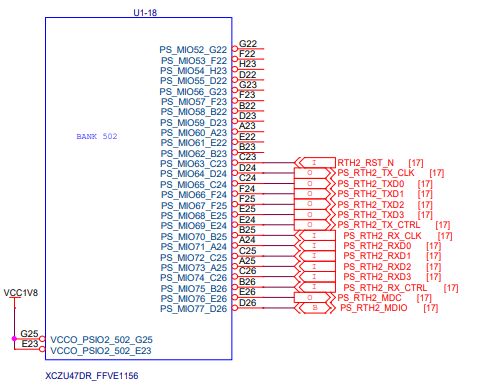

为大家贴上我在实现以太网通信时候实际的电路连接图,下图是zynq的ps端千兆网通信,与PHY芯片连接采用的是RGMII接口,pl端使用三速以太网ip Tri Mode Ethernet MAC时也是采用此接口(本次学习记录主要是对GT高速收发器的IP核学习,与下图无关):

这里只是对zynq ps端的以太网进行介绍。后续将详细介绍的是使用1G/2.5G Ethernet PCS/PMA or SGMII IP核进行千兆网通信,三速以太网Tri Mode Ethernet IP同zynq的ps端结构一样(很少用,用了再补充)。

上图MAC与PHY芯片采用的是RGMII接口,MAC侧的引脚图

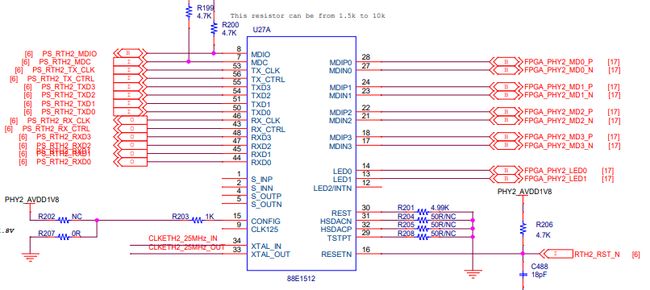

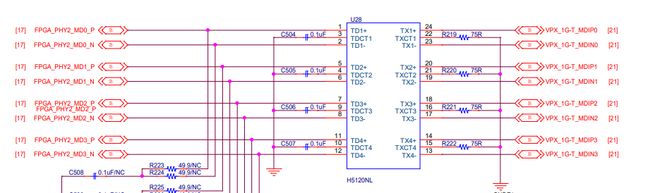

上图MAC与PHY芯片的引脚(左),PHY芯片与变压器的引脚(右)

上图PHY芯片与变压器的引脚(左),变压器与RJ-45的引脚(右)

四、千兆网协议帧(链路层MAC,编写FPGA代码时重点学习)

以太网 MAC 帧格式

以太网技术的正式标准是 IEEE 802.3,它规定了以太网传输数据的帧结构,我们可以把以太网 MAC 层理解成高速公路,我们必须遵循它的规则才能在上面通行,以太网MAC 层帧格式如图:

以太网传输数据时按照上面的顺序从头到尾依次被发送和接收,我们下面进一步解释各个区域。

前导码(Preamble):为了实现底层数据的正确阐述,物理层使用7个字节同步码(0 和1交替(55-55-55-55-55-55-55))实现数据的同步。

帧起始界定符(SFD,Start Frame Delimiter):使用1个字节的SFD(固定值为 0xd5)来表示一帧的开始,即后面紧跟着传输的就是以太网的帧头。

目的MAC地址:即接收端物理MAC地址,占用6个字节。MAC地址从应用上可分为单播地址、组播地址和广播地址。单播地址:第一个字节的最低位为0,比如00-00-00-11-11-11,一般用于标志唯一的设备;组播地址:第一个字节的最低位为1,比如01-00-00-11-11-11,一般用于标志同属一组的多个设备;广播地址:所有48bit全为1,即FF-FF-FF-FF-FF-FF,它用于标志同一网段中的所有设备。

源MAC地址:即发送端物理MAC地址,占用6个字节。

长度/类型:上图中的长度/类型具有两个意义,当这两个字节的值小于1536(十六进制为0x0600)时,代表该以太网中数据段的长度;如果这两个字节的值大于1536,则表示该以太网中的数据属于哪个上层协议,例如0x0800代表IP协议(网际协议)、0x0806代表ARP协议(地址解析协议)等。

数据:以太网中的数据段长度最小46个字节,最大1500个字节。最大值 1500 称为以太网的最大传输单元(MTU,Maximum Transmission Unit),之所以限制最大传输单元是因为在多个计算机的数据帧排队等待传输时,如果某个数据帧太大的话,那么其它数据帧等待的时间就会加长,导致体验变差,这就像一个十字路口的红绿灯,你可以让绿灯持续亮一小时,但是等红灯的人一定不愿意的。另外还要考虑网络I/O控制器缓存区资源以及网络最大的承载能力等因素,因此最大传输单元是由各种综合因素决定的。为了避免增加额外的配置,通常以太网的有效数据字段小于1500个字节。

帧检验序列(FCS,Frame Check Sequence):为了确保数据的正确传输,在数据的尾部加入了4个字节的循环冗余校验码(CRC校验)来检测数据是否传输错误。CRC数据校验从以太网帧头开始即不包含前导码和帧起始界定符。通用的CRC标准有CRC-8、CRC-16、CRC-32、CRC-CCIT,其中在网络通信系统中应用最广泛的是CRC-32标准。

在这里还有一个要注意的地方就是以太网相邻两帧之间的时间间隔,即帧间隙(IFG,Interpacket Gap)。帧间隙的时间就是网络设备和组件在接收一帧之后,需要短暂的时间来恢复并为接收下一帧做准备的时间,IFG的最小值是96 bit time,即在媒介中发送 96 位原始数据所需要的时间,在不同媒介中IFG的最小值是不一样的。不管10M/100M/1000M的以太网,两帧之间最少要有96bit time,IFG的最少间隔时间计算方法 如下:

10Mbit/s 最小时间为:96*100ns = 9600ns;

100Mbit/s 最小时间为:96*10ns = 960ns;

1000Mbit/s 最小时间为:96*1ns = 96ns。

在我们实际应用中,除了前导码,帧起始界定符被固定以外,目的地址,源地址,数据长度,数据都可以根据现实设计进行更改。

五、实际中以太网通信方式

交换机(Switch)意为“开关”是一种用于电(光)信号转发的网络设备。它可以为接入交换机的任意两个网络节点提供独享的电信号通路。最常见的交换机是以太网交换机。其他常见的还有电话语音交换机、光纤交换机等。

它是连接计算机、服务器、网络打印机、网络摄像头、IP电话等终端设备,并实现与其它交换机、无线接入点、路由器、网络防火墙等网络设备的互联,从而构建局域网络,实现所有设备之间的通信。简单来说就是设备之间通信的交通枢纽。

1、工作原理

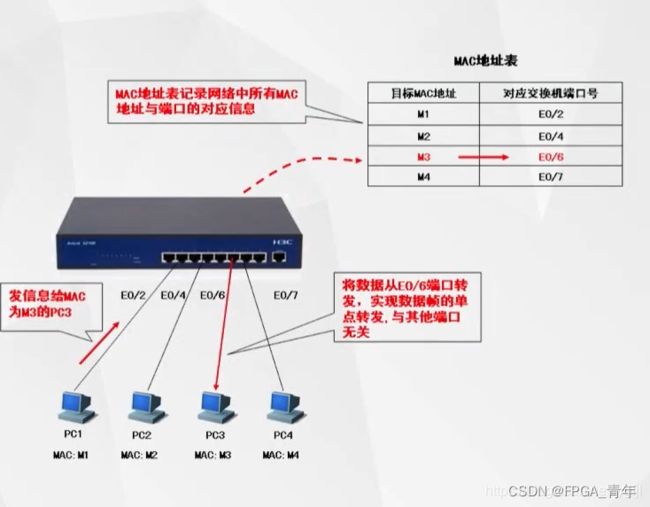

交换机是工作在数据链路层的设备。它的主要功能是MAC地址学习、通信过滤(数据帧单点转发)、避免回路功能;在每个交换机内部都维护有一张MAC地址表,用于记录交换机上每个端口所连接主机的MAC地址信息

交换机收到一个数据帧后,进行识别并根据帧的目的地址,将这个帧转发对应的某个端口上去,而不是广播到所有端口

2、MAC地址表

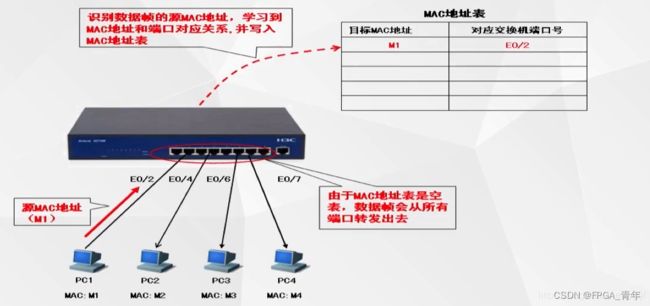

交换机具有MAC地址学习功能。交换机就是通过识别数据帧的源MAC地址,学习MAC地址和源端口的对应关系,主要过程如下:

1)当第一次使用交换机时,交换机MAC表为空,此时交换机会将源MAC地址与源端口建立交换映射,并将其写入交换机的MAC表;

2)将数据帧(含有目标MAC地址)从所有其他端口转发出去;

3)当接受者接受到数据帧并返回信息时,交换机便记住对应的MAC地址与端口的映射,并将其对应的关系写入MAC地址表中,以便下次转发;

之前测试设备时数据接口没有数据,然而千兆网链路已经建立成功,通过控制发送状态,多次发送,让交换卡熟悉地址后,才正常通信。

3、数据交换方式

1)建立MAC地址表与端口的映射:交换机监测发送到每个交换机端口的数据帧,通过数据帧中的源主机MAC地址、目的主机的MAC地址,在交换机中建立一张MAC地址表和端口的映射

2)判断广播帧和单播帧:当源数据帧中的MAC地址在MAC表中找到,需要判断是广播帧还是单播帧;如果为广播帧,则向所有端口(除接受该数据帧的端口外)转发数据帧;如果为单播帧,则查找已有MAC地址表,按照映射关系进行数据转发

关于局域网的知识,大家可以学习下CSDN中的网络技能树,科普一些知识挺好用的;

网络技能树 (csdn.net)

4、以太网通信方式

下面两张图是我目前所见过千兆网通信方式,也是我实际项目中测试遇到的,在这里作为学习记录。

上图可以对应文章第三部分最后的电路连接原理图,通常运用在ZYNQ的ps端以太网以及三速以太网(Tri Mode Ethernet MAC)IP时的实际连接方式;

下图是最近项目中连接的两种方式,采用的是1G/2.5G Ethernet PCS/PMA or SGMII IP核进行千兆网通信的实际连接方式(高速GT收发器)。

交换机:电源+风扇+n*交换卡+等等,是一个完整的系统(路由器)

交换卡:只是一个单独子卡,如下图所示,可以插进交换机中;

详细介绍可以参考一下

交换机基本介绍(分类、性能指标、硬件构成及工作方式)_交换机硬件组成_monologuezjp的博客-CSDN博客

以上内容是对以太网通信基础知识的学习,作为FPGA平台以太网学习的扩展知识,我们应关注的是MAC侧(FPGA)这一块知识,即文章中第四部分知识才是我们编写程序时候的要点。

下一节,将会做IP配置介绍。

记录美好学习,从总结开始;