第二章VHDL基本知识

2.1.1 空白符\b,\t

2.1.2注释符

单行注释://

多行注释:/* 8/

2.1.3标识符

字母,数字,符号,下划线,区分大小写,第一个字符必须是字母或者下划线

2.1.3转移标识符

以\开头,以空白结尾,

2.1.4关键字

用来VHDL内部使用的词叫关键字,所有的关键字都是小写

2.1.5数值

0 低电平,逻辑0或者假

1 高电平,逻辑1或者真

x 不确定的逻辑状态

z 高阻态

(2)整数及其表示

二进制 b 0,1,x,X,z,Z,?,_

八进制 o 0-7,x,X,z,Z,?,_

十进制 d 0-9,_

十六进制 h 0-9,a-f,A-F,x,X,z,A,?,_

8‘b10001101 //位宽为8位的二进制数

注意;数值不能为负,有符号放在最左边

’和b之间不允许出现空格

位宽不能是表达式形式

(3)实数及其表示

十进制表示法:小数点两边必须都要有数字,

科学计数法:564.2e2,3e-3=0.003

使用下划线可提高可读性,5_4582.2158_5896

2.2 数据类型

物理数据类型:连线型,寄存器型,存储器型,

1.连线型

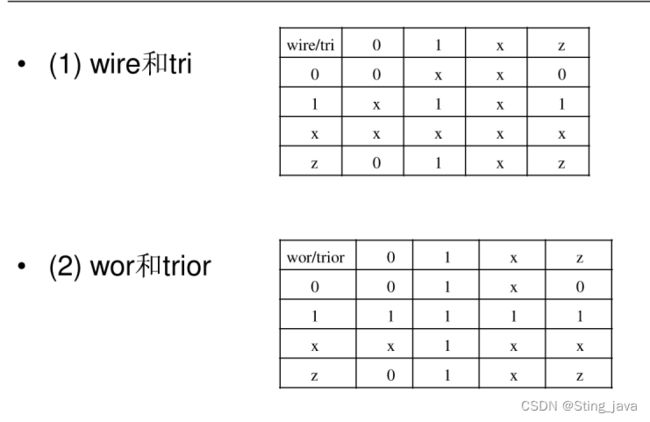

wire,tri 标准连线

wor,trior 多重驱动时,具有线或特性的连线型

wand,trand 多重驱动时,具有线与特性的连线型

trireg 具有电荷保持特性的连线型数据

tri 1 上拉电阻

tri 0 下拉电阻

supply1 电源线,用于对电源建模,为高电平1

supply0 电源线,用于对“地”建模,为低电平0

2.寄存器型

reg型状态保持作用,存储数据,触发器,锁存器

reg [3:0] b;

reg型变量一般为无符号数,若将一个负数赋值给reg型变量,自动转化为二进制补码形式。

2.2.2连线型和reg型数据类型的声明

连线型数据变量的声明

net_declaration 包括wire,tri,tri0,tri1,wand,triand,trior,wor

range数据类型为1位的标量,超过一位为矢量

delay 仿真延迟时间

list_of_variables变量名称,一次可定义多个名称,逗号隔开

drive-strength:连线变量的驱动强度

寄存器型数据类型的声明

reg

range为可选项,指定了reg型变量的位宽,缺省时为一位;

reg rega; //定义一个一位的寄存器型变量

reg [7:0] regb;// 8位的寄存器型变量

tri [7:0] tribus;//8位的三态总线

tri0[15:0] busa;//16位的连线型,处于三态时为上拉电阻

tri1[31:0] busb;//32位连线型,处于三态时为下拉电阻

reg scalared[1:4]b;//4位的标量型寄存器矢量

wire(pull1,strong0)c=a+b;//1和0的驱动强度不同的1位连线型变量c

trireg (large) storeline;//大强度的电荷存储功能的存储线

2.2.3存储器型

RAM\ROM\reg文件

一般声明格式为:

reg

range 1和range2都是可选项,缺省都为1;

range1存储器当中寄存器的位宽,格式为[msb:lsb]

range2寄存器个数,[msb:lsb],有msb-lsb+1个;

reg[7:0] mem1[255:0];//256个8位寄存器的存储器mem1;

reg [15:0]mem2[127:0],reg1,reg2;//128个16位寄存器的存储器mem2和两个16位 寄存器reg1,reg2;

reg[n-1:0]a;//n位寄存器a;

reg mem1[n-1:0];//n个1位寄存器构成的存储器mem1

2.2.4 抽象数据类型

整形,时间型;实型;参数型;

integer index;//32位有符号整数

integer i[31:0];//32个元素,整型数组

时间型

64位无符号数

time a,b;//两个64位时间型变量

实型

浮点型数值,对延迟时间的计算;

real stime;//定义了一个实数型数据

参数型

常量,仿真开始之前就被赋值,仿真过程中不变,提高程序可读性和维护性

parameter length=32,weight=16;

parameter PI=3.14,LOAD=4'b1101;

parameter DELAY = (BYTE+BIT)/2;

2.3运算符和表达式

2.3.1算术操作符

算术表带是的结果的长度由最长的操作数决定,再赋值语句下,算术操作数的长度由操作左端目标长度决定;

等于==;不等于!==;全等===;非全等!==

比较的结果有三种,0,1,x

2.3.4逻辑运算符

逻辑与运算符“&&”逻辑或运算符“||”逻辑非运算符“!”

按位运算符

按位取反~按位与&按位或|按位与或^按位同或^~

按位异或

参加运算的两个数,如果两个相应位为“异”(值不同),则该位结果为1,否则为0。

即 0 ^ 0=0 , 0 ^ 1= 1 , 1 ^ 0= 1 , 1 ^ 1= 0 。

2.3.6归约运算符

归约运算的过程是第一步先用操作数的第一位和第二位进行位操作,然后再用第一步的结果和操作的数的下一位

进行位操作,如此重复直到最后一位。

2.3.7移位操作符

<< >>

2.3.8条件运算符

<条件表达式>?<表达式1>:<表达式2>

一真大师

2.3.9 连接和复制运算符

连接运算符{}复制运算符{{}}

2.4模块的基本概念

模块的主要包括:模块的开始与结束,模块端口定义,模块数据类型说明,模块逻辑功能描述

(1)module开始endmodule结束,模块开始语句以分号结束

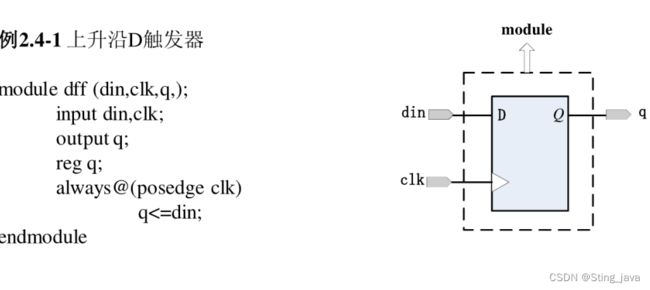

上升沿触发器

2.4.2端口

1.端口的定义

输入端口输出端口双向端口

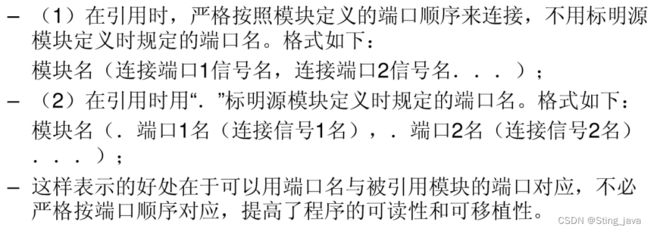

2.模块引用时端口的对应方式