【模拟CMOS集成电路设计】第九章 运算放大器

目录

9.1概述

9.1.1性能参数

9.2一级运放

9.2.1基本结构

9.2.2设计步骤

9.2.3线性缩放

9.2.4共源共栅运放

9.2.5设计步骤

9.3两级运放

9.3.1设计步骤

9.4增益的提高

9.4.1基本思想

9.4.2电路的实现

9.4.3频率响应

9.5性能比较

9.6输出摆幅计算

9.7共模反馈

9.7.1共模反馈知识

9.7.2共模检测技术

9.7.3共模反馈技术

9.7.4两级运放中的共模反馈

9.8输入范围限制

9.9转换速率

9.10高转换速率的运算放大器

9.10.1一级运放

9.10.2二级运放

9.11电源抑制

9.12运放的噪声

9.1概述

模拟的主要认为在两个方向:

(1)自然界的输入:关注噪声

(2)处理后的数据推动到天线输出:关注非线性

9.1.1性能参数

一、增益

决定精度;故设计时根据精度决定需要的增益。

二、带宽

单位增益带宽=![]() 决定速度;

决定速度;

主要是计算时间常数。

三、大信号特性

大信号带宽:大的阶跃时输出并不会指数变化,输出会先进行线性变化,再进行指数逼近。

四、输出摆幅

五、线性

六、噪声与失调

输入端等效噪声,输入端等效失调

七、电源抑制比

全差动可以解决

9.2一级运放

大信号特性关注点:

(1)输入共模范围

(2)输出摆幅

(3)输出直流点

(4)功耗

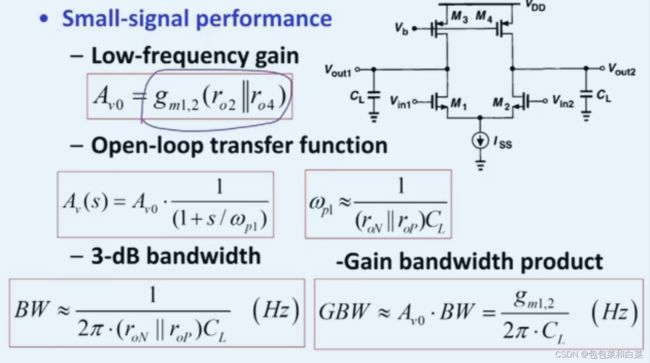

小信号特性关注点:

(1)低频增益:决定精度

(2)增益带宽积:决定速度(第二个极点在0dB以后)

(3)

9.2.1基本结构

一、5OTA

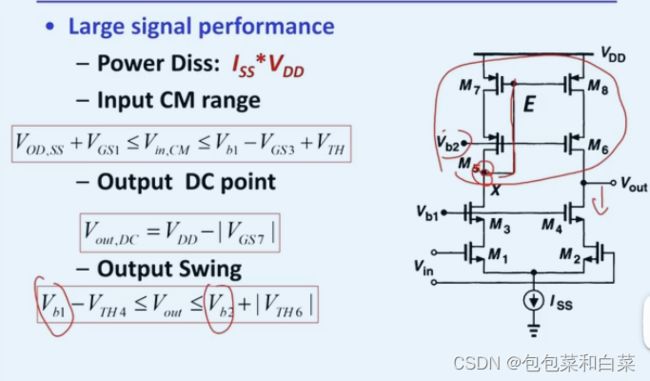

大信号特性

小信号特性

二、全差分

大信号特性

小信号特性

9.2.2设计步骤

(1)功耗——>![]()

(2)输出摆幅和输出工作点——>![]()

(3)![]() 和

和 ![]() ——>W / L

——>W / L

(4)![]() 和

和 ![]() ——>偏置电压和电流

——>偏置电压和电流

(5)验证增益

(6)设计迭代——>调制L(改变ro),且保证W/L不变(保持其他指标恒定)

注意点:在设计中![]() 和

和![]() 的确定需要以速率为依据,

的确定需要以速率为依据,![]() ,且有

,且有![]() ,

,

这个公式讲速率、功耗和摆幅联系在了一起。根据要求求 Id 和 Vod.

9.2.3线性缩放

W加倍造成的影响:

Id加倍、W/L加倍、Vod不变->电压摆幅不变、gm加倍、ro减半。

结论:宽度的线性缩放只会改变功耗(gm加倍,速度、GBW加倍。),增益和摆幅的数值不变。

9.2.4共源共栅运放

一、套筒式

摆幅:

低压版:上端增大一个Vth的摆幅

要满足单极点近似,需要![]() ,即保证第二个极点在单位增益点的右侧。

,即保证第二个极点在单位增益点的右侧。

二、全差分套筒式

有两个极点:一个小的极点是输出结点;另一个大的极点在串联的两个 nmos之间。

9.2.5设计步骤

(1)根据CL和GBW计算gm。(公式:![]() )

)

(2)确定 Id 和 Vod 。(根据 ![]() )

)

(3)根据Id和Vod计算W/L ,

(4)电流镜偏置Vb

增益调整:增大增益 ,增大调整ro(等比增大W和L) ,需要先观察是输出点上方电阻小了还是上方电阻小了,调节电阻小的一方,因为这样效果更显著。

三、cascode源随器的改进

不改进时输入输出摆幅很小;改进后增大。

四、折叠式共源共栅

输入摆幅增大了很大,特别是下方摆幅,甚至可以为负值。

输出范围扩大了一点(没有尾管了,范围下边扩大了)

增益比套筒式减小了;

主极点两者相同,次级点折叠式更小(结点处寄生电容更大)。

进一步增大增益

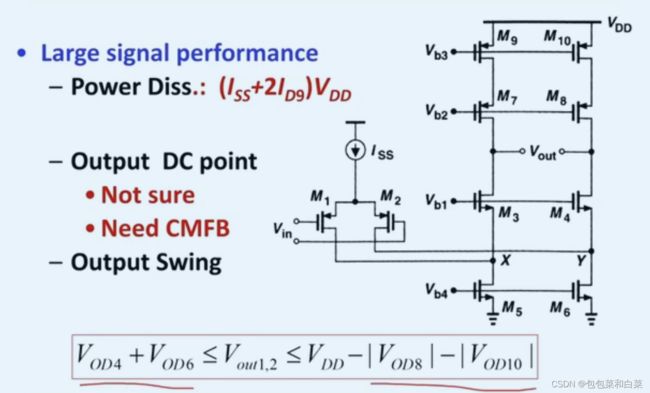

9.3两级运放

在单极中,即使有两个结点(极点),两个结点也一个是高阻结点,一个是低阻结点。两个极点距离远,易于单极点近似;在二级电路中,两个结点都是高阻的,两个极点距离近,不易单极点近似。

9.3.1设计步骤

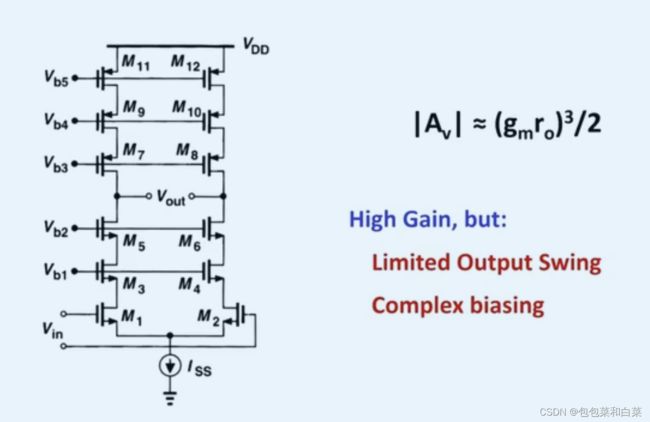

9.4增益的提高

9.4.1基本思想

一、电流负反馈制造大的输出电阻

9.4.2电路的实现

要想有大的输出摆幅,X点的电压需要等于Vod,但是这个电路还要保证M3在饱和区,故X点需提高电压,多消耗了一个Vth的电压余度。

改进:用pmos

左图中,M3的漏极电压最高位 V-Vod ,P点电压为 V-Vod-Vth ,漏极电压降低时,M2截至,即使不降低,M2也很容易截至,

故改进为右侧图,折叠式共源共栅,可以让输入与输出不相关,利于调节M2栅和源的电位。

电路:

9.4.3频率响应

增益提高技术后的电路:

![]()

增益提高,增益带宽积没变,增益提升是以带宽降低为代价的。

当辅助放大器的频率特性是全频(或极点很大),直接在主放大器频率特性的斜线顺延至增益更大的位置。如上图。

当辅助放大器极点小于GBW时,就会变得很复杂。

9.5性能比较

摆幅:两级有优势,增益提升没有优势;

速度:两级速度低,增益提升速度高;

功耗:增益提升技术功耗大(2倍)。

噪声:增益提高技术噪声大。

套筒式:

折叠式:

两级: 副极点低,频率特性图中增益下降快,GBW小,速度低。

增益提高技术:

9.6输出摆幅计算

9.7共模反馈

9.7.1共模反馈知识

(1)为什么要共模反馈?

两电流源冲突,使得输出端共模点很敏感,一点的波动就会导致输出端大的变化。

(2)三要素:检测、求差、反馈。

(3)简单分析反馈极性

9.7.2共模检测技术

9.7.3共模反馈技术

法一、

为不减小输出电阻,电阻需要很大,会占用很大面积。

法二、

共模检测的范围与主级输出的范围不匹配。

法三、

M7、M8都在线性区。输出Vout1,2 大时可能会饱和;

同样的问题:共模检测的范围与主级输出的范围不匹配。

法四、

开关电容共模负反馈:需要有时钟信号。

总结:一般常用的为电阻加电阻和开关电容。

9.7.4两级运放中的共模反馈

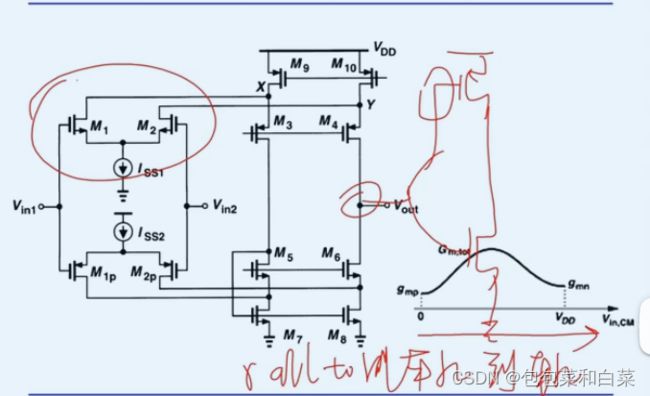

9.8输入范围限制

输入的范围上可达Vdd,下却受VGS的限制。换pmos输入的话,下可达gnd,上却受限制。

故做如下改进,扩大输入共模范围。

可以看出,跨导不恒定。

增大输出摆幅,可用class-AB

9.9转换速率

大信号速率:

输入给一个阶跃,当这个阶跃比较小时,随着输入阶跃的增大,输出斜率会随阶跃增大而增大,当阶跃大到某个值时,再大,输出斜率与不会变大了,输出会先线性,再指数逼近。

原因是:随着阶跃增大,Iss会分给左侧的变大,当Iss几乎全分给左侧时,输出斜率便不会再增大(线性充电)。这个临界的阶跃是![]() ,即Iss全部给左侧时的情况。当两侧的电压差小于

,即Iss全部给左侧时的情况。当两侧的电压差小于![]() 时,为指数充电。

时,为指数充电。