【Verilog】数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter)

- 数值

-

- 整数

- 实数

- 字符串

- 数据类型

-

- wire

- reg

- 存储器型

- 参数型

数值

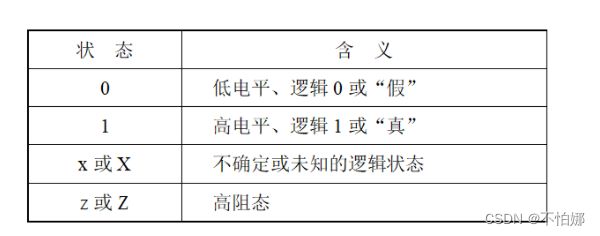

Verilog HDL有四种基本的逻辑数值状态,用数字或字符表达数字电路中传送的逻辑状态和存储信息。

-

x和z都不区分大小写,也就是说,0x1z与值0X1Z是等同的。

-

在数值中,下划线符号“_”除了不能放于数值的首位外,可以随意用在整型数与实型数中,它们对数值大小没有任何改变,只是为了提高可读性。例如,16’b1011000110001100和16’b1011_0001_1000_1100的数值大小是相同的,只是后一种的表达方式可读性更强。

整数

Verilog HDL中的整数可以是二进制(b或B)、八进制(o或O)、十进制(d或D)与十六进制(h或H)。

整数的表示形式为如下: +/- 其中,“+/-”是正数和负数标示;size指换算过后的二进制数的宽度;“ ’ ”为基数格式表示的固有字符,该字符不能缺省,否则为非法表示形式;base_format是其基数符号;number是可以使用的数字字符集,形式上是相应进制格式下的一串数值。

-

在较长的数之间可以用下划线来分开,目的是提高可读性,下划线本身没有意义,如16’b1110_1011_0011_1010,但下划线符号不能用作首字符。

-

当数字没有说明位宽时,默认为32位。

-

x或z在二进制中代表1位x或z,在八进制中代表3位x或z,在十六进制中代表4位x或z,其代表的宽度取决于所用的进制。例如:8’b1011xxxx 等价于8’hBx;8’b1001zzzz 等价于8’h9z

-

若没有定义一个整数的位宽,其宽度为相应值中定义的位数。例如:

'o642 //9位八进制数

'hBD //8位十六进制数

-

若定义的位宽比实际数的位数大,则在左边用0补齐。但如果数最左边一位为x或z,就相应地用x或z在左边补齐。例如:

10’b101 //左边补0,得0000000101

8’bz0x1 //左边补z,得zzzzz0x1

如果定义的位宽比实际数的位宽小,那么最左边的位被截断。

-

“ ? ”是高阻态z的另一种表示符号。在数字的表示中,字符“ ? ”和Z或z是等价的,可互相替代。例如:4’b??? 等价于4’bzzzz。

-

整数可以带正、负号,并且正、负号应写在最左边。负数表示为二进制的补码形式。例如:-4等价于4’b1100。

下面是一些合法的整数示例:

8’b10001101 //位宽为8位的二进制数10001101

8’ha6 //位宽为8位的十六进制数a6

4’b1x_01 //4位二进制数1x01

5’hx //5位十六进制数x (扩展的x),即xxxxx

实数

实数表示示例:

2.7 //十进制计数法

5.2e8 //科学计数法

3.5E-6 //科学计数法可用e或E表示,其结果相同

5_4582.2158_5896 //使用下划线提高可读性

字符串

字符串是指用双引号括起来的字符序列,它必须包含在同一行中,不能分行书写。若字符串用作Verilog HDL表达式或赋值语句中的操作数,则字符串被看做8位的ASCII值序列,即一个字符对应8位的ASCII值。例如"hello world"和"An example for Verilog HDL"是标准的字符串类型

数据类型

在Verilog HDL中,数据类型共有19种,分别是wire、tri、tri0、tri1、wand、triand、trireg、trior、wor、reg、large、small、scalared、medium、vectored、integer、time、real、parameter型。

按照抽象程度,Verilog HDL的数据类型又可划分为两大类:物理数据类型(主要包括连线型及寄存器型)和抽象数据类型(主要包括整型、时间型、实型及参数型)。

下面介绍常用的几个数据类型:

wire

wire是最常见的一种连线型,并且缺省为该类型。

连线表示逻辑单元的物理连接,可以对应为电路中的物理信号连线,这种变量类型不能保持电荷(除trireg之外)。连线型变量必须要有驱动源,一种是连接到一个门或者模块的输出端,另一种是用assign连续赋值语句对它进行赋值。若没有驱动源,将保持高阻态z。

reg

reg型变量是最常见也是最重要的寄存器型数据类型,它是数据储存单元的抽象类型,其对应的硬件电路元件具有状态保持作用,能够存储数据,如触发器、锁存器等。reg型变量常用于行为级描述中,由过程赋值语句对其进行赋值。

reg型数据与wire型数据的区别在于,reg型数据保持最后一次的赋值,而wire型数据需要有持续的驱动。一般情况下,reg型数据的默认初始值为不定值x,缺省时的位宽为1位。

reg型变量举例:

reg a; //定义一个1位的名为a的reg型变量

reg [3:0] b; //定义一个4位的名为b的reg型变量

reg[8:1]c,d,e; //定义三个名称分别为c、d、e的8位的reg型变量

在过程块内被赋值的每一个信号都必须定义成reg型,并且只能在always或initial过程块中赋值,大多数reg型信号常常是寄存器或触发器的输出。

存储器型

存储器型(memory)本质上还是寄存器型变量阵列,只是Verilog HDL语言中没有多维数组,所以就用reg型变量建立寄存器组(数组)来实现存储器的功能,也就是扩展的reg型数据地址范围。存储器型变量可以描述RAM型、ROM型存储器以及reg文件。数组中的每一个单元通过一个数组索引进行寻址。

存储器型变量的一般声明格式: reg 其中,range1和range2都是可选项,缺省时都为1。

- range1:表示存储器中寄存器的位宽,格式为[msb:lsb]。

- range2:表示寄存器的个数,格式为[msb:lsb],即有msb-lsb+1个。

- name_of_register:变量名称列表,一次可以定义多个名称,之间用逗号分开。

存储器型变量声明示例:

reg[7:0] mem1[255:0]; //定义了一个有256个8位寄存器的存储器mem1。地址范围是0到255

reg [15:0]mem2[127:0],reg1,reg2; //定义了一个具有128个16位寄存器的存储器mem2和2个16位的寄存器reg1和reg2

存储器型变量与寄存器型变量的比较:

reg[n-1:0] a; //表示一个n位的寄存器a

reg mem1[n-1:0]; //表示一个由n个1位寄存器构成的存储器mem1

- 一个n位的寄存器可以在一条赋值语句里进行赋值,而一个完整的存储器则不行。例如,对于上例可以进行“reg a = 0;”的赋值操作,而不能进行“mem1 = 0;”的赋值操作。 如果想对存储器中的存储单元进行读写操作,则必须指定该单元在存储器中的地址。比如mem1[2] = 0;

参数型

在Verilog HDL中,参数是一个非常重要的数据类型,属于常量,在仿真开始之前就被赋值,在仿真过程中保持不变。采用参数定义方法可以提高程序的可读性和维护性。参数常用来定义延迟时间和变量的位宽。

示例:

parameter length=32, weight=16; parameter PI=3.14, LOAD=4'b1101; parameter DELAY=(BYTE+BIT)/2;

另外,对于同一个模块来说,参数一旦被定义就不能够通过其它语句对它重新赋值。若要改变参量的值,可通过模块之间的参数传递来实现。