verilog数据选择器

1. 实验目的

(1)深入了解数据选择器原理

(2)学习使用Verilog HDL 设计实现数据选择器

2. 实验内容

(1)原理描述

数据选择器是一种多输入电路,单路输出的标准化逻辑构建。

选择器的的开关由两根控制线的编码控制,选择四路输入中的一路输出。

(2)Verilog HDL设计源代码描述(要求:注释)

//四选一选择器

module selector41(

//输入数据

input [3:0] iC0,

input [3:0] iC1,

input [3:0] iC2,

input [3:0] iC3,

//选择信号

input iS1,

input iS0,

//输出数据

output [3:0] oZ

);

assign oZ = iS1?(iS0 ? iC3:iC2):(iS0 ? iC1:iC0);

//当{iS1,iS0}=11 是输出 iC3;当{iS1,iS0}=10 是输出 iC2;当{iS1,iS0}=01 是输出 iC1;

//当{iS1,iS0}=00 是输出 iC0

endmodule说明:

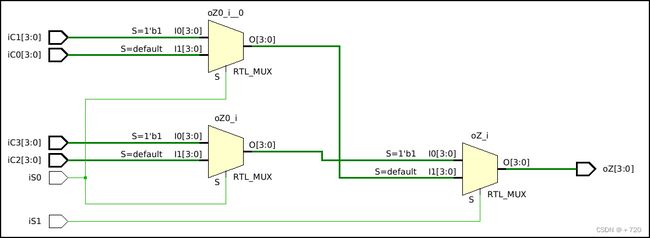

这是一个 Verilog 代码,用于实现 4-to-1 选择器。它有四个输入变量,iC0、iC1、iC2 和 iC3,以及两个输入选择信号 iS1 和 iS0。它还有一个输出变量 oZ。

选择器使用输入选择信号 iS1 和 iS0 选择哪个四个输入变量应传递到输出。如果 iS1 和 iS0 都是 1,则将 iC3 传递到输出。如果 iS1 是 1,而 iS0 是 0,则将 iC2 传递到输出。如果 iS1 是 0,而 iS0 是 1,则将 iC1 传递到输出。如果 iS1 和 iS0 都是 0,则将 iC0 传递到输出。

选择器使用 Verilog 代码中的赋值语句实现。赋值语句使用三元运算符(也称为条件运算符)来指定 oZ 的值,该值基于 iS1 和 iS0 的值。三元运算符具有以下语法:

条件 ? 值_如果_真 : 值_如果_假

在这种情况下,条件是 iS1?(iS0 ? iC3:iC2):(iS0 ? iC1:iC0),这意味着如果 iS1 为 1,则 oZ 的值将为 iS0 ? iC3:iC2,否则它将为 iS0 ? iC1:iC0。嵌套的三元运算符 iS0 ? iC3:iC2 在 iS0 为 1 时选择 iC3,在 iS0 为 0 时选择 iC2。类似地,嵌套的三元运算符 iS0 ? iC1:iC0 在 iS0 为 1 时选择 iC1,在 iS0 为 0 时选择 iC0。

这段代码的作用是根据输入的选择信号 iS1 和 iS0,从四个输入变量 iC0、iC1、iC2 和 iC3 中选择一个,并将其输出到 oZ。

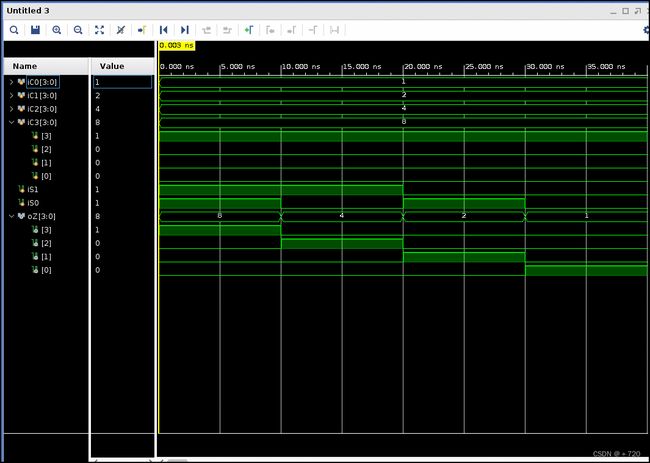

(3)TestBeach仿真代码及仿真结果

module test();

reg [3:0] iC0;

reg [3:0] iC1;

reg [3:0] iC2;

reg [3:0] iC3;

reg iS1;

reg iS0;

wire [3:0] oZ;

selector41 mux(

.iC0(iC0),

.iC1(iC1),

.iC2(iC2),

.iC3(iC3),

.iS1(iS1),

.iS0(iS0),

.oZ(oZ)

);

initial begin

iC0 = 4'b0001;

iC1 = 4'b0010;

iC2 = 4'b0100;

iC3 = 4'b1000;

iS1 = 1'b1;iS0 = 1'b1;

#10 iS1 = 1'b1;iS0 = 1'b0;

#10 iS1 = 1'b0;iS0 = 1'b1;

#10 iS1 = 1'b0;iS0 = 1'b0;

end

endmodulemodule test();

reg [3:0] iC0;

reg [3:0] iC1;

reg [3:0] iC2;

reg [3:0] iC3;

reg iS1;

reg iS0;

wire [3:0] oZ;

selector41 mux(

.iC0(iC0),

.iC1(iC1),

.iC2(iC2),

.iC3(iC3),

.iS1(iS1),

.iS0(iS0),

.oZ(oZ)

);

initial begin

iC0 = 4'b0001;

iC1 = 4'b0010;

iC2 = 4'b0100;

iC3 = 4'b1000;

iS1 = 1'b1;iS0 = 1'b1;

#10 iS1 = 1'b1;iS0 = 1'b0;

#10 iS1 = 1'b0;iS0 = 1'b1;

#10 iS1 = 1'b0;iS0 = 1'b0;

end

endmodule

(4)XDC文件配置

set_property PACKAGE_PIN R15 [get_ports {iC0[3]}]

set_property PACKAGE_PIN L16 [get_ports {iC0[1]}]

set_property PACKAGE_PIN M13 [get_ports {iC0[2]}]

set_property PACKAGE_PIN J15 [get_ports {iC0[0]}]

set_property PACKAGE_PIN R13 [get_ports {iC1[3]}]

set_property PACKAGE_PIN U18 [get_ports {iC1[2]}]

set_property PACKAGE_PIN T18 [get_ports {iC1[1]}]

set_property PACKAGE_PIN R17 [get_ports {iC1[0]}]

set_property PACKAGE_PIN T13 [get_ports {iC2[3]}]

set_property PACKAGE_PIN R16 [get_ports {iC2[2]}]

set_property PACKAGE_PIN U8 [get_ports {iC2[1]}]

set_property PACKAGE_PIN T8 [get_ports {iC2[0]}]

set_property PACKAGE_PIN V10 [get_ports {iC3[3]}]

set_property PACKAGE_PIN U11 [get_ports {iC3[2]}]

set_property PACKAGE_PIN U12 [get_ports {iC3[1]}]

set_property PACKAGE_PIN H6 [get_ports {iC3[0]}]

set_property PACKAGE_PIN M17 [get_ports iS0]

set_property PACKAGE_PIN N17 [get_ports iS1]

set_property PACKAGE_PIN N14 [get_ports {oZ[3]}]

set_property PACKAGE_PIN J13 [get_ports {oZ[2]}]

set_property PACKAGE_PIN K15 [get_ports {oZ[1]}]

set_property PACKAGE_PIN H17 [get_ports {oZ[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC0[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC0[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC0[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC0[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC1[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC1[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC1[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC1[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC2[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC2[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC2[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC2[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC3[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC3[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC3[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {iC3[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oZ[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oZ[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oZ[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {oZ[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports iS0]

set_property IOSTANDARD LVCMOS33 [get_ports iS1]

(5)下板测试