Stm32最小系统板电路图设计、PCB设计

目录

- 一、电路设计

-

- 1.复位电路

- 2.时钟电路

- 3.电源电路

- 4.SWD接口电路

- 5.BOOT启动电路

- 二、原理图绘制

-

- 1. 工程的建立

- 2. 原理图的绘制

-

- 2.1 使用已有库绘制原理图

- 2.2 构建原理图库

- 2.3 整体原理图

- 三、PCB绘制

-

- 3.1元件封装

-

- 3.1.1 元件封装的检测

- 3.1.2 元件封装的添加

- 3.1.3 封装库的建立

- 3.2 PCB设计

-

- 3.2.1 PCB设计前布局

- 3.2.2 PCB布局

- 3.2.3 PCB布线

- 3.2.4 PCB规则设计

- 3.2.5 PCB电气规则检查

- 3.2.6 滴泪以及铺铜操作

- 3.3 网络报表

-

- 3.3.1 网络报表的概念

- 3.3.2 网络报表的操作步骤

一、电路设计

1.复位电路

复位电路,就是指单片机芯片可以通过外部外部引脚输入复位电平信号,从而使单片机除备份区以外的所有寄存器都恢复为默认值,且芯片内烧录的程序会重新执行。对于STM32103C8T6芯片来说,其复位引脚是7号引脚,也就是NRST引脚。

通过复位电路对Stm32芯片系统进行的复位是外部复位,除此之外,Stm32芯片内部还有独立看门狗IWDG复位、窗口看门狗WWDG复位、软件SW复位和低功耗管理复位。独立看门狗和窗口看门狗就是一个递减计数器,当计数器的值减小到0的时候,系统就会进行复位。软件SW复位是通过程序在Stm32的一个寄存器的SW位赋值来控制复位。低功耗管理复位可以在待机或者停机状态下将Stm32的系统复位。除了复位电路的外部复位,其他复位模式并不需要自己设计,本文就仅设计了Stm32的外部复位电路,电路图如下。

此原理图由一个按键和一个电容并联后再和一个上拉电阻串联构成。上拉电阻一端接电源,另一端接电容和按键的并连结点,该结点接芯片的NRST引脚。芯片系统产生复位的条件是当NRST引脚的电压值低于某一值时就会产生复位,在本图中,按键没有按下时,NRST所接引脚的电压为电源电压,系统不会产生复位。当按键按下时,NRST对应引脚接地,芯片会产生复位。

2.时钟电路

Stm32芯片内部是由十分复杂的数字电路以及其他电路组成,需要稳定的时钟脉冲信号才能够保证其正常工作,通过Stm32的数据手册可知,Stm32芯片要想正常工作,其需要用到时钟的模块有很多。其分别是Contex-M3内核、闪存FLASH、可配置的静态存储器控制器FSMC、SDIO、内置SRAM、DMA直接数据存储、AHB总线、APB1总线及APB2总线。其中Contex-M3需要用到Contex自由运行时钟FCLK和Contex系统时钟SYSCLK。闪存FLASH、内置SRAM、DMA直接数据存储器和AHB总线则需要用到高速时钟HCLK。FSMC和SDIO也有其特有的时钟,分别为FSMCCLK和SDIOCLK。APB1和APB2也有其特有的时钟。由于芯片的内部集成化要求,不可能将每个模块都配置一个时钟源,因此芯片内部对已有的时钟源进行分频或者倍频操作,从而达到各个模块要求的时钟频率。

通过Stm32的数据手册得知,Stm32的芯片内部有三个时钟源,分别是HSI、LSI、PLL倍频器,除此之外还具备两个可以接外部时钟源的引脚,分别是OSCIN和OSC32IN。其中OSCIN引脚可以接4~16MHZ的晶体振荡器,在本设计中采用8MHZ的晶体振荡器。OSC32引脚通常接入32.768KHZ的晶振。本设计所采用的晶振都为石英晶振,因此外部晶振模块的抗干扰能力和精度相较于系统内部已有的晶振要提升很多,所以正常情况下,模块使用外部晶振。时钟电路的原理图设计如下。

电路原理图中,Y1为32.768KHZ的石英晶体振荡器,其两端分别通过匹配电容接地,其两端也分别接PC14和PC15,PC14在本设计中就是OSC32_IN引脚,PC15就是OSC32_OUT引脚。Y2为8MHZ的石英晶体振荡器,其和一个1M欧姆的电阻R9并联后分别接OSC_IN和OSC_OUT,并且通过两个匹配电容接地。匹配电容的作用是使晶振两端的等效电容等于或接近负载电容和滤除掉晶振波形中的高频杂波。R9是反馈电阻,其作用是保证非门工作在线性工作区,这样晶振会更容易起振。

3.电源电路

通过对Stm32数据手册的查阅可以得知,Stm32的芯片工作电压范围为2.0-3.6V。Stm32提供给模数转换电路的电压范围为2.4V-3.6V,在对模数转换没有较高精度要求的时候,其可以直接接到芯片的供电电源上,本文所设计的电源电路提供给Stm32芯片的电压值为3.3V。电源电路设计如图。

由于此最小系统板的设计采用USB供电,USB的直接供电电压是5V,因此需要设计出一个降压电路模块来将5V电压降到芯片所能够承受的3.3V。本设计在降压电路模块所采用的稳压芯片是RT9193。该稳压芯片具有输入端、参考噪声旁路端口、使能端、接地端和输出端五个引脚。电源电路原理图中输入端接USB提供的5V电压。BP端口接滤波电容。输出端口输出3.3V的稳定电压,输出电路部分接电容C3和C4,其作用为抑制自激振荡和稳定输出电压。

由于芯片中各个电路网络中电流变化时,各个电路模块之间会产生耦合现象,在电源电路模块中产生的耦合电流会对整个最小系统板的正常工作产生影响,因此可以设计一个退耦电容电路来消除各个电路模块之间产生的寄生耦合。本文所设计的退耦电路模块是在电路正极和地之间并联了4个退耦电容。退耦电路原理图如下。

4.SWD接口电路

Stm32的下载调试电路由JTAG下载电路、SWD下载电路,除此之外还可以通过串口下载和ISP下载。本设计SWD仿真调试下载。电路原理图部分只需要将芯片上的SWDIO和SWDCLK与SWD接口上的对应端口连接好即可,在本设计中芯片的SWDIO和SWDCLK非别为PA13和PA14引脚。在SWD端口的3.3V供电端口和接地端口接入一个电容,来达到抗干扰和滤波的作用。下载电路原理图如下所示。

5.BOOT启动电路

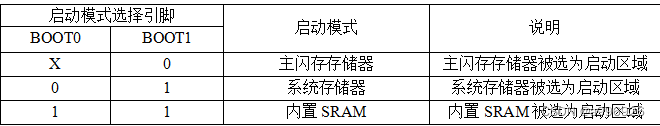

通过Stm32的用户手册可以得知,Stm32有三种启动状态,其由BOOT1和BOOT0引脚控制,BOOT0和BOOT1的值与启动模式之间的具体关系如下表所示。

在本设计中,BOOT0对应芯片的引脚为44号引脚,BOOT1对应引脚为20号引脚。本设计通过一个3*2的跳线针来作为主体,其1、2号引脚接3.3V电源,3、4号引脚分别通过一个电阻与BOOT0和BOOT1相连接,5、6号引脚接地。需要更改Stm32的启动模式时,只需要用跳线帽就可以达到更改BOOT0和BOOT1的值的目的,从而就可以更改启动模式。BOOT启动电路原理图如下。

二、原理图绘制

1. 工程的建立

点击左上角菜单栏中的文件,点击新的–>项目,建立一个完整的工程。此后建立的所有文件必须保证PCB和原理图必须保存在同一个项目下,否则在进行原理图转到PCB时会出现错误。成功建立的工程如下图所示。

2. 原理图的绘制

2.1 使用已有库绘制原理图

本设计的原理图库原理图库参考了部分嵌入式设计课程中所提供的STM32F108RCT6 MINI板的原理图,本设计选出了Stm32最小系统板需要用到的几个模块,从而完成了关于原理图部分的设计。正常的原理图绘制操作,需要提前下载好原理图库以及原理图库对应的封装库,在右侧的Compoents中可以选择自己需要用到的原理图库,并且可以添加自己需要的原理图库,以及从原理图库文件夹中查询元件。具体操作如下所示。

2.2 构建原理图库

本次设计中,原理图上用到的所有元件都来自于自行建立的库中,自行建造库的原因有两个。其一是通过对原理图库的构建可以提升查找芯片资料的能力和阅读芯片数据手册的能力。其二是因为stm32最小系统是一个很常用的芯片,其开发板用途很广泛,在后续竞赛项目中可能会用到。同时,建立起一个最小系统需要用到的所有元件的原理图库,也可以将资源共享,帮助其他人。综合以上两点因素,在本次设计中建立了一个完整地stm32最小系统板所需要用到的原理图库。

库的建立流程:点击左上角文件–>选择新建–>库–>原理图库。原理图库的建立最好也保存在本工程下,但并不强制,也可以将此库作为一个常用库,跟其他库放在同一文件夹下。在建立原理图库时,就是绘制出元件在电路图中的模样。在进行元件的绘制,添加引脚时,可以在右侧的Properties中对各个引脚的属性进行设置,这是在直接调用库中不容易被关注到的一个地方,建立库后库的形式和Properties的界面如下。

2.3 整体原理图

三、PCB绘制

3.1元件封装

3.1.1 元件封装的检测

元件封装检测方法有三种。方法一是点击原理图转到PCB时可以点击验证变更,如果没有错误,便表示封装都已添加完毕。方法二点击封装管理器,来对每一个元件的封装进行检测,在此也可以给没有封装的元件添加封装。方法三是依次的点击每个元件,然后在其Properties中来检验其是否有封装。

3.1.2 元件封装的添加

元件的封装添加步骤与原理图设计时元件的添加类似,可以直接在该工程中添加上封装库,但这种方法并不太可行,因为大多数元件的封装库并不清楚,因此来查找封装或者来构建专属于自己工程的封装库就显得很重要。

3.1.3 封装库的建立

建立封装库文件步骤是点击文件,点击新的,在此界面下点击库,最后点击PCB库即可。

构建一个元件的封装:在构建一个元件封装时,需要先去查询目标芯片芯片或者元件的尺寸大小。因为封装就是元件的实际尺寸,因此在构建封装时必须满足封装的大小要和目标元件的大小相对应。在查询完资料后,就可以来进行封装的建立。

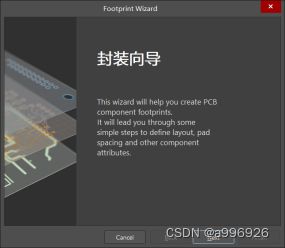

封装建立有自行建立和按照封装向导来建立两种类型,自行建立封装就是再添加完需要建立的封装后,双击即可,接下来便可以在封装界面对目标元件的封装进行规划设计,可以添加焊盘或者边框等操作,操作界面如下。

第二种方法就是按照向导来建立,把向导的步骤执行完,封装也就建立成功了。在添加封装栏,然后点击右键,选择Footprint Wizard即可进入封装向导界面。界面如下图所示。

3.2 PCB设计

3.2.1 PCB设计前布局

在进行PCB操作前,需要先绘制机械层的边界,板子后续的形状需要根据机械层的边界来裁剪,除此之外也要在keep-out层绘制出电气边界,这个边界可以来限制住自动布线时软件的操作,使板子的布线更加合理。

3.2.2 PCB布局

PCB的布局,这是一个十分吃经验的模块,大多数元器件都有很特殊的摆放位置,但是由于笔者专业水平还不够,在本设计中布局的时候还是仅仅停留在让飞线短一些,让布局看起来完美一些,让后期的布线不那么麻烦。本设计进行PCB布局的时候,是先对原理图中各个模块了解,了解各个元器件之间的连接关系,观察飞线,因此来尽可能的使自己的PCB布局更加合理。

在本设计中整体的布局思路是。首先,将Stm32的芯片放在板子的中心位置,方便与其他各个部分连接。其次是将晶振、电源模块等易受干扰或者受干扰后会对Stm32最小系统的工作产生较大影响的模块布局,本设计中晶振放在芯片周围。接下来,本设计将各个模块的元件尽量放在一块,让整体的布局更美观以及使板子更加合理。最后将有插口的元件放置在板子周围,以及贴片元件可以摆放在板子的底层。

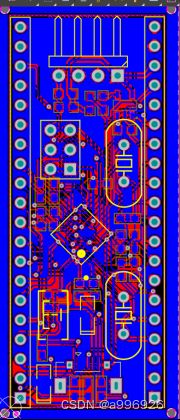

3.2.3 PCB布线

PCB布线有自动布线和手动布线两种方式。在手动布线时可以自行对各个模块,各个元件之间的线路进行布局,也可以打过孔或者放置焊盘,但是自动布线遇到原理图较难时就比较困难,总结下来还是经验不足,布局不够完美,布线经验也不够,这个需要后续多多的去进行项目的制作,去进行板子的布局和布线来总结经验。自动布线相较于手动布线就容易得多,但是在自动布线时要对不同网络的线宽要进行规则修改,这一点在后续规则检查时也尤为重要,规则修改会在下文会具体介绍。本设计的思路是布局的时候使飞线尽可能短,使最小系统板的各个模块尽可能地在一起,从而使布局看起来尽可能的美观合理。接着修改规则,按照修改后的布线规则进行自动布线,后续会对自动布线中需要修改的地方进行修改。本次设计完整的PCB如下。

3.2.4 PCB规则设计

在PCB规则设置界面可以对PCB的器件摆放、器件和线之间最小距离、线和线之间最小距离,封装引脚之间要求等等进行设置,PCB的规则设计很重要,后续的电器规则检查就是以设置的规则来进行检查的,在进行规则的设置时,要对电路知识有一定的了解,比如线和线离得过近可能会产生什么影响之类的要了解清楚。不能为了在进行电器规则检测时不报错,就肆意的修改规则,这也是一个需要去查阅去积累的过程,通过这次的的大作业,笔者也积累了一点关于这部分的知识。

规则设置操作步骤是点击菜单栏设计,然后点击规则,最后就可以选择需要更改的模块,新建规则或者修改已经有的规则。除了规则的建立,规则的优先级也十分重要。规则设置界面和规则建立界面如下。

3.2.5 PCB电气规则检查

点击工具,然后设计规则检查,通过设计规则检查可以根据建立的规则来检测自己的电路图中是否还有错误,检测过后可以得到如下界面。

3.2.6 滴泪以及铺铜操作

滴泪操作步骤是在PCB界面点击菜单栏工具,然后点击滴泪,接着就可以选择滴泪的网络又或者是选择所有导线都要进行滴泪,也可以选择滴泪的格式。界面如下。

铺铜操作步骤是在PCB界面点击菜单栏的放置,然后点击铺铜就可以进行铺铜操作了,分别选择顶层和底层来进行铺铜的操作就可以了,铺铜完成后设计效果如下。

3.3 网络报表

3.3.1 网络报表的概念

网络报表是对PCB个元器件之间电气连接的定义,在生成网络报表时,软件会根据元件、端口网络标号,导线来生成原理图所想要表述的电器连接,也可以说网络报表中涉及到了电路板的一切信息,其也可以称为原理图到PCB之间的桥梁。

在生成网络报表前需要先对原理图进行检测,简单来说就是编译一下。或者打开工程选项,在这里也可以对各种错误的报告类型进行设定,直到原理图编译无误后方可导出网络报表。网络报表中由()和[]两种符号,其含义分别为一个方括号[]里面的信息为一个元器件的信息,一个圆括号里面()里面的信息为一个网络的信息。

3.3.2 网络报表的操作步骤

网络报表生成步骤是在原理图界面下,点击设计,点击工程网络表或者文件的网络表,当该工程只有一个原理图文件时两者并无差异,点击Protel就可以生成目标对应的网络表,网络表以及工程选项界面图如下。