ARM体系架构

1. 计算机组成

交叉开发: 程序的编写 编译 在 PC机上(宿主机) 但 运行在 开发板(目标机)

嵌入式开的的特点:

开发环境的不同: 交叉开发环境

以应用为中心, 围绕实际功能设计 软件和硬件 量体裁衣

1.1 计算机的基本组成部分:

输入设备

输出设备

存储器

运算器

控制器

总线

计算机 X64(64位) x86(32位) stm32 8位(C51,STM8) 16位

1.2 控制器

CPU: 中央处理器 一般不能独立运行程序 只有寄存器 运算器 控制器 总线

MCU: 微控制器 可以独立运行程序 即 有CPU + RAM + ROM 构成

FPU: 硬件浮点运算单元 专门用于 进行浮点运算

GPU: 多个FPU + 多控制器构成 核心多 128 256

APU: (AI核心) 硬件神经网络

1.2.1 CPU中:

运算器: ALU 做运算 + - ...

控制器: 统筹整个系统的 工作, 仲裁

cpu运行程序逻辑:

CPU在时钟系统的 驱动下, 不断从ARM中 取出预先编译好的 程序指令 然后 执行

机器指令: 有汇编或其他高级语言编译 得到的 二进制指令 CPU只能识别这个

总线: 专门用于 CPU与各个设备间通信

单总线:

多总线:

1.3 存储器:

用于存储程序运行过程中的一些数据 缓存

金字塔结构 按照速度排序

寄存器 : 速度最快 成本最高的 存储器 通常以"个"计 在CPU中 相当于CPU的"手"

高速缓存: cache 速度 等同与CPU 成本高 通常以 KB或M计

内存(RAM): 内存条 运行内存 程序需要RAM(代码,数据段) 成本一般 G

外存(ROM): 硬盘 U盘 光盘 网盘

硬盘: 成本低 T

机械硬盘: 转速 5400 7200 硬盘接口: STAT(600m) M.2(固态) SCACS

固态硬盘: 使用FLASH 存储 读写有限次数 写操作要 复杂与写操作

通常 写入数据前 需要擦除 且 是按块擦除的

访问 读 通常也按块读取

负载均衡:

2. ARM知识点

2.1 ARM公司:

提出ARM架构 使用精简处理器指令集

整体上, ARM架构芯片 功耗低,成本低

嵌入式应用中,大部分CPU使用ARM架构

ARM架构: ARM公司开发的 一种CPU处理器结构

ARM CPU 架构发展和性能变化

ARM7

ARM9

...

cortex系列:

Cortex-A : 高性能型 多用于 多媒体 图形图像 UI

Cortex-R : 实时性能强 多用于汽车 运动控制等

Cortex-M : 低功耗或 低成本 场景 多作为单片机使用

stm32 - Cortex-M3

2.2 ARM生态链:

ARM公司: 做CPU架构设计 ARM 出解决方案的

芯片公司: 三星,华为,... 设计制造芯片

开发板设计公司: 做开发板 以及基本驱动程序

产品开发公司: 大量中小型嵌入式企业

使用开发板或自己设计硬件开发板 做 应用

软件层面:

Linux系统: 开源免费 GPL协议

智能手机: 嵌入式崛起 安卓系统

2.3 ARM环境搭建:

使用KEIL 调试功能,模拟ARMCPU运行情况

1. 安装交叉编译工具 即编译器

该编译器在 Windows下运行 但编译的程序在ARM架构下运行

2.4 armCPU寄存器:

是cpu留给程序的接口 类似于人的双手

2.4.1 CPU中 主要的寄存器

R0—R12 13个通用寄存器 没有专用的特定功能

R13 sp 栈指针寄存器 专用于存储程序栈指针

R14 lr 链接寄存器 用于程序跳转返回的实现

R15 pc 程序计数器 用于存储下一条将要执行的指令的地址(取址的指令的地址) ,修改该寄存器中的值 ,即实现程序跳转

CPSR: 程序状态寄存器 用于存储程序状态(ZNCV位 ...)

nzcv为: 符号位 存储计算过程中的一些特定情况

模式位: [4:0] 存储CPU的模式 修改模式位 可以主动让CPU进入指定模式

SPSR: 程序状态备份寄存器

3. CPU的状态和模式

3.1 CPU状态:

ARM状态: 在该状态下 运行ARM指令 4字节对齐 运行速度快 指令更耗费空间

thumb状态: 在该状态下 运行thumb指令 2字节对齐 指令密度更高 运行效率会有所降低

3.2 CPU模式:

目的

1 为了安全

2 为了处理异常

3.2.1 7中模式

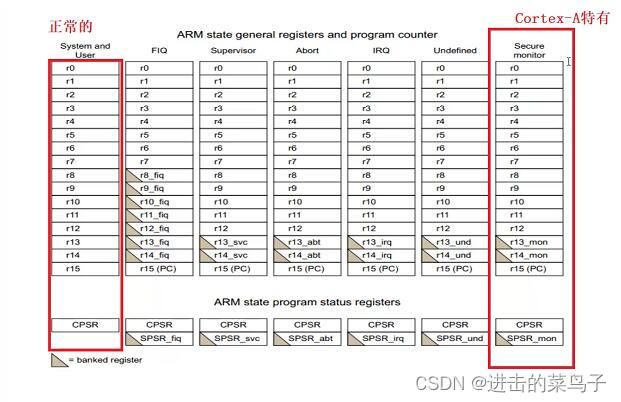

ARMCPU 提供了 7种模式 每一种模式 都有 R0-R15 CPSR SPSR(usr,sys模式没有)

usr sys abort svc irq fiq undef

用户模式 系统 终止 管理员 中断 快速中断 未定义

模式位 10000 11111 10111 10011 10010 10001 11011

寄存器个数 17个 0 3 3 3 8 3 sys因为和usr公用所以没有独立的寄存器,后面从abort开始写的寄存器个数是每个模式下独有的寄存器个数

ARMcpu 一共有 37 个寄存器 有7中模式 通常

3.2.2 模式的细分

非特权模式 : usr

特权模式(可以主动修改cpsr): ( 除usr模式外) sys abort svc irq fiq undef

非异常模式: sys

异常模式 : (除sys和usr外) 指在CPU发生异常情况时 会主动进入的模式

3.2.3 ARM寄存器组织

这里注意sys和usr两种模式公用一套寄存器且没有SPSR(因为他俩都成为正常模式(因为usr为非特权模式和sys为非异常模式),只有不正常才需要SPSR)

注意每种模式的栈区不是在一起的

4. 什么叫异常?

CPU中的异常是指,CPU遇到的一些特定情况 将这些特定情况 统称为异常

4.1 ARMCPU有哪些异常?

复位异常: 复位键被点击了 产生了复位信号 CPU将 自动进入svc模式

未定义指令异常: CPU从内存中得到了一条不识别的指令 undef 用于扩展指令

软中断异常 : 触发了软中断 svc 用于实现系统调用

指令预取异常: CPU从内存中取一条指令失败了 abort 用于虚拟内存的刷新

数据异常 : a/0 (比如除数为零) abort 处理非法运算

中断异常 : 触发了中断 irq 处理中断事件

快速中断异常 触发了快速中断 fiq 处理快速中断事件

4.2 异常处理流程:

硬件处理和软件处理

4.2.1 硬件处理:

由CPU在触发异常时 自动完成的动作

1. 备份 CPSR 到对应模式的 SPSR ,为了恢复程序状态做准备

2. 备份 PC到LR ,为了处理完毕异常后 可以返回到异常打断处理继续

3. 修改 CPSR

1) 设置CPU 为ARM状态 因为异常的处理 都是ARM指令

2) 设置CPSR 中模式位 为异常模式

3) 若有必要 禁止某些中断(f/i) 例如 fiq触发时 irq中断位设置为1 屏蔽

4. 设置PC 到对应异常向量的入口 即程序入口(软件处理)

4.2.2 软件处理:

由编程者解决具体的问题

1. 保存现场 公用寄存器入栈 r0-r12, lr

2. 处理异常

3. 恢复现场 从栈中取出 R0-R12, lr--> PC , 从 SPSR中 恢复CPSR

4.3 异常向量的入口?

由CPU 规定的 对应异常的处理程序的入口 地址

入口:

0x00 复位异常: 复位键被点击了 产生了复位信号 CPU将 自动进入svc模式

0x04 未定义指令异常: CPU从内存中得到了一条不识别的指令 undef 用于扩展指令

0x08 软中断异常 : 触发了软中断 svc 用于实现系统调用

0x0c 指令预取异常: CPU从内存中取一条指令失败了 abort 用于虚拟内存的刷新

0x10 数据异常 : a/0 abort 处理非法运算

0x14 保留 为了后续可以 扩展异常

0x18 中断异常 : 触发了中断 irq 处理中断事件

0x1c 快速中断异常 触发了快速中断 fiq 处理快速中断事件

4.4 异常的优先级问题?

1. reset 复位异常

2. Data ABort

3. FIQ

4. IRQ

5. Prefetch Abort

6. SWI 软中断

7. Undefined instruction

5. 中断

中断: 指事件(中断源) 打断CPU当前正在 执行的程序, 转而去 处理中断事件 处理完毕后,回到打断位置 继续向后执行

中断源: 系统中能够产生中断信号的来源

外部中断: 中断信号来自芯片外部 通过GPIO 传入的

内部中断: 芯片内部的一些设备 产生的 timer uart wdt ....

5.1 问 快速中断为何比中断快 ,快在什么地方

fiq 快速中断 irq 中断

1.fiq 优先级高于irq

2.fiq 独立寄存器多 保存现场 与 恢复现场 快

3.fiq 位于异常向量表 末尾, 可以不必要跳转 直接开始处理

6. 流水线

目的 提高指令执行的效率

一条ARM指令的执行 主要有3个步骤

取址: 从内存中 加载 指令到 CPU

译码: 解锁执行需要的寄存器

执行: 指令执行对应操作

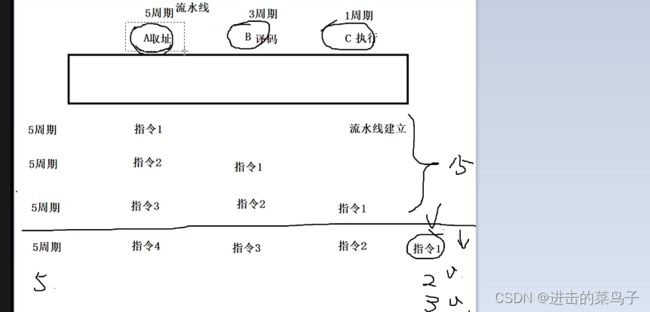

多级流水线: 3级 5级 9级 11级

指令执行的周期 并非一致 多周期指令 将 阻塞流水线

流水线的打断 ----->例如 执行了 跳转指令 异常触发了

6.1 举例

6.1.2 使用3级流水线

不使用流水线

假设 取址 5周期 译码 3周期 执行 1周期 ,执行一条指令 9周期

有100条执行 需要顺序执行 900周期

3级流水线

若为3级流水线 问 100条指令 需要多少周期可以完成?

515个周期

解释

由上图可知,载第4个5周期结束后,我们的指令1刚好全部执行完毕

那么可以推断出,在下一个5周期执行完毕后,指令2也执行完毕,再下一个5周期执行完毕后,指令3执行完成,由此可以得出再第4个5周期后,每5个周期都会有一个指令执行完毕,所以100条指令需要500周期,但是前面还有3个5周期(称之为流水线的建立周期)要计算,总共515周期

7. ARM指令集

RISC:精简指令集处理器 追求的是 结构的简化 功耗的降低 ,指令长度是固定 舍弃了一些复杂指令 转而由多个简单指令取完成复杂指令的工作,嵌入式应用场合, 低功耗, 对成本敏感的 场景

CISC (x86 架构):复杂指令集处理器 追求的是 运行效率 ,指令集长度不固定 所有指令都追求硬件实现 结构复杂 功耗高