PCB布局布线小建议(1)

编者荐语:

亲爱的读者,你是否对PCB设计感兴趣?这篇文章是在 EEWorld 看到的, 是由 XuTong 撰写的,文章介绍了PCB布局布线的小技巧,既简单又实用,无论你是PCB设计的初学者还是爱好者,都可以从中受益匪浅。快来阅读这篇文章吧!

以下文章来源于xuyuntong ,作者XuTong

xuyuntong.

想学电路吗?来吧!

画好电路原理图只能代表逻辑没有问题,但是真的就没有问题吗?

不好的布线就会引起很多诡异的问题,最好从一开始就做好布局布线省去很多Debug时间。

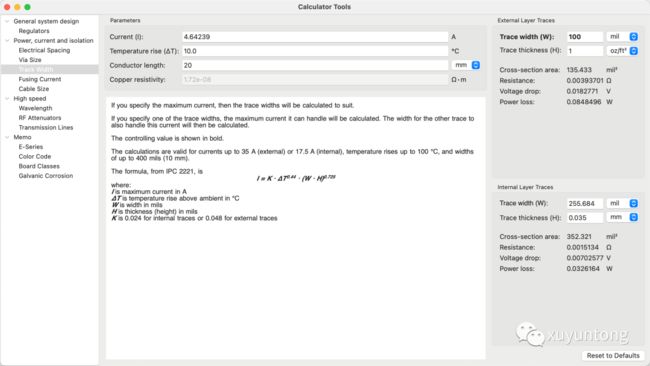

首先需要关注的是线宽,多少线宽对应多大电流,通常来说在1oz的情况下,100mil的线宽可以走4.6A的电流,通常有现成的电流计算软件可以完成计算工作,如图1所示

图1:qorvo电流计算网页

电流计算网址:https://www.qorvo.com/design-hub/design-tools/interactive/pcb-trace-power-handling-calculator

Kicad软件内也包含现成的电流计算,如图2所示

图2:Kicad PCB calculator tools

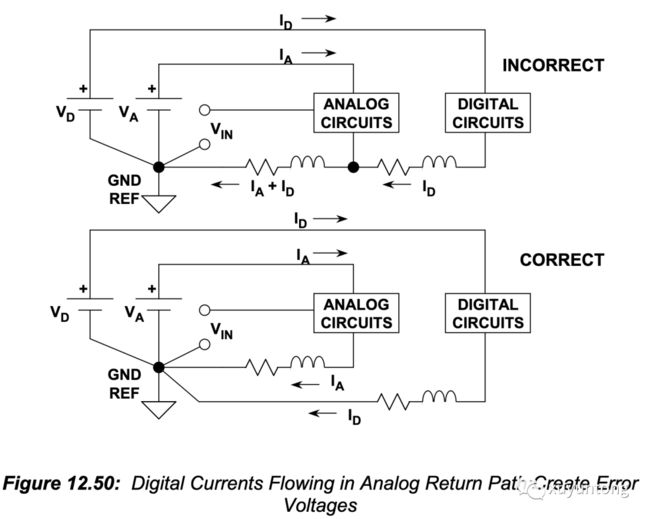

清楚电流和线宽的关系后,还需要知道这根线的类型,到底是变化缓慢的模拟信号,还是快速变化的数字信号,还是用于过大电流的功率信号。

通常来说分为以上3种类型,不同类型需要不同的GND回路,通常在连接器处共地,以保证信号线不被相互干扰,要知道GND并非理想,地上面通常包含阻抗和电感,当接地器件电流快速变化时候,GND上面可能会产生压降,从而导致器件损毁,在不那么恶劣的情况下,GND只是电阻可能会引起模拟信号的精度下降。

通常较为理想的接地为星型接地,如下图3参考所示(参考basic linear design 第12章)

图3:典型的星型接地

很多情况下,我们只能使用两层板布线,地不可避免的分割,所以为了有一个完整的地平面,通常只在顶层布线使用尽可能短的跳线,以保证底层地的完整。如果是四层板那我们的选择会多一些,通常四层板的可以在信号相近层做地平面,通常4层板堆叠为以下:1信号,2接地,3信号,4接地。参考文档(High Speed Analog Design and Application Seminar)

另外退藕电容的设置也尤为关键,首先要确保退藕电容和被滤波的芯片在同一个层上,避免由于通孔引起的电感,要让电源和地先进退藕电容在进芯片,保证退藕电容的有效性。可以参考图4:退藕电容布置

图4:退藕电容布置

在开关电源电路中,应该保证最小的di/dt dv/dt 的loop,如下图5,图6所示。参考(Improve High-Current DC/DC Regulator EMI Performance for Free With Optimized Power Stage Layout)

图5: 同步buck PCB布局

图6:横向开关loop设计

同时需要注意的是,如果使用的电解电容,应该让电解电容和发热器件保持一定的距离以保证电解电容可以有更长的使用寿命。

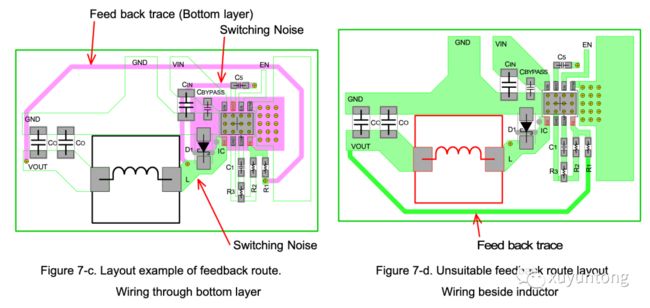

另外采样线也应该远离high di/dt dv/dt的loop,举个例子如图7所示,左边为较为合适的布局,远离电感,并且R1和R2的位置是反馈点,要注意的是,先从输出端拉出反馈线,在离输入端比较近的位置在去放置反馈电阻。参考:PCB Layout Techniques of Buck Converter Rohm

图7:反馈线布线例子

另外在使用拐角的导线时候尽量使用尽可能大的拐角角度,拐角角度越大线阻抗变化率越小,以下给出好的拐角导线和不好的拐角导线例子。如图8所示:

图8:拐角导线

使用带热焊盘的器件时候,要尽可能多的在热焊盘下面放置过孔,让其热传导更加好一些,如下图9所示不同via放置对热阻的影响。参考文档PCB Layout Thermal Design Guide

图9:不同via数对热阻的影响

小建议(1)先到这吧,想到在更新。

参考文档:

Basic linear circuit design

PCB Layout Techniques of Buck Converter Rohm

PCB Layout Thermal Design Guide

Improve High-Current DC/DC Regulator EMI Performance for Free With Optimized Power Stage Layout

Qorvo 网页