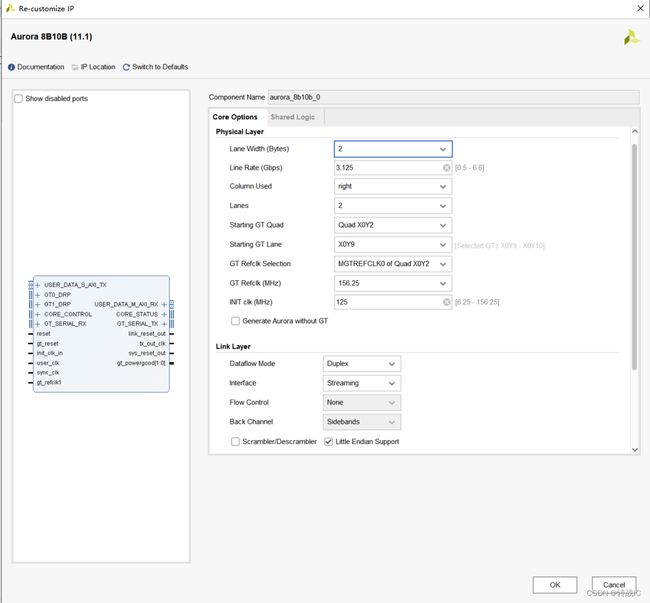

2.aurora 8b10b ip核说明

1.ip配置

因为图中很多信号都是用的总线接口,这里我们从核里的顶层文件来看每个信号的使用

2.核中顶层文件接口信号展示

module aurora_8b10b_0

(

input [31:0] s_axi_tx_tdata,

input s_axi_tx_tvalid,

output s_axi_tx_tready,

output [31:0] m_axi_rx_tdata,

output m_axi_rx_tvalid,

// GT Serial I/O

input [0:1] rxp,

input [0:1] rxn,

output [0:1] txp,

output [0:1] txn,

// GT Reference Clock Interface

input gt_refclk1,

// Error Detection Interface

output hard_err,

output soft_err,

// Status

output [0:1] lane_up,

output channel_up,

// System Interface

input user_clk,

input sync_clk,

input gt_reset,

input reset,

output sys_reset_out,

input power_down,

input [2:0] loopback,

output tx_lock,

input init_clk_in,

output tx_resetdone_out,

output rx_resetdone_out,

output link_reset_out,

//DRP Ports

input [8:0] gt0_drpaddr,

input [15:0] gt0_drpdi,

output [15:0] gt0_drpdo,

input gt0_drpen,

output gt0_drprdy,

input gt0_drpwe,

input [8:0] gt1_drpaddr,

input [15:0] gt1_drpdi,

output [15:0] gt1_drpdo,

input gt1_drpen,

output gt1_drprdy,

input gt1_drpwe,

output [1 : 0 ] gt_powergood,

output tx_out_clk,

output bufg_gt_clr_out,

input pll_not_locked

);

2.1.复位信号

1.reset:Aurora 8B10B IP的复位信号,高有效,如果要复位,至少保持6个时钟周期的高电平

2.gt_reset:GT接口的复位信号,高有效,至少保持6个时钟周期的高电平,注意如果gt在复位过程中,user_clk会停止产生一段时间,因为user_clk是从GT的txoutclk产生的

注意:在上电复位过程中,保持reset、gt_reset为高,且gt_refclk、init_clk_in稳定,即可完成上电复位。

3.link_reset_out:热插拔复位信号,如果热插拔计数器计数超过了期望值(说明此时没有接收通道),则拉高该复位信号,同时这个信号也会输入给gt核的热插拔复位管脚(注意gt核的热插播复位管脚只有在aurora模块有,前一讲单单的gt核没有该输入信号)

(aurora核中的热插拔逻辑:Aurora 8B/10B中的热插拔逻辑(使用自由运行的init_clk信号)是基于接收到的时钟补偿字符。通过Aurora RX接口接收时钟补偿字符意味着通信信道是活动的,而没有中断。如果在预定的时间内没有接收到时钟补偿字符,则热插拔逻辑将重置核心和收发器。)

(每个通道都有一个link_reset_out信号,如果我们使能两个通道,ip核就会把这两个通道的link_reset_out或一下,然后再输出给t核的热插拔复位管脚)

4.sys_reset_out:输出去除抖动的sys_reset_out

2.2.时钟信号

1.user_clk:在aurora的示例工程aurora_module_i中,该信号由gt核中的txoutclk经过BUFG驱动,作为输入进入aurora核,在aurora核中user_clk连接到了GT核的txuserclk2和rxuserclk2(即txuserclk2和rxuserclk2用的是同一个时钟,由tx_out_clk产生),user_clk同时在aurora_module_i示例工程中作为输出,供用户使用

2. sync_clk:在aurora的示例工程aurora_module_i中,该信号由gt核中的txoutclk经过BUFG驱动,作为输入进入aurora核,在aurora核中sync_clk连接到了GT核的txuserclk和rxuserclk。

3. gt_refclk:GT参考时钟,在aurora的示例工程aurora_module_i中由板子上输入的差分时钟对经过IBUFDS_GTE驱动

4.tx_out_clk:GT核为用户提供的TX端时钟

5.init_clk_in: 用于GT核核aurora核初始化和复位操作的时钟,因为在复位完成前user_clk并没有输出。频率范围推荐低于GT参考频率。

2.3.状态信号

1.hard_err 、soft_err信号:hard_err检测buffer溢出、锁相环失锁,soft_err检测内部数据流是否出现错误

2.channel_up:当Aurora 8B/10B通道初始化完成且该通道已准备好进行数据传输时拉高。

3.lane_up:当Aurora 8B/10B通道初始化完成且该通道已准备好进行数据传输时拉高。(只有将channel_up和lane_up两个信号拉高之后,我们才可以进行进一步的操作。)

(channel和lane有什么区别嘛:channel是片中的通信总线,同时也是一种抽象的概念,它是芯片中连接多个子系统的桥梁,可以实现信息的传输和交互。lane是指芯片中的逻辑信道,它是channel的一种物理实现,主要用于传输信号和数据。)

4.rx_resetdone_out/ tx_resetdone_out:gt核中rx/tx复位完成信号

5.bufg_gt_clr_out:这个信号代表gt核中的tx通道初始化已经完成,因为在auraoip核的示例工程aurora_8b10b_0_support中,会用txourclk生成user_clk_i和sync_clk_i,那么bufg_gt_clr_out信号就被当作复位信号,因为如果tx通道没有初始化完成,我们无法用txourclk生成user_clk_i和sync_clk_i

assign gtwiz_userclk_tx_reset_int = !(>_txpmaresetdone_int);

assign bufg_gt_clr_out = gtwiz_userclk_tx_reset_int;

6.tx_lock:拉高表示传入的串行收发器的参考时钟已被收发器锁相环(PLL)锁定。我的理解是因为参考时钟输入cpll或者pll之后,输出的频率稳定之后,会有一个locked输出信号,即tx_lock,该信号拉高,说明此时cpll或者qpll输出的时钟已经稳定

2.4.控制信号

1.power_down:输入信号,控制收发器电源,为低时电源打开,收发器工作

2.loopback[2:0]:环回模式,包括PCS、PMA的近端环回、远端环回,以及不使用环回调试的正常模式。(一般情况给000即可)

3.pll_not_locked:输入信号,如果使用PLL为Aurora 8B/10B核心生成时钟,则pll_not_locked信号应该连接到PLL的锁定信号的取反。如果PLL不用于为Aurora 8B/10B核心生成时钟信号,则将pll_not_locked连接到地面。

注意:检查设计过程中的pll_not_locked信号。如果它是高电平,aurora是无法初始化。

2.5.drp相关信号

DRP信号接口并未使用,均初始化为0

注意:这里drp接口信号没有引出drp的时钟信号DRPCLK_IN,ip核里之间把这个信号连接到了init_clk

2.6.用户数据接口信号

1.s_axi_tx_tdata、s_axi_tx_tvalid、s_axi_tx_tready:这是发送数据的相关信号,使用AXI_stream协议

2.m_axi_rx_tdata、m_axi_rx_tvalid信号:这是接收数据的相关信号,使用AXI_stream协议

(为什么没有m_axi_rx_tready信号,文档里进行了说明

)

2.7gt核数据发送端口

1.txp、txn信号:GTP的写差分接口,也就是我们绑引脚的接口。但是不用我们在约束文件中绑定管脚,gt核自己帮我们做了

2.rxp、rxn信号: GTP的读差分接口,也是我们绑引脚的接口。但是不用我们在约束文件中绑定管脚,gt核自己帮我们做了