Verilog HDL语法学习心得

从五月中旬开始进入到Verilog HDL语法学习、项目实战阶段,满打满算已经两个月时间了。这两个月全部在自习室度过,一直没有认真做一篇总结,主要还是抽不出时间来,因为几乎每天都有需要琢磨研究的东西。今天得空写一篇总结,一是告慰自己,二是希望能为后来学习者提供一些借鉴,尽量少走一些弯路。

从零基础开始,到现在一看到编译报错信息就可以判断出是什么类型的错误、怎么解决以及可以帮助别人解决一些简单的问题。这背后的辛酸也只有自己能体会到。

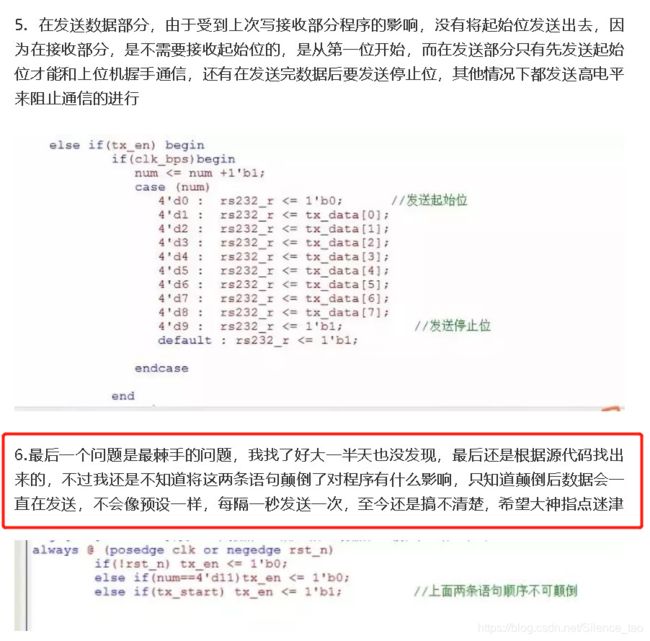

上图是我解答某公众号文章《工程师深度:FPGA高手养成记》中提出的一个问题。其实我并没有看到完整代码,但是凭借上下两段简短的截取代码,再依据自身的经验,就清楚了设计者想要完成的功能以及代码中的逻辑错误。(文章链接:https://mp.weixin.qq.com/s/6dOTmlVnI6zONbFkGuTPaQ)

提这个并没有标榜自己的意思,我也只是一个初学者,想表达的是,从零基础到这个水平,两个月时间,你也可以!

一、雾里看花 邯郸学步

初见Verilog语言,一头雾水,不知所言。与其坐以待毙,不如邯郸学步。刚开始的水平就是照着老师的代码一个一个敲,都会编译出错。可能这里少了“end”,那里用了中文字符,这里打错了某个字母,那里少了某个变量、关键字……诸如此类的低级语法错误,很多很多。那会儿还没有总结出一条比较成熟的debug路线,就是求助同学、老师,被别人点醒后,恍然大悟,这是零基础玩家必须要经过的一个阶段。

二、筋骨不全 跃跃欲试

克服了低级语法错误这个问题,即将进入第二阶段。这个篇幅的长度也对应零基础学习者在这个阶段所要持续的时间以及痛苦程度.......

一遍一遍的边抄边体会一些简单项目的课程代码,交通灯,流水灯,按键消抖,数码管显示等,体会代码背后所描述的功能、每一段代码的意义、每一个关键字的用法。渐渐地,我开始在摸清了老师的思路之后,尝试着自己去写代码,一旦卡壳就会回去翻看老师的讲解或者源代码,仔细体会。语感的培养还好一些,但是硬件设计思维在短时间内很难做到融会贯通。

这时,我尝试半自主写出来的小项目代码不仅有语法错误,还有很多逻辑漏洞。简单的语法错误容易排除掉,难在排除逻辑漏洞,逻辑漏洞的排除过程,也就是自身硬件设计思维培养和健全的过程。

排除逻辑漏洞的过程好比是在排雷。很多时候,代码看着差不多,但是仿真、上板验证的结果却大相径庭。而这时我犯了一个致命的错误:逐段对照着老师的代码检查自身代码,一遍两遍三遍......一直检查不出问题出在哪里的时候,我便失去了耐心,直接把老师的那个片段复制粘贴过来了,然后还沾沾自喜地觉得自己可以完成这些小项目了。于是,这些雷点就响当当的埋在那里,我也就当压根没看到。

东窗事发始于在半自主式写完课堂上的所有小项目,并且上了两节复杂数字时钟(功能类似电子表,在数码管上实现)课后,便兴冲冲地尝试独立写出这个时钟项目。

写项目的时间是快乐且短暂的,经常是撸一天代码,不知不觉天已黑。于是,爆肝三天,我写出来了这一堆粘贴到vivodo上面,右边错误提示直接连成红线的东西。

当时这件事对我打击不小,一连两天都是一蹶不振的样子。不过也就两天,我迅速调整状态,告诫自己打破幻想,认清现实,仔细分析问题出在哪里,苦思冥想,问题还是出在之前的那些逻辑上的雷点。斟酌之后,打算第三次过一遍之前的小项目,目的很明确:排雷!

在这里要给初学者一点建议:前期做项目时,先画框架图、状态转移图、时序图,再来上手写代码,会有事半功倍的效果。如果是简单的图,可以直接在纸上画,对于稍复杂一点的,建议用Visio软件来画框架图和状态转移图,Time Gen来画时序图,更便于修改。如果项目结束后想进行资源整合,可以把Time Gen的时序图导入到Visio中。(但是到了后期,面对一些稍复杂的项目,还是推荐用Visio来画图)(具体操作方法:https://www.cnblogs.com/lilyhappygirl/p/11184470.html)

我依然记得“排雷”的青葱岁月,那会感觉自己被一行行代码虐得体无完肤。这可能也是零基础玩家的痛苦之处:半路出家从Verilog学起,并不了解底层逻辑究竟是怎么实现的,写起代码来就一种搭建空中楼阁的感觉。所以这里有一个需要特别注意、也是我当时没意识到的、直到现在自身也比较欠缺的一个点:Verilog HDL既然是一种硬件描述语言,但是它究竟是怎么通过代码综合出对应的功能电路呢?或者说是每一段代码背后对应什么样的电路呢?每一个逻辑雷点归根结底都会落在底层逻辑电路如何实现这一层。因此在每次独立完成一个项目后,一定要对照着自己的代码研究一下综合出的RTL图,细细琢磨什么样的代码对应电路中的哪些结构,做到图码合一。

如果能独立设计出复杂数字时钟,debug完成并且上板成功的话,也就对Verilog的掌握到达了一定程度。

三、坚定信念 蹒跚前行

掌握了基础语法后,也就相当于拿到了学习更深层次内容的钥匙。接下来各种IP核的调用、各种通信协议的学习以及不同接口的图像显示学习等等,烧脑程度不亚于“排雷”。

打开这个大门后,会不禁感叹“吾生有涯,而知无涯也”!本人也是新手,以下内容均为学习之余的兴趣挖掘。

最近大热的国人自主研发的香山处理器,是一款开源的高性能 RISC-V 处理器,基于 Chisel 硬件设计语言实现,支持 RV64GC 指令集。关于香山选择Chisel作为开发语言的解读,可参阅下文(https://mp.weixin.qq.com/s/NJCdDMAf1pQs_rdt-5gyBQ)

Chisel是一种更为高效的开发语言。下面这篇知乎文章对现阶段各种开发语言的解读挺中肯的。(https://zhuanlan.zhihu.com/p/73978174)

Chisel编程语言介绍:

Chisel是由伯克利大学发布的一种开源硬件构建语言,通过使用高度化的参数生成器和分层的专用硬件设计语言来支持高级硬件设计。

重要特性:

内嵌Scala编程语言

层次化+面向对象+功能构建

使用Scala中的元编程可以高度地参数化

支持专用设计语言的分层

生成低级Verilog设计文件,传递到标准ASIC或FPGA工具

采用Chisel设计的电路,经过编译,可以得到针对FPGA、ASIC的Verilog HDL代码,还可以得到对应的时钟精确C++模拟器。

Chisel -> FPGA Verilog

Chisel -> ASIC Verilog

Chisel -> C++ Simulator

Scala语言:不仅是面向对象编程语言,而又无缝地结合了命令式编程和函数式编程风格。 Scala可以与Java互操作 。它用scalac这个编译器把源文件编译成Java的class文件(即在JVM上运行的字节码)。你可以从Scala中调用所有的Java类库,也同样可以从Java应用程序中调用Scala的代码。

目前,有多个开源项目使用 Chisel 作为开发语言,包括采用RISC-V架构的开源标量处理器Rocket、开源乱序执行处理器BOOM(Berkeley Out‐of‐Order Machine )等。

(斜体内容选自CSDN平台,作者 JepsonWong 的文章《Chisel介绍》)

但是鉴于Verilog HDL和VHDL仍然占据市场主导地位的现状,Chisel语言的普及不是一蹴而就的事情。

可以预见的是,未来十几年时间,中国的芯片市场都是蓬勃向好的发展势头,这个风口可能不亚于十几年前的IT行业。而RISC-V指令集在未来则很有可能打破ARM、X86复杂指令集的垄断地位。同时国内国外的环境也决定了,这是中国芯片产业实现追赶的一个契机。

如果RISC V在未来成为主流指令集,Chisel语言的普及也是大势所趋。但同时,入门芯片行业的难度也会再上一个台阶。