【FPGA原型验证】附录基础知识:FPGA/CPLD基本结构与实现原理

聚焦Xilinx ISE

介绍Xilinx公司及其产品的基本情况,并在此基础上描述了CPLD和FPGA的内部结构及基本原理。

1.1 Xilinx公司及其产品介绍

总部设在加利福尼亚圣何塞市(San Jose)的Xilinx是全球领先的可编程逻辑解决方案的供应商,图1-1为公司标志。

Xilinx公司的业务是研发、制造并销售高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核,其相关产品在全球占有大量的份额,客户通过使用Xilinx及其合作伙伴的自动化设计软件和IP核,进行器件编程及设计的工作,最终实现特定的逻辑功能。

1.1.1 Xilinx公司简介

Xilinx公司成立于1984年,它首创了现场可编程逻辑阵列(FPGA)这一创新性的技术,并于1985年首次推出商业化产品。目前Xilinx满足了全世界对FPGA产品一半以上的需求。Xilinx产品线还包括复杂可编程逻辑器件(CPLD)。

Xilinx可编程逻辑解决方案缩短了电子设备制造商开发产品的时间并加快了产品面市的速度,从而减小了制造商的风险。

与采用传统方法,如固定逻辑门阵列相比,利用Xilinx可编程器件,客户可以更快地设计和验证他们的电路。

而且,由于Xilinx器件是只需要进行编程的标准部件,客户不需要像采用固定逻辑芯片时那样等待样品或者付出巨额成本。Xilinx产品已经被广泛应用于从无线电话基站到DVD播放机的数字电子应用技术中。

作为一个可编程逻辑器件的供应商,Xilinx有自己的开发套件,至今已经形成了一个完整的整体。Xilinx公司提供的开发软件主要有以下几种。

- ● ISE:Xilinx公司集成开发的工具

- ● Foundation:Xilinx公司早期的开发工具,逐步被ISE取代

- ● ISE Webpack:Webpack是Xilinx公司提供的免费开发软件,功能比ISE少一些,可以从Xilinx网站下载

- ● 嵌入式开发套件(EDK):用于开发集成PowerPC硬核和Micro Blaze软核CPU的工具

- ● System Generator for DSP:配合Matlab,在FPGA中完成数字信号处理的工具

- ● Xilinx IP核:Xilinx公司拥有非常完整的IP库

FPGA/CPLD基本结构与实现原理

FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于FPGA和CPLD结构上的差异,具有各自的特点,为了更好地理解FPGA和CPLD的特点和应用场合,下面将对FPGA和CPLD基本结构与实现原理进行简单的介绍,这部分内容将同样有助于用户进行相关的产品设计。

1、Intel/Altera FPGA

Intel/Altera FPGA组成: ALMs、LEs、RAM、DSP Blocks、Multipliers、PLLs等。

Intel/Altera的可编程逻辑单元通常被称为LE(Logic Element,逻辑单元),由一个Register和一个LUT组成。

再将10个LE有机组合起来,构成更大的逻辑功能单元——逻辑阵列模块(LAB,Logic Array Block),LAB中还包含LE间的进位链、LAB控制信号、LUT级联链、局部互连线资源、寄存器级联链等连线和控制资源。

2、Xilinx FPGA

Xilinx FPGA组成: CLB(Configable Logic Block)包含Slices和DRAM。

CLB是由Slices构成的,每一个Slices基本是由LUT、进位链、MUX和寄存器组成。

Xilinx的可编程逻辑单元被称为Slice,由上下两部分组成。

每部分都由一个Register和一个LUT组成,被称为LC(LogicCell,逻辑单元),两个LC间也有一些共用逻辑。可以完成LC之间的配合与级联。

3、Lattice FPGA

Lattice组成的主要可编程逻辑单元叫PFU(ProgrammableFuncTIonUnit),是由8个LUT和8~9个Register组成。

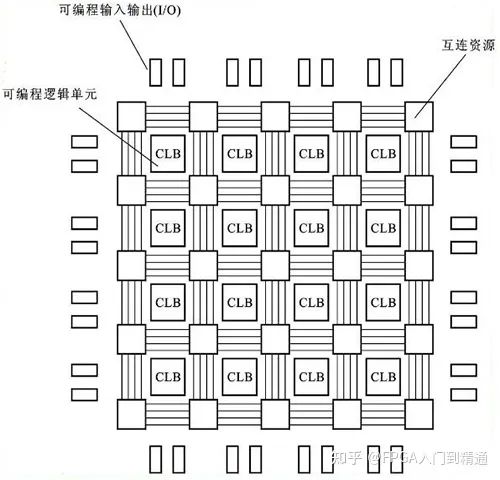

1.2.1 FPGA基本结构与实现原理

![]()

1)可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元。

实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个由4或6个输入、一些选型电路(多路复用器等)和触发器组成的可配置开关矩阵。

开关矩阵是高度灵活的,可以进行配置以便处理组合逻辑、移位寄存器或RAM。

相应器件的数据手册中提供了更系统的详情。

互连CLB提供了逻辑性能,灵活的互连布线在CLB和I/O之间发送信号。有几种布线方法,从专门实现CLB互连的到快速水平和垂直长线,再到实现时钟与其他全局信号的低歪斜发送的器件。

非特别规定,设计软件使得互连布线任务从用户眼前消失,这样就极大地降低了设计复杂度。

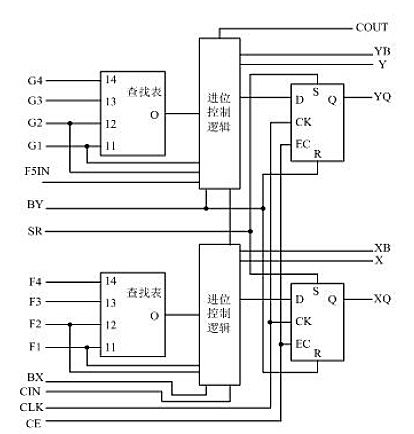

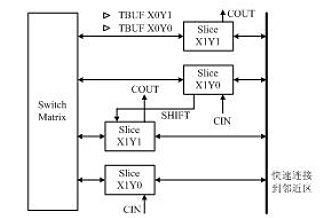

在赛灵思公司公司的FPGA 器件中,CLB 由多个( 一般为4 个或2 个) 相同的Slice 和附加逻辑构成,如图2-5 所示。每个CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式 RAM 和分布式 ROM。

Slice 是赛灵思公司公司定义的基本逻辑单位,其内部结构如图2-6 所示,一个 Slice 由两个4 输入的函数、进位逻辑、算术逻辑、存储逻辑和函数复用器组成。

算术逻辑包括一个异或门(XORG) 和一个专用与门(MULTAND),一个异或门可以使一个Slice 实现2bit 全加操作,专用与门用于提高乘法器的效率;

进位逻辑由专用进位信号和函数复用器(MUXC) 组成,用于实现快速的算术加减法操作;

4 输入函数发生器用于实现4 输入LUT、分布式RAM 或16 比特移位寄存器(Virtex-5 系列芯片的Slice 中的两个输入函数为6 输入,可以实现6 输入LUT 或64 比特移位寄存器) ;

进位逻辑包括两条快速进位链,用于提高CLB 模块的处理速度。

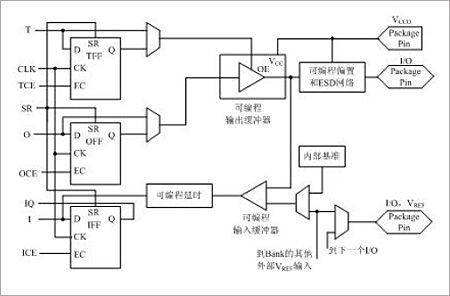

3)I/O块(IOB)

当今的FPGA支持很多I/O标准,这样就为您的系统提供了理想的接口连接。

FPGA内的I/O按组分类,每组都能够独立的支持不同的I/O标准。

当今领先的FPGA提供了很多I/O组,这样就实现了I/O支持的灵活性。

排成阵列的逻辑单元由布线通道中的可编程内连线连接起来实现一定的逻辑功能,即分段的金属互连线可以由编程开关以任意方式连接形成逻辑单元之间要求的信号线。

可编程输入/ 输出单元简称I/O 单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/ 输出信号的驱动与匹配要求,其示意结构如图2-4 所示。

FPGA 内的I/O 按组分类,每组都能够独立地支持不同的I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O 物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

目前,I/O 口的频率也越来越高,一些高端的FPGA 通过DDR 寄存器技术可以支持高达 2Gbps 的数据速率。

外部输入信号可以通过IOB 模块的存储单元输入到FPGA 的内部,也可以直接输入FPGA 内部。

当外部输入信号经过IOB 模块的存储单元输入到FPGA 内部时,其保持时间(Hold Time) 的要求可以降低,通常默认为0。

为了便于管理和适应多种电器标准,FPGA 的IOB 被划分为若干个组(bank),每个bank 的接口标准由其接口电压VCCO 决定,一个bank 只能有一种VCCO,但不同bank 的VCCO 可以不同。

只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

4)存储器

大多数FPGA均提供嵌入式Block RAM存储器,这可以在您的设计中实现片上存储器。

Xilinx FPGA在36 kbit块中提供高达10Mbits的片上存储器,可以支持真正的双端口操作。

块RAM 可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM) 以及FIFO 等常用存储结构。

RAM、FIFO 是比较普及的概念,在此就不冗述。

CAM 存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM 中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。

除了块RAM,还可以将FPGA 中的LUT 灵活地配置成RAM、ROM 和FIFO 等结构。在实际应用中,芯片内部块RAM 的数量也是选择芯片的一个重要因素。

单片块 RAM 的容量为18k 比特,即位宽为18 比特、深度为1024,可以根据需要改变其位宽和深度,

但要满足两个原则:首先,修改后的容量( 位宽 深度) 不能大于18k 比特;

其次,位宽最大不能超过36 比特。

当然,可以将多片块RAM级联起来形成更大的RAM,此时只受限于芯片内块RAM的数量,而不再受上面两条原则约束。

5)完整的时钟管理 -底层内嵌功能单元

业内大多数FPGA均提供数字时钟管理(Xilinx的全部FPGA均具有这种特性)。

Xilinx推出的最先进的FPGA提供数字时钟管理和相位环路锁定。相位环路锁定能够提供精确的时钟综合,且能够降低抖动,并能够实现过滤功能。

内嵌功能模块主要指 DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP 等软处理核(Soft Core)。

现在越来越丰富的内嵌功能单元,使得单片FPGA 成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC 平台过渡。

DLL 和PLL 具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。

赛灵思公司生产的芯片上集成了 DCM 和 DLL,Altera 公司的芯片集成了 PLL,Lattice 公司的新型芯片上同时集成了PLL 和DLL。

PLL 和DLL 可以通过IP 核生成的工具方便地进行管理和配置。DLL 的结构如图2-8 所示。

6)丰富的布线资源

布线资源连通FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。

FPGA 芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/ 置位的布线;

第二类是长线资源,用以完成芯片Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。

从本质上讲,布线资源的使用方法和设计的结果有密切、直接的关系。

7)内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA 处理能力强大的硬核(Hard Core),等效于ASIC 电路。

为了提高FPGA 性能,芯片生产商在芯片内部集成了一些专用的硬核。

例如:为了提高FPGA 的乘法速度,主流的FPGA 中都集成了专用乘法器;

为了适用通信总线与接口标准,很多高端的FPGA 内部都集成了串并收发器(SERDES),可以达到数十Gbps 的收发速度。

赛灵思公司的高端产品不仅集成了Power PC 系列CPU,还内嵌了DSP Core 模块,其相应的系统级设计工具是EDK 和Platform Studio,并依此提出了片上系统(System on Chip) 的概念。

通过PowerPC™、Miroblaze、Picoblaze 等平台,能够开发标准的DSP 处理器及其相关应用,达到SOC 的开发目的。

此外,新推出赛灵思的FPGA 系列如Virtex-5 LXT 还内建了PCI Express 和三态以太网MAC 硬核(TEMAC),与软核实现方式相比,硬核可以把功耗降低5~10 倍, 节约将近90% 的逻辑资源。

Xilinx 三态以太网MAC 核是一个可参数化的核,非常适合在网络设备中使用, 例如开关和路由器等。可定制的TEMAC 核使系统设计者能够实现宽范围的集成式以太网设计,从低成本10/100 以太网到性能更高的1GB端口。TEMAC 核设计符合 IEEE 802.3 规范的要求,并且可以在 1000Mbps、100 Mbps 和 10 Mbps 模式下运行。

另外,它还支持半双工和全双工操作。TEMAC 核通过 Xilinx CORE Generator™ 工具提供,是 Xilinx 全套以太网解决方案的一部分。

软核、硬核以及固核的概念:

- 硬核:就像一个已经完全组装好的乐高玩具,你不能改变它的形状或功能,除非重新做一个新的。在电子设计中,硬核是一个已经设计好并且被制造出来的芯片硬件,它不能再被改变。

- 固核:有点像一个半成品的乐高玩具,你可以根据需要添加或移除某些部分,但它已经有了基本的框架和功能。在电子设计中,固核是一个经过设计但还没有被制造出来的芯片硬件,可以根据需要进行修改。

- 软核:就像一堆乐高积木的组件,你可以随意组合和创造。在电子设计中,软核是一个只有设计和功能描述的IP模块,它还没有被物理实现,可以根据不同的需求在不同的芯片上实现。

1.2.2 查找表(Look-Up-Table)的原理与结构

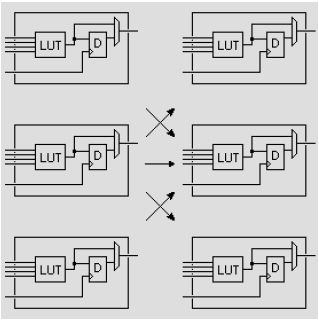

Altera的ACEX、APEX系列,Xilinx的Spartan、Virtex等FPGA系列采用查找表(Look-Up-Table)结构,简称为LUT,其本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16× 1的RAM。

当用户通过原理图或HDL语言描述了一个逻辑电路以后,CPLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出相应得逻辑运算结果。

一个四输入与门的例子,如表1-7所示。

图1-8中的A、B、C、D输入信号通过FPGA芯片的引脚输入后,进入可编程部分,然后作为地址线连到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样实现了相应的组合逻辑。

图1-8所示的电路中,D触发器是直接利用LUT后面D触发器来实现的。

时钟信号CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触发器的时钟端。

触发器的输出与I/O脚相连,把结果输出到芯片引脚。

这样就实现了图1-8所示电路的逻辑功能。

提示:以上这些步骤都是由软件自动完成的,不需要人为干预

图1-8所示为一个简单的例子,该示例只需要一个LUT,外加一个触发器就可以完成相应功能。

当面临一个复杂的逻辑功能时,单一的LUT无法完成或实现的情况下,需要通过进位逻辑,将多个单元相连,以形成复杂的逻辑。

由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,所以一定要外加一片专用配置芯片,在上电时,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作,由于配置时间很短,通常不会影响到系统正常工作。

也有少数FPGA采用反熔丝或Flash工艺,对这种FPGA,就不需要外加专用的配置芯片。

1.2.3 CPLD基本结构与实现原理

1.CPLD基本结构

每个器件是一个由多个逻辑块(Logic Block)、I/O块组成,通过内部互连矩阵完全互连的子系统,I/O块提供器件的I/O缓冲,每个逻辑块提供具有一定数目的输入和输出的可编程逻辑的容量。分别描述如下:

1)逻辑块(Logic Block)

每个逻辑块由独立的宏单元、乘积项阵列和乘积项分配组成。

宏单元是PLD的基本结构,由它来实现基本的逻辑功能。

每个宏单元能够实现一个组合的或寄存的功能。

LB负责信号传递,连接所有的宏单元,也接受全局时钟、输出使能和复位/置位信号,同时还可以产生驱动互连矩阵的输出,这些输出信号和相应的输出使能信号也可以用于完成对I/O块(I/O Block)的驱动

2)互连矩阵(Interconnect)

互连矩阵要将来自I/O的信号和逻辑块的输出布线到器件内任何逻辑块的输入。一般互连矩阵有两种形式:基于阵列的互连和基于多路开关的互连。

基于阵列的互连是完全的纵横开关的实现方式,它允许任何输入到互连矩阵中的信号布线到任何逻辑块,是完全可布通的。

基于多路开关的互连是对逻辑块的每一个输入有一个多路转换器,输入到互连矩阵的信号被连接到每个逻辑块的大量多路开关的输入端,这些多路转换器的选择端是可编程的,只允许其一个输入通过它进入逻辑块。

3)I/O块(I/O Block)

I/O控制块负责I/O的电气特性控制,比如可以设定I/O输出为集电极开路输出、摆率控制输出、三态输出等不同输出形式。

下面简要介绍宏单元的基本结构。宏单元的具体结构:

左侧是乘积项阵列,实际就是一个与或阵列,每一个交叉点都是一个可编程节点,如果导通就是实现“与”逻辑。

后面的乘积项选择矩阵是一个“或”阵列。两者一起完成组合逻辑。

图1-10右侧是一个可编程D触发器,它的时钟,清零输入都可以编程选择,可以使用专用的全局清零和全局时钟,也可以使用内部逻辑(乘积项阵列)产生的时钟和清零。

如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA或输出到I/O脚。

1.2.4 FPGA/CPLD性能特点差异

● CPLD适合于完成各种算法和组合逻辑,FPGA更适合于完成时序逻辑。换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构

● CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性

●在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门下编程,而CPLD是在逻辑块下编程

● FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现

● CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或Fast Flash技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法复杂

● CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于FPGA是门级编程,并且CLB之间采用分布式互连,而CPLD是逻辑块级编程,并且其逻辑块之间的互连是集总式的

分布式存储是将数据分散存储在多个节点上,而集总式存储则是将所有数据存储在中心服务器上。分布式存储具有更高的扩展性和容错性,而集总式存储则更适合处理大规模数据。

●编程方式上,CPLD主要是基于E2PROM或Flash存储器编程,编程次数可达1万次,优点是系统断电时编程信息也不丢失。CPLD又可分为在编程器上编程和在系统编程两类。FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从器件外部将编程数据重新写入SRAM中。其优点是可以编程任意次,可在工作中快速编程,从而实现板级和系统级的动态配置

● CPLD保密性好,FPGA保密性差

● 一般情况下,CPLD的功耗要比FPGA大,且集成度越高越明显

参考资料

- 【FPGA基础知识 (FPGA 内部结构)】

- 【FPGA内部结构】

- [【FPGA/CPLD设计与应用】:李建、谈世哲、管殿柱]