RGMII接口介绍

RGMII接口概述

RGMII全称为Reduced Gigabit Media Independent Interface,是一种网络接口标准,用于千兆以太网芯片与PHY芯片之间的接口标准。RGMII接口的设计目的是为了减少I/O的数量,尽可能减小网卡PCB占用面积,同时提高数据传输效率。RGMII接口的实现有两种方式,分别是外部PHY与MAC之间的连接和SoC内部集成的MAC和PHY连接,不同的实现方法有不同的实现方式和接口定义。

RGMII均采用4位数据接口,工作时钟125MHz,并且在上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式,支持传输速率:10M/100M/1000Mb/s ,其对应clk 信号分别为:2.5MHz/25MHz/125MHz。

4根线,单向总共500M带宽。

发送时钟:MAC---->PHY

接收时钟:PHY----->MAC

GMII引脚定义

GMII(Gigabit Media Independant Interface),千兆MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。GMII接口数据结构符合IEEE以太网标准,该接口定义见IEEE 802.3-2000。信号定义如下:

RGMII引脚定义

RGMII

RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

发送/接收数据线由8条改为4条

TX_ER和TX_EN复用,通过TX_CTL传送

RX_ER与RX_DV复用,通过RX_CTL传送

1 Gbit/s速率下,时钟频率为125MHz

100 Mbit/s速率下,时钟频率为25MHz

10 Mbit/s速率下,时钟频率为2.5MHz

信号定义如下:

RGMII接口的双工类型

RGMII接口提供了两种双工类型:全双工和半双工。全双工模式下,MAC和PHY同时发送和接收数据,半双工模式下,MAC和PHY可以交替发送和接收数据。在使用RGMII接口进行数据传输时,需要根据应用选择适当的双工模式。

实现RGMII接口的方法

外部PHY和MAC之间的连接

外部PHY和MAC之间的RGMII接口通过两对差分信号进行连接。RXD,TXD和RXCLK、TXCLK之间进行差分匹配。RXD和TXD之间还配有RXDV和TXEN两个控制信号。此方式的RGMII接口由MAC和PHY两个芯片零散分布,但设计方便,因所需I/O资源少,可降低成本。

/* RGMII硬件接口定义 */

typedef struct rgmii_hw {

struct mii_dev *bus; /* Bus the device is on */

uint addr; /* Ethernet PHY addres */

uint tx_clk; /* TX clock input frequency in Hz */

uint rx_clk; /* RX clock input frequency in Hz */

int txen_pin; /* Pin MII_TXEN is on */

int txd0_pin; /* Pin MII_TXD0 is on */

int txd1_pin; /* Pin MII_TXD1 is on */

int txd2_pin; /* Pin MII_TXD2 is on */

int txd3_pin; /* Pin MII_TXD3 is on */

int rx_clk_delay; /* RX clock delay in ns */

int rx_dv_delay; /* RX DV delay in ns */

enum rgmii_type type; /* RGMII or RGMII_ID */

} rgmii_hw_t;SoC内部MAC和PHY之间的连接

SoC内部MAC和PHY之间的RGMII接口则是通过PHY/MAC接口完成物理连接,MAC和PHY通常集成在同一块芯片中,通过内部信号线进行数据的传输。

/* RGMII软件接口定义 */

typedef struct rgmii {

unsigned rgmii_mdio_base; /* mdio virtual base */

unsigned rgmii_phy_addr; /* PHY address - default is #define */

unsigned rgmii_rx_clk_hz; /* CLK signal input frequency in Hz */

unsigned rgmii_tx_clk_hz; /* CLK signal output frequency in Hz */

} RGMII;RGMII接口在硬件设计中的应用

RGMII接口在千兆以太网芯片与PHY芯片之间的接口标准中具有重要的应用,特别是在计算机硬件设计的应用中,更是不可或缺。在硬件设计中,RGMII接口可以作为芯片与PHY之间的数据传输接口。例如,在计算机板卡里,芯片件间和芯片与速度更快的电信运营商网卡之间有一个RGMII接口。在处理器和PHY芯片之间建立RGMII接口可以大幅提高数据传输速率,同时也简化了系统设计。

为什么RGMII时钟线和数据线要做延时处理?

由于RGMII的数据传输是根据时钟信号采样获得的,RGMII时钟在1000Mb/s速率下载上升沿河下降沿均进行采样;在100Mb/s速率及10Mb/s速率下,仅在上升沿采样数据位。这就会出现一个问题,在时钟上升沿或下降沿采样时,数据要保证稳定才能使采样结果更加准确,这就要求采样点尽量靠近数据位中间点,在时钟线上延时就是为了让采样点尽量靠近数据位信号中心点,使采样结果更加稳定。也就是说在时钟线信号上升沿的时候,数据已经走了2个bit的位置上,采样结果才是准确的。

要对时钟信号额外增加 1.5~2 ns 的延迟以保证接收端的建立/保持时间满足要求。

以下为解释为什么需要对时钟添加delay (参考于https://ethernetfmc.com/docs/user-guide/rgmii-timing/)

The RGMII standard specifies clock and data signals to be output with no skew, ie. the clock edges are aligned with the data edges. This is not ideal for the receiver’s sampling circuit, but it greatly simplifies the transmitter circuit.(RGMII标准指定时钟和数据信号输出没有倾斜,即,时钟边缘与数据边缘对齐。这对于接收机的采样电路并不理想,但它极大地简化了发送电路。)

RGMII clock and data signals as they must be presented to the receiving circuit for optimal sampling. The clock skew has been added by the PCB trace or the receiving device.(RGMII时钟和数据信号,因为它们必须呈现给接收电路以进行最佳采样。时钟倾斜已由PCB跟踪或接收设备添加。)

Adding the clock skew :

In an FPGA based system, there are three stages where the required skew (ie. delay) can be added to the TX and RX clock signals. The first stage is in the FPGA, the second stage is on the PCB traces (ie. with longer clock traces than the data traces) and the third stage is in the PHY. In an optimal RGMII interface, the skew is added at only one stage in the TX and RX path, and the other two delay stages are disabled or not implemented.

The skew of the TX and RX clocks can be managed independently, it does not have to be implemented at the same stage on each path, but it must be implemented somewhere on each path. So it is critical to understand each of the delay stages in your target system in order to ensure that the clocks in your RGMII interface are properly skewed. We will now discuss each skew stage and the various ways to enable or disable them.

为什么RGMII配置下1000Mb/s的延时要求比100Mb/s要求严格?

因为在1000Mb/s速率下,RGMII时钟速率为125M,在100Mb/s速率下,RGMII时钟速率为25M,在125M的时钟速率侠,每隔时钟所战友的时间长度会很短,稍微一点延时误差就会导致采样出错,而25M时钟所占时间稍长,对延时误差的容错性更高。

RGMII1.3协议和RGMII2.0协议的区别?

对于RGMII1.3协议,部分PHY芯片或者交换机芯片不支持芯片配置时钟延时,只能依靠PCB走线延时或支持配置延时的芯片配置。

对于RGMII2.0协议,部分PHY芯片或者交换机芯片支持芯片配置时钟延时,在依靠PCB走线延时的同时,在芯片内部也能调整TX_CLK或RX_CLK,这就使得PCB走线的容错性大大提高。

RGMII如何配置延时?

按照RGMII数据随时钟源发送的原理(数据线和时钟线同方向),RGMII延时一般都会配置在发送端,再结合线上延时最终使数据完美传输。

但对于异常情况,若时钟发送端无法配置延时,这就需要在接收端配置接收延时,在配置接收延时时,示波器无法测出配置的延时数据,只能看到延时偏差,即数据时超前时钟还是滞后时钟。因为这是芯片内部在接收时自己做的延时,线上的时钟信号仍然是由时钟发送端发送过来的无延时时钟。

RGMII的时钟延时为什么常用2ns?

在125M时钟下,最佳的延时时间是2ns。

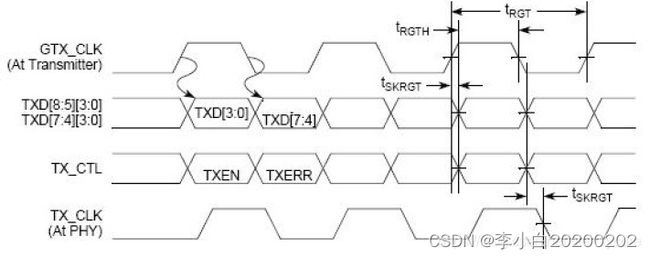

虽然RGMII信号线减半,但TXC/RXC时钟仍为125Mhz,为了达到1000Mbit的传输速率,TXD/RXD信号线在时钟上升沿发送接收GMII接口中的TXD[3:0]/RXD[3:0],在时钟下降沿发送接收TXD[7:4]/RXD[7:4],并且信号TX_CTL反应了TX_EN和TX_ER状态,即在TXC上升沿发送TX_EN,下降沿发送TX_ER,同样的道理试用于RX_CTL,下图为发送接收的时序: