数字电路实验1:4联装7段数码管管脚功能、传统实验箱非门延迟、fpga各种虚拟门特性及边沿检测器

软件工程学院

目录

第一组数字电路实验报告一

一、 实验室环境与仪器

1. 实验环境

2. 实验仪器

二、 实验内容

(1) 测量4联装7段数码管管脚功能

(2) 测量74LS00与非门管脚功能与门延迟(使用传统实验箱)

(3) 74LS197产生测试信号(使用FPGA实验箱)

(4) FPGA虚拟逻辑门性能测试——测量虚拟与非门特性

(5) FPGA虚拟逻辑门性能测试——测量虚拟非门特性

(6)FPGA虚拟逻辑门性能测试——测量虚拟与门特性

(7) FPGA虚拟逻辑门性能测试——测量虚拟与非门特性

(8)FPGA虚拟逻辑门性能测试——测量虚拟或门特性

(9)FPGA虚拟逻辑门性能测试——测量虚拟异或门74LS86特性

(2) -(9)分析总结:

(10) 设计边沿检测器——使用虚拟逻辑门设计实现上升/下降沿脉冲发生器

- 实验室环境与仪器

- 实验环境

实验时间:2022.11.3 气温:19℃ 地点:教学大楼A412

2.实验仪器

示波器/逻辑分析仪 MSO5354

函数信号发生器 DG4202

实验箱

万用表 DM3058

元器件

- 实验内容

- 测量4联装7段数码管管脚功能

实验过程:使用万用表二极管功能,依次重复连接数码管各引脚。

经测量,7段数码管abcdefgdp和公共端1234的管脚如图所示:

波形说明:蓝色表示输入(与非门的两个输入连通,也就是输入是相同的信号),黄色为输出。根据与非门的功能,当两个输入为高电平,那么输出为低电平;当两个输入为低电平,那么输出为低电平。

经测量,门延迟为22.6ns。

过程:放大之后,运用游标测量功能,选取输入下降沿中间和输出上升沿中间,记录AB游标之间的时间间隔。

- 74LS197产生测试信号(使用FPGA实验箱)

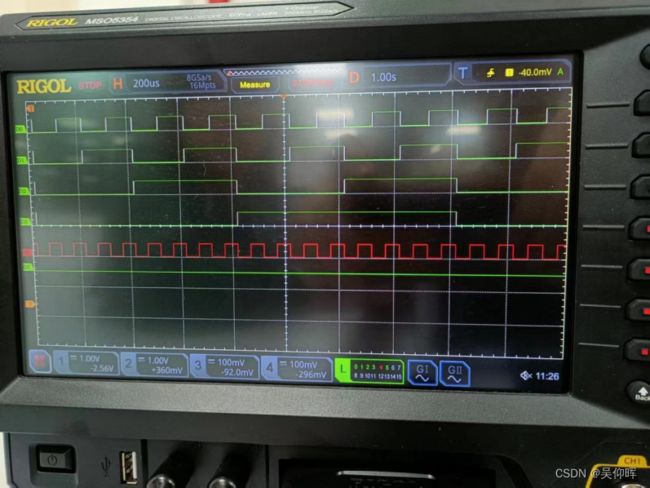

D0、D1、D2、D3为输出,输入输出波形如下:

波形说明:

D0~D3对应197的Q0~Q3(即计数输出的低位到高位),D4(上图中红色的那条)是输入的clk信号。

可以看出D0信号周期是D4的两倍,D1信号周期是D0的两倍,D2信号周期是D1的两倍,D3信号周期是D2的两倍。

宏观上看D0D1D2D3依次输出:0000,0001,0010,0011,0100......也就是十进制(0~15)对应的二进制。

信号的异常错位现象如下:

波形说明;

上图中D0~D3对应197的Q0~Q3,可以看到计数改变的时候D0~D3不是同时变化的。上图中可以看出D0先发生改变,所以大概在计数后55ns左右的时间段内会产生错误的变化。

- FPGA虚拟逻辑门性能测试——测量虚拟与非门特性

测试信号接入虚拟与非门芯片74LS00,D0为输入,D1为输出,输入输出波形如下:

经测量得,与非门的延迟大概为59.6ns。

波形说明:上面两条是输入信号(输入的信号是相同的),下面那一条是与非门的输出信号。当两个输入从低电平上升到高电平,输出讲从高电平下降到低电平。

(5) FPGA虚拟逻辑门性能测试——测量虚拟非门特性

测试信号接入虚拟非门芯片74LS04,D0为输入,D1为输出,输入输出波形如下:

波形说明:

上面的信号为非门的输入信号,下面的信号为非门的输出信号。

经测量得,非门的延迟大概为12.79ns。

波形说明:

当输入信号从高电平下降到高电平,输出信号将从低电平上升到高电平。

(6)FPGA虚拟逻辑门性能测试——测量虚拟与门特性

测试信号接入虚拟与门芯片74LS08,D0、D1为输入,D2为输出,输入输出波形如下:

经测量得,与门的延迟大概为51.8ns。

(7) FPGA虚拟逻辑门性能测试——测量虚拟与非门特性

测试信号接入虚拟与非门芯片74LS20,用74LS197的四个输出作为与非门的四个输入,输入输出波形如下:

波形说明:

上面四条(D0~D3)该与非门的输入信号(实际是74ls197的输出信号),D4(最下面那个信号)是与非门的输出信号。可以观察到,只有当D0~D3输入为1111时,与非门才输出低电平,这与四输入与非门的真值表是对应的。

经测量得,与非门的延迟大概为55.99s.

波形说明:

当输入信号的任意一个为低电平,与非门将输出高电平。所以我们把A游标对准首先发生下降的D0的下降沿,B游标对准输出的上升沿。

(8)FPGA虚拟逻辑门性能测试——测量虚拟或门特性

测试信号接入虚拟或门芯片74LS32,D0、D1为输入,D2为输出,输入输出波形如下:

波形说明:D0、D1为输入信号,D3为输出信号。

可以观察到只有两个输入都是低电平时,才输出高电平。

这与或门的真值表是对应的。

经测量得,或门的延迟大概为53.2s。

波形说明:

当两个输入从高电平下降到低电平,或门也将从高电平下降到低电平。

所以我们将A游标对应到后下降的输入信号。

(9)FPGA虚拟逻辑门性能测试——测量虚拟异或门74LS86特性

测试信号接入虚拟异或门芯片74LS86,D0、D1为输入,D2为输出,输入输出波形如下:

波形说明:

D0、D1为输入信号,D3为异或门的输出信号。可以看到D0D1同时为高电平或低电平时,异或门输出低电平;否则输出高电平。这与异或门的真值表是对应的。

经测量得,异或门的延迟大概为53.2s。

波形说明:

D0D1为低电平,当D0上升到高电平而D1保持不变时,异或门从高电平下降到低电平。

- -(9)分析总结:

从实验测量的结果来看,FPGA虚拟逻辑门的延迟会比真实的芯片的延迟要高一些,在上面的实验测试中,我们可以看到模拟与非门的延迟(22.6ns)还不到FPGA虚拟与非门延迟(59.6ns)的一半。这应该是因为虚拟逻辑门实际运作的电路会比真实芯片要复杂。

此外,不同的FPGA虚拟逻辑门的延迟也会有所不同,这是因为它们的复杂程度不同,在上面的实验测试中虚拟非门的延迟最低,虚拟与非门的延迟最高。

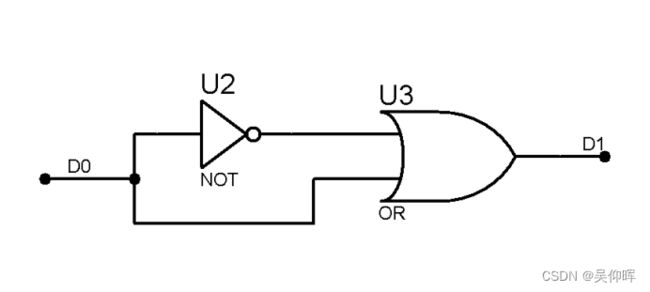

- 设计边沿检测器——使用虚拟逻辑门设计实现上升/下降沿脉冲发生器

上升沿:

设计方法:将一个输入与它的反相同时通过一个与门。

其中D0为输入,D1为输出,当检测到D0的上升, D1将输出一个脉冲,发生器的输入输出波形如下:

脉冲宽度:16.99ns

下降沿:

设计方法:将一个输入与它的反相同时通过一个或门(还可以在最后加一个非门)。

当检测到D0的下降, D1将输出一个(负)脉冲。其中D0为输入,D1为输出,发生器的输入输出波形如下:

脉冲宽度:12.01ns

【反思】最后一个实验中,测量脉冲宽度时,由于采用数字信号输入没有严格按照测量上升沿和下降沿幅度50%处的时间间隔,导致实验结果有一定误差。

而且总体上来讲我们在各实验中延迟的测量只在一处地方测了,所以容易受到偶然因素的影响,增大误差。