NandFlash基础知识

1.存储介质

存储介质按物理材料的不同可分为三大类:光学存储介质、半导体存储介质和磁性存储介质。

最早的SSD使用DRAM来作为存储介质

SSD一般采用NAND闪存芯片作为存储介质

2. Nand flash

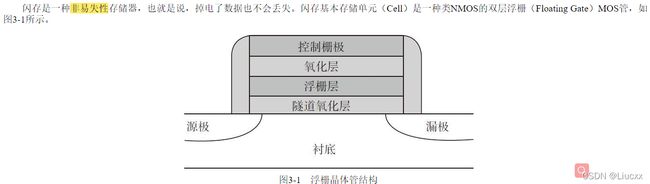

2.1. Nand flash物理结构

2.1.1. Nand flash特点

- 非易失性

- 以page为单位读写,以block为单位擦除

是典型的块设备。 现在有些设备为了方便,提供了一种random read模式,可以只读取1个字节)。

- 集成密度高、单位比特成本低和可靠性高

- 对于Nand的读写,只能由1变成0,不能由0变成1。因此要先对Nand进行erase(0变成1),然后再写。

2.1.2. 分类

- 二维闪存、三维闪存

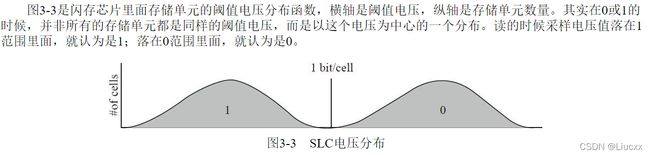

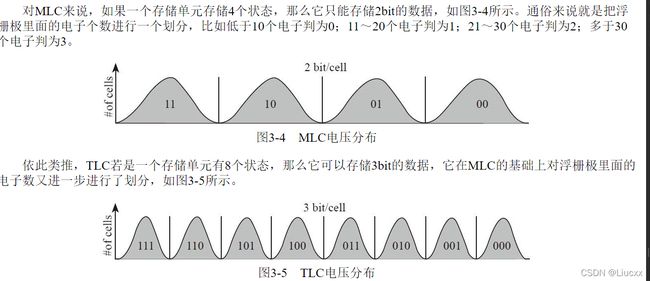

2.1.3. SLC, MLC, TLC, QLC

- SLC: 一个存储单元存储1个bit。

- MLC: 存储2bit

- TLC: 存储3bit (3D TLC 主流)

- QLC: 存储4bit数据

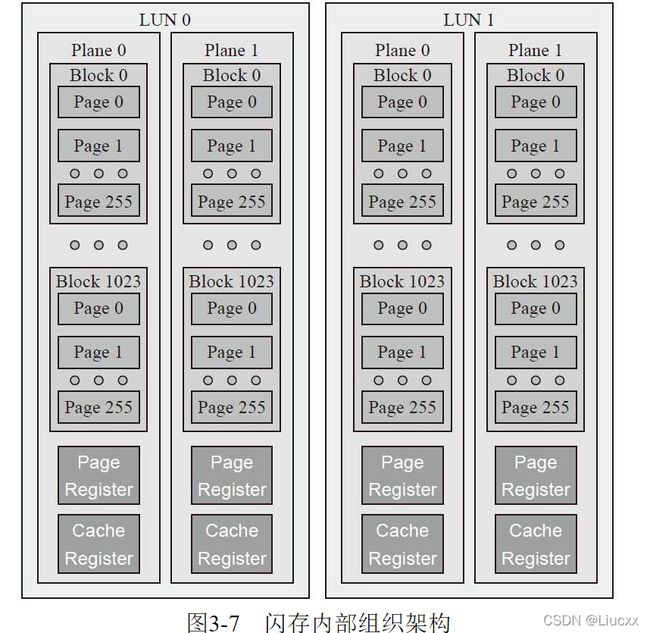

2.2. nanflash 架构

2.2.1. nand flash 硬件部署

- DIE/LUN是接收和执行闪存命令的基本单元.

不同的LUN可以同时接收和执行不同的命令。同一个LUN,一次只能执行一个命令(不能同时读 和 写)。

- 主控写数据: 先写到cache register,再由cache register写到闪存阵列。 以page为单位

读数据相反

2.3.2. cache register、page register作用?

- 优化闪存访问速度。

发送数据时(cache -> 主控),可以同时读下一个page到page register(闪存-> page register).

接收数据时(page -> 闪存),可以将下一个要存的数据放到cache中(主控-> cache register)

2.3.3. 三维闪存

2.4. 闪存的接口

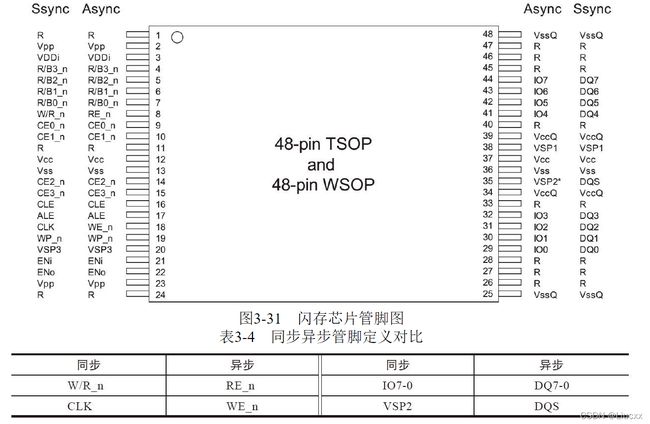

2.4.1. 同步和异步闪存接口对比

- 闪存接口: 同步、异步。

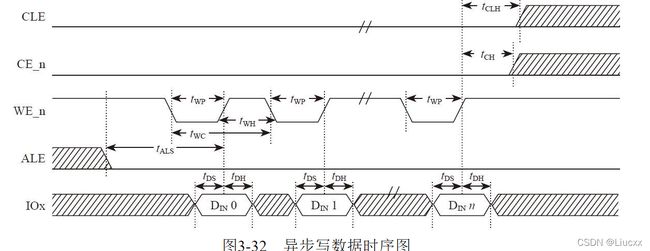

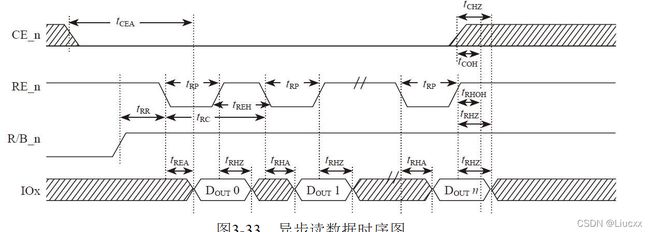

2.4.1.1. 异步时序

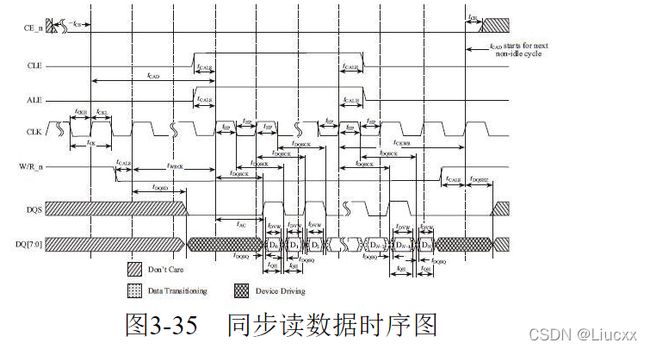

2.4.1.2. 同步时序

- CLK 、DQS 时钟信号和同步信号

- 写数据时,DQS由用户产生。读数据时,DQS由闪存产生

2.4.1.3. 闪存命令集

- SSD主控通过闪存命令集来与NandFlash交互。

- ONFI 2.3协议部分命令集如下

2.4.1.4. 闪存寻址

- NandFlash结构

LUN1 LUN2 ...

Plane1 Plane2 ...

Block1 block2.....

page1 page2 ...

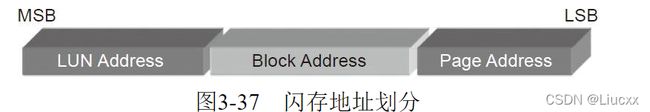

- 闪存使用了行地址、列地址进行访问和管理

列地址: Page内部的偏移地址

行地址: 在ONFI协议中,高位到低位依次表示 : LUN、Block(Plane在Block地址的最低几位)、Page地址。具体位宽由芯片决定。

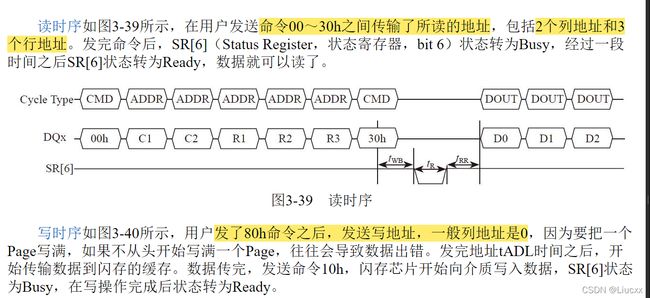

2.5.1.5.读、写、擦时序

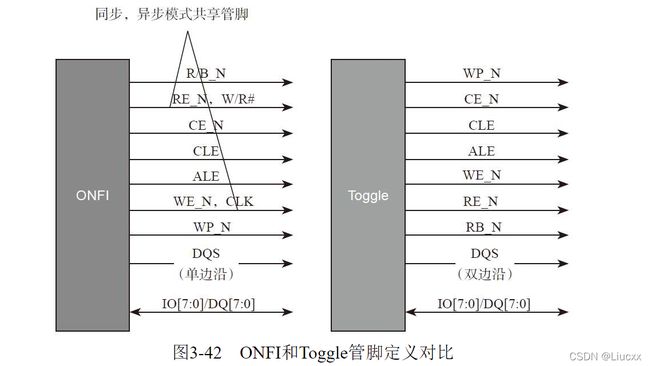

2.5. ONFI与Toggle协议

2.5.1. Toggle协议

- 由三星和东芝一起创建。研发出 一款新的闪存产品 Toogle Nand。

2.5.2. ONFI协议

- ONFI(open NAND Flash Interface): 许多个公司一起制定的协议。

2.5.3. 两种协议对比

2.6. 闪存特性

2.6.1. 闪存存在的问题

- 闪存坏块。 需要有坏块管理机制

- 读干扰。 可能会影响其它page的某些bit反转

- 写干扰。 可能导致bit翻转

- 存储单元间的耦合

- 电荷泄露

2.6.2. NandFlash寿命

- 问题: 频繁读写某些块,会导致磨损、坏块等问题

- 解决方法:

- Wear Leveling 磨损平衡算法

- 降低写放大

- 纠错算法优化(提高容错率)

2.6.3. MCL使用特性

- 对于MCL或TLC:

写一个闪存块的闪存页,应该顺序写page0, 1. 2...

读没有这样的限制

- MLC特有的问题

- MLC最大擦写次数会变小。 (使用wear leveing保证寿命)

- 一个闪存页写失败,可能导致另外页损坏

- 不能随机写

- 写lower page快,写upper page慢

- MLC应对存在问题的一些方法

- 可以只写lower page

- lower和upper打包写

- 定期填充upper page

- 写Lower page时,备份数据,直到upper写完。

- MLC当SLC使用

- 企业级固态硬盘,配备大电容

2.6.4. 读干扰问题

2.6.5. 闪存数据保存期

2.6.5.1.什么是闪存数据保存期

- 数据保存期(Data Retention), 从写入操作到电子慢慢泄漏,直到数据出错,这个期限叫作数据保存期。

到了期限的标致是: 闪存读出来的数据无法用 ECC纠错成功。

闪存一般可能存在的错误: 电气问题 、 读写擦失败、ECC纠错失败

- SLC时代,期限有好几年

TLC时代,期限只有几个月

2.6.5.2. 如何解决数据保存期短问题

- Read Scrub技术(数据巡检、扫描重写技术)

与ZFS类似,固态硬盘空闲时,扫描全盘,对某个闪存页翻转bit数进行计算,超过一定数量,重写数据。

2.7. 闪存数据完整性

2.7.1. 问题及解决方法

- 问题: 容易发生bit位翻转

- 解决方法:

2.7.2. 读错误来源

- 擦写次数多

氧化层老化,电荷容易位置异常,导致读错误

- Date Retention

随时间变化,电子流失,阈值电压值向左移动,读数据发生误判

- 读干扰

读数据时,需要施加电压,影响到其它page

读的次数多后,阈值电压右移

- 存储单元之间的干扰

存储电子的浮栅极是导体,两导体间构成电容。一个存储单元电荷变化引起另其它单元发生电荷变化 。

周围单元是不同状态时,中心单元的阈值电压不同。

- 写错误

一般发生在MLC、TLC2-pass中,是因为upper page是基于lower page的数据的

TLC1-pass中不存在这个问题,因为upper和lower同时写入。

2.7.3. 重读

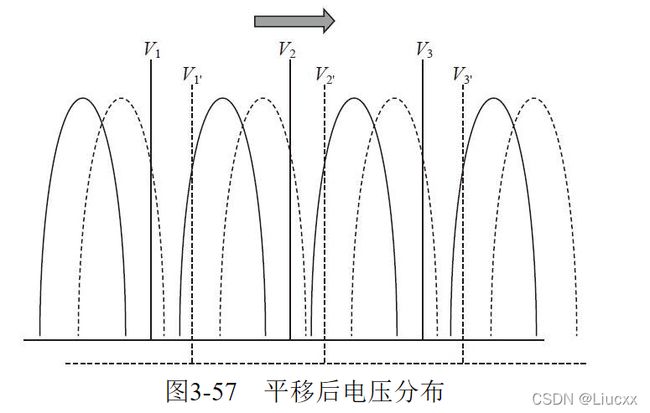

2.7.3.1. 解决电压分布平移问题

- 方法1: 不断改变参考电压,找到可读出数据的电压点,直到正确读出数据

- 方法2: (更复杂的重读) Advanced Retry. 先读附近的单元确定状态,再用不同的参考电压读两次要读的单元,根据附近数据选择结果。

2.7.4.ECC纠错码(error checking and correcting)

2.7.4.1. 常用的ECC纠错算法

ecc一般属于SSD控制器的一个模块,有些闪存内部也集成了ECC模块

原理:

先通过奇偶校验的方法检查错误,也就是存储一个"奇偶检验",其值为8 个比特组里所有1的和,结果为奇或偶(1或0)。

下次再访问数据时,进行奇偶校验,与之前存储的校验值对比。若不相同,就采用一段存储时使用的特殊代码进行校正。

- BCH。 比较常用

- LDPC 逐渐成为主流

2.7.4.2.

- Nand 中额外的预留空间,部分用来写ECC校验数据。 因此,纠错强度受限于闪存页的预留空间

2.7.4.3. 静态ECC纠正、动态ECC纠正

- 静态ECC纠错方案

ECC纠错单元(用户数据)和ECC校验数据大小在整个固态硬盘生命周期都是固定的。纠错能力一直不变

- 动态ECC纠正方案

刚开始使用少的纠错码,能存放更多用户数据(ECC纠正单元)。随着SSD的使用,将纠错码比例增多,用户数据区变小。从而达到动态调整纠错能力。

优点:

开始时使用少的纠错码,op(Over Provisioning,预留空间)更多,减小写放大。

当ECC较少时,带宽利用率越高。

2.7.8. raid

2.7.8.1. RAID介绍

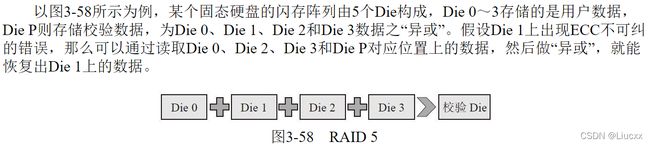

- RAID(Redundant Arrays of Independent Disks)是另一种纠错算法。

Nand中数据bit翻转个数太多,超过ECC纠错能力,ECC就无法纠正了。因此越来越多的SSD都使用RAID(一般是RAID 5)

- 借鉴磁盘阵列技术来确保数据的完整性

- 采用RAID 5技术的SSD,只能恢复单个ECC不可纠的数据

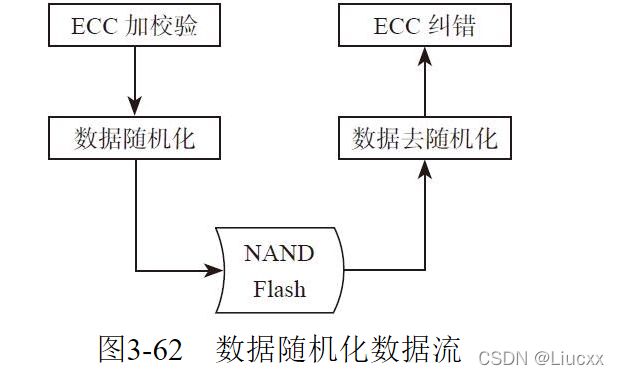

2.7.9. 数据随机化

- 若未进行随机化写。会导致Nand内部电量不均匀,导致抗干扰性下降。

- 让0和1的分布充分隔离

- 降低相邻单元之间的耦合电压产生的影响

- SSD内部一般都有 数据随机化模块, 对用户写入数据加入扰码,使0 和1比较均匀,减小数据发生翻转概率。一般Nand厂商推荐使用AES算法实现数据随机化