《Orange’s 一个操作系统的实现》3.保护模式8-页式存储

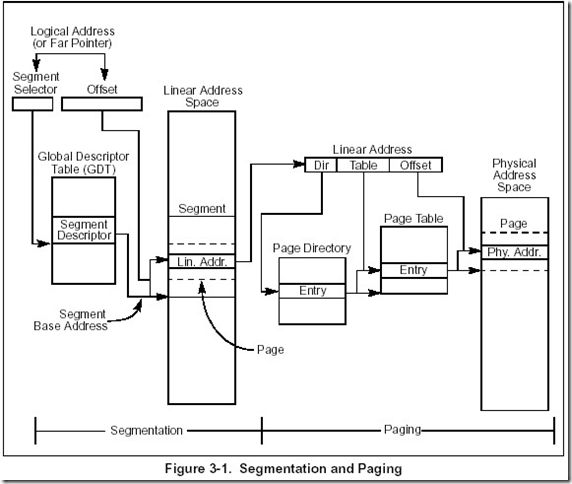

A.分页机制概述(如图)

Segmentation部分为分段机制,逻辑地址通过段选择子,从GDT中对应的段描述符中确定段基址,然后在加上偏移确定线性地址

Paging部分为分页机制:物理地址=f(线性地址)

分页机制使用两级转换表,第一级叫做页目录(Page Directory),存储在一个物理页中.大小为4KB,每个表项4字节,

共有1024个表项(Page Directory Entry).

每个表项对应第二级的一个页表(Page Table),每个页表也有1024项(Page Table Entry),每个表项对应一个物理页。

运行转换时,先是有寄存器cr3指定的页目录中根据线性地址的高10位(图中的Dir)得到页表地址,然后在页表中根据线性地址的第

12到21位(图中的Table)得到物理页首地址,将这个首地址加上线性地址低12位(图中的Offset)便得到了物理地址。

分页机制是否生效的开关位于cr0的最高为PG位,PG=1,分页生效.所以当我们准备好了页目录表和页表,并将cr3指向

页目录表之后,只需重置PG位即可开始分页机制.

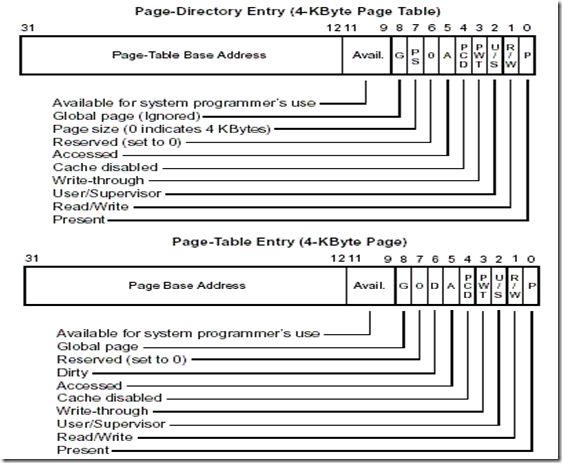

B.PDE和PTE

P存在位:表示当前条目所指向的页或页表是否在物理内存中.P=0,表示页不在内存中,如果处理器试图访问此页会

产生页异常(page-fault exception,#PF);P=1表示页在内存中

R/W指定一个页或者一组页的读写权限.R/W=0表示只读,R/W=1表示可读写

此位与U/S位和cr0中的WP相互作用

U/S指定一个页或者一组页的特权级。此位与R/W和中cr0中的WP相互作用

U/S=0,表示系统级别,如果CPL=0,1,2就在此级别

U/S=1,表示系统级别,如果CPL=3就在此级别

如果cr0的WP=0,即便用户级页面的R/W=0,系统级程序仍然具备写权限.

WP=1,即便用户级页面的R/W=0,系统级程序也不能写入只读页.

PWT用于控制对单个页或者页表的缓冲策略。PWT=0使用Write-back缓冲策略

PWT=1使用Write-through缓冲策略

cr0的CD(Cache-Disable)位被设置时会被忽略

PCD控制对单个页或者页表的缓冲PCD=0时,页或页表可以被缓冲PCD=1,不能

cr0的CD(Cache-Disable)位被设置时会被忽略

A指示页或页表是否被访问。在页或页表刚被加载到物理内存中时被内存管理程序清0,处理器会在第一次

访问此页或页面时设置此位.而且处理器不会自动清除此位。只有软件能清除它

D指示页或页表是否被写入。在页或页表刚被加载到物理内存中时被内存管理程序清0,处理器会在第一次

访问此页或页面时设置此位.而且处理器不会自动清除此位。只有软件能清除它

A位和D位都是被内存管理程序用来管理页和页表从物理内存中换入换出的

PS位决定页大小PS=0页大小为4KB,PDE指向页表

PAT选择PAT(Page Attribute Table)条目。

G指示全局页。如果此位被设置.同时cr4中的PGE位被设置。那么此页的页表和页目录条目不会再TLB中变得无效

处理器会将最近常用的页目录和页表保存在一个叫做TLB(Translation Lookasied buffer)的缓冲区中.加速访问