操作系統恐龍書第十版課後答案 ch12

12.1 State three advantages of placing functionality in a device controller, rather than in the kernel. State three disadvantages.

優點:

- bug不太可能導致系統崩潰;

- 通過使用專用硬體和硬編碼演算法可以提高性能;

- 通過將算法移出核心可以簡化

缺點:

- bug更難修復

- 改進演算法也需要硬體更新

- 嵌入式演算法可能與應用程序對設備的使用發生衝突,影響性能

12.2 The example of handshaking in Section 12.2 used two bits: a busy bit and a command-ready bit. Is it possible to implement this handshaking with only one bit? If it is, describe the protocol. If it is not, explain why one bit is insufficient.

是有可能的,可以使用以下演算法。 讓我們假設我們使用忙碌位元(或命令就緒位元;無論如何此答案相同)。 當位元關閉時,控制器處於閒置狀態。 主機寫入數據輸出,並設定該位元以發出操作準備就緒的訊號(相當於設定命令就緒位元)。 當控制器完成後,它將清除忙碌位元。 然後主機啟動下一個操作。此解決方案要求主機和控制器都讀取以及寫入存取同一位元,這會使電路更複雜和增加控制器的成本。

12.3 Why might a system use interrupt-driven I/O to manage a single serial port and polling I/O to manage a front-end processor, such as a terminal concentrator?

當I/O頻繁且短暫是輪詢比中斷驅動更有效。大量的I/O使用輪詢可以減少資源的浪費

12.4 Polling for an I/O completion can waste a large number of CPU cycles if the processor iterates a busy-waiting loop many times before the I/O completes. But if the I/O device is ready for service, polling can be much more efficient than catching and dispatching an interrupt. Describe a hybrid strategy that combines polling, sleeping, and interrupts for I/O device service. For each of these three strategies (pure polling, pure interrupts, hybrid), describe a computing environment in which that strategy is more efficient than either of the others.

一個混合方法可以根據I/O操作等待的長度在輪詢和中斷之間切換。例如我們可以輪詢和迴圈N次,如果設備仍然處於忙碌在N+1,我們可以設定一個中斷與休眠。這種方法可以避免長忙碌的等待週期,最適合長時間或短時間的忙碌時間。 如果I/O在N+T時完成(其中T是少量週期),由於輪詢的開銷加上設定和捕獲中斷,則較無效率。純輪詢在等待時間非常短的情况下最好。 中斷在已知的長等待時間下是最好的。

12.5 How does DMA increase system concurrency? How does it complicate hardware design?

DMA系統通過系統和記憶體匯流排傳輸數據時,允許CPU執行任務,從而提高系統並行性。硬體設計很複雜,因為DMA控制器必須結合到系統中,並且系統必須允許DMA控制器成為匯流排主控。為了允許CPU和DMA控制器共享記憶體匯流排的使用,可能還需要進行週期竊取

12.6 Why is it important to scale up system-bus and device speeds as CPU speed increases?

考慮一個執行50%I/O和50%計算的系統。 加倍該系統上的CPU效能將僅新增50%的總系統性能。 將兩個系統方面都加倍將新增效能提高100%。 通常重要的是消除當前的系統瓶頸,而不是盲目地提高單個系統組件的效能。

12.7 Distinguish between a driver end and a stream module in a STREAMS operation

驅動程式尾端控制實體設備可能包含在STREAMS操作。 串列模組在資料串列標頭與驅動程式間修改流動資料。

12.8 What are the advantages and disadvantages of supporting memorymapped I/O to device-control registers?

优点:

不需要指令集中的特殊指令,因此不需要执行保护规则;

缺点:

内存转换单元需确保郁设备控制寄存器相关的内存地址不被用户程序访问

12.9 In most multiprogrammed systems, user programs access memory through virtual addresses, while the operating system uses raw physical addresses to access memory.What are the implications of this design for the initiation of I/O operations by the user program and their execution by the operating system?

用戶程序通常指定一個緩衝區,用於向設備傳輸或從設備讀取數據。這個緩衝區存在於用戶空間,有一個虛擬地址指定。核心需要發出I/O操作,並在I/O之前或之後在用戶緩衝區和它自己的核心緩衝區之間複製數據。為了訪問用戶緩衝區,核心需要將用戶提供的虛擬地址轉換為相應的實體地址

12.10 Describe three circumstances under which blocking I/O should be used. Describe three circumstances under which nonblocking I/O should be used. Why not just implement nonblocking I/O and have processes busy-wait until their devices are ready?

通常,阻隔I/O適合行程等待特定事件。 例如由應用程序讀取包括磁片、磁帶或鍵盤。 無阻塞I/O在I/O可能來自多個來源和I/O到達的順序不是預先確定時很有用。 例如包括網絡守護程序偵聽多個網絡插座,窗口管理員接受滑鼠移動和鍵盤輸入,以及I/O管理程序,例如在I/O設備之間複製資料的複製指令。 在最後一種情况是,該程式可以通過緩衝輸入和輸出並使用非阻塞I/O保持兩個設備完全占用來優化其效能。無阻塞I/O對於程式師來說更加複雜,程式可以通過緩衝輸入和輸出,並使用非阻塞I/O保持兩個設備完全佔用無阻塞I/O對於程式師來說更加複雜,因為當I/O發生時需要非同步會合。 此外,忙碌等待比中斷驅動I/O效率低,因此總體系統性能會降低。

12.11 Some DMA controllers support direct virtual memory access, where the targets of I/O operations are specified as virtual addresses and a translation from virtual to physical address is performed during the DMA. How does this design complicate the design of the DMA controller? What are the advantages of providing such functionality?

直接存取虛擬記憶體允許設備從兩個記憶體映射設備轉換,無需CPU干預或使用主記憶體作為中繼站; 設備簡單地向目標設備的記憶體映射地址發出記憶體操作且隨後虛擬位址轉換確保數據被傳輸到適當的設備。 然而,這種功能的代價是必須支持虛擬位址轉換DMA控制器訪問的地址,並且需要添加將位址轉換單元連接到DMA控制器。位址轉換導致硬體和軟件成本,並且還可能導致由CPU維護用於位址轉換的資料結構與DMA控制器使用的相應結構之間的一致性問題。 這些一致性問題也需要處理,這將導致系統進一步增加複雜性。

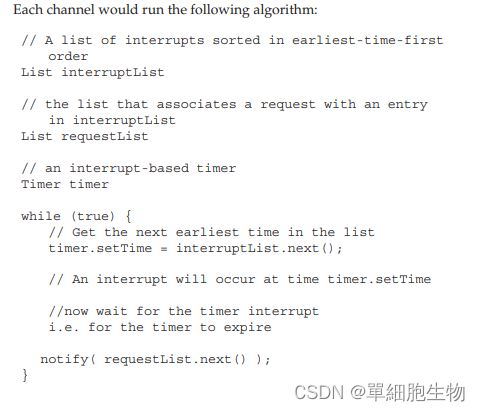

12.12 Write (in pseudocode) an implementation of virtual clocks, including the queueing and management of timer requests for the kernel and applications. Assume that the hardware provides three timer channels.