USB 3.0规范中译本 第6章 物理层

本文为CoryXie原创译文,转载及有任何问题请联系cory.xie#gmail.com。

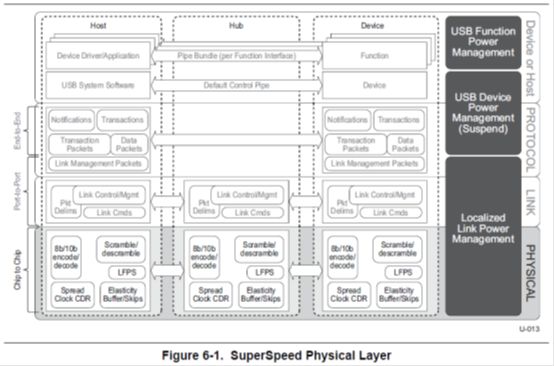

6.1 物理层概览

物理层定义超高速总线的信号技术。本章定义超高速物理层的电气要求。

本节定义超高速组件之间互操作所要求的电气层参数。强制性规范(Normative specifications)是必须要求的(required)。参考性规范(Informative specifications)可以帮助产品设计者和测试者理解超高速总线的预期行为(intended behavior)。

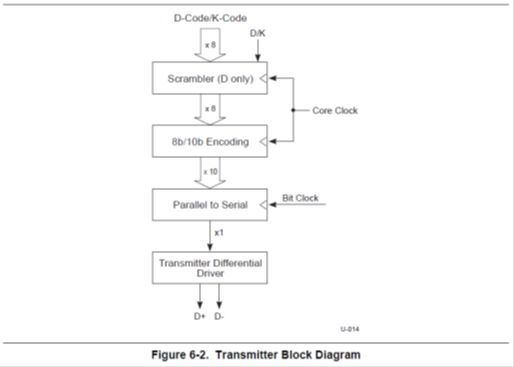

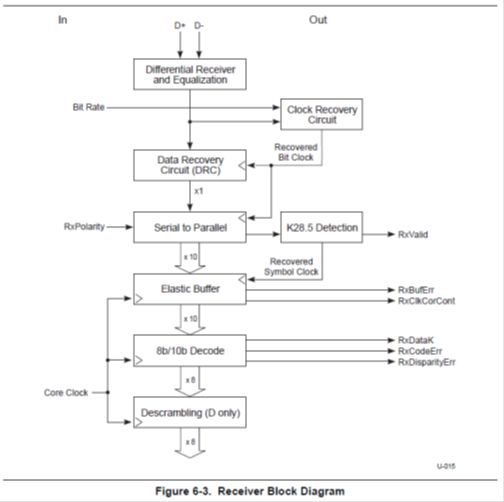

6.2 物理层功能

物理层功能在图6-2, 图 6-3, 以及图 6-4中显示。

6.2.1 测量概览

强制性(normative)超高速眼图(eye diagram)要通过兼容性通道(代表一个长通道,一个短通道以及一条3米线缆的总和)来测量。这要求3个独立的兼容性测试。这些参考通道(reference channels)在USB SuperSpeed Compliance Methodology白皮书中描述。眼图是使用第6.5.2节中描述的时钟恢复函数(clock recovery function)测量的。

对于长通道(long channel)的情形,眼图在接收端是完全关闭的。在第6.8.2节提供了一个参考性(informative)接收器均衡函数(receiver equalization function),其对兼容性通道(compliance channel)做了优化,被用来打开接收器眼睛(open the receiver eye)。

这一方法学允许芯片制造商将通道和元件作为匹配对(matched pair)来设计。期望芯片元件有(用户)必须遵循的布线导引(layout guidelines),以便满足总体规范(overall specification)以及在兼容性通道末端的眼图(eye diagram at the end of the compliance channel)。

注意同时的(simultaneous)USB 2.0和超高速(SuperSpeed)操作是一个兼容性测试要求。

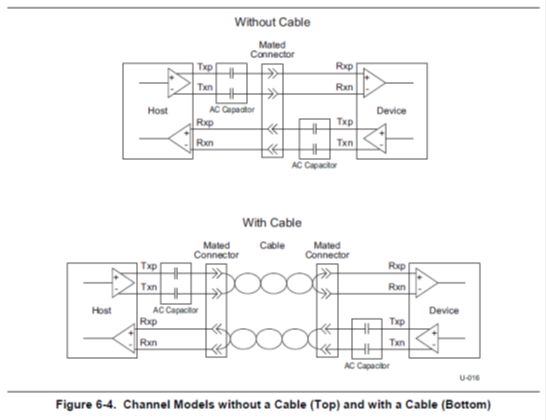

6.2.2 通道概览

PHY是在一起操作(operate together)的发射器(transmitter)和接收器(receiver)的组合,并且位于同一元件内部。一个通道连接两个PHY,具有两个单向差分对(unidirectional differential pairs),总共4条线的管脚。要求PHY是AC耦合的。AC耦合电容与发射器关联在一起。

6.3 符号编码(Symbol Encoding)

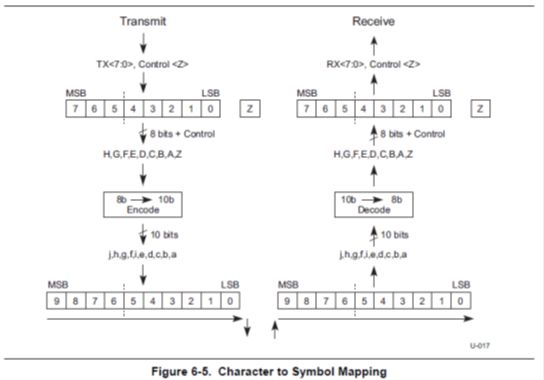

超高速使用8b/10b传输码(transmission code)。这个传输码(transmission code)的定义同ANSI X3.230-1994第11部分相同(同时参考ANSI INCITS 230-1994)。正如图6-5所示,ABCDE 映射为abcdei,而FGH映射为fghj。

【勘误:上图中MSB和LSB实际应该是MSb和LSb】

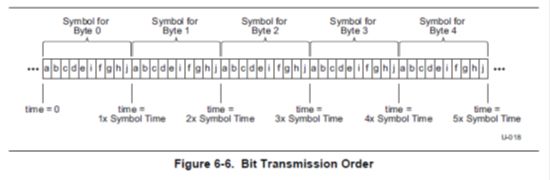

6.3.1 数据序列化和反序列化(Serialization and Deserialization)

一个符号(Symbol)的比特位被以比特"a"开始,并以比特"j"结束。这在图6-6中显示。

6.3.2 强制性8b/10b 解码规则(Normative 8b/10b Decode Rules)

1. 在处于电气空闲(Electrical Idle)状态之后,发射器被允许在首次发送差分数据时选取任何不均等性(pick any disparity)。发射器应该接着遵循适当的编码规则,直到下次进入电气空闲状态(Electrical Idle)。

2. 接收器(Receiver)的初始不均等性是用来获取符号锁(Symbol lock)的第一个符号(Symbol)的不均等性(disparity)。

3. 如果符号锁(Symbol lock)在传送差分信息的过程中因一个突发错误事件(burst error event)而丢失又重新获取了(lost and regained),则不均等性(Disparity)可以被重新初始化。

4. 在初始不均等性(initial disparity)被设置之后接收到的所有后续符号都应该在相应于当前运行不均等性(running disparity)的恰当列中。

5. 接收不均等性误差(Receive disparity errors)不会直接导致链路重新训练。

6. 如果不均等性误差(disparity error)或者8b/10b解码误差(8b/10b Decode error)被检测到了,物理层应该通知链路层。

6.3.3 数据加扰(Data Scrambling)

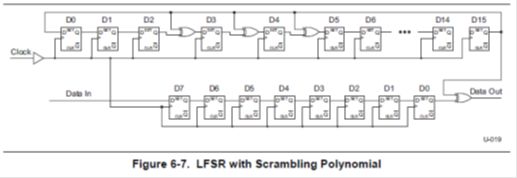

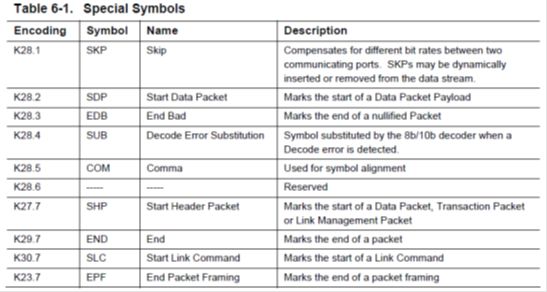

加扰函数(scrambling function)是使用自由运行的线性反馈移位寄存器【Linear Feedback Shift Register (LFSR)】实现的。在发射方,对字符的加扰应用在8b/10b编码之前。在接收方,对字符的解扰应用在8b/10b解码之后。每当发送或者接收到COM符号,LFSR就被重置。【译注:关于COM符号,见表6-1的特殊符号,用于符号对齐】

图6-7以图形化的方式展示了LFSR。加扰或者解扰是通过将8比特字符(D0-D7)与LFSR输出的16比特(D0-D15)串行(serially)相异或。LFSR的一个输出,D15,被与要处理的数据的D0相异或。LFSR和数据寄存器接着被串行地步进(serially advanced),进而输出处理从D1到D7进行重复。LFSR在数据被异或之后才被步进。

用于通知物理层禁掉加扰的机制是实现特定的,超出了本规范的范围。

数据加扰规则如下:

1. LFSR实现如下多项式: G(X)=X16+X5+X4+X3+1

2. 对于每个符号(Symbol)而言,除了SKP之外,LFSR值都应该被步进8个串行移位。

3. 所有的8b/10b D-码,除了位于训练序列有续集(Training Sequence Ordered Sets)之内的,都应该被加扰。

4. K-码不应该被加扰。

5. LFSR种子(D0-D15)的初始值应该是FFFFh。在COM离开发送器LFSR之后,发送端的LFSR应该被初始化。每当COM进入接收器LFSR时,接收端LFSR应该被初始化。这也适用于回环模式(loopback mode)期间的BRST(测试复位)序列(见第6.8.4.1节)。【译注:关于COM符号,见表6-1的特殊符号,用于符号对齐】

---------------------------------------------------------------------------------------------

实现注意(IMPLEMENTATION NOTE)

禁用加扰(Disabling Scrambling)

禁用加扰(Disabling scrambling)意图在于帮助简化测试和调试设备。控制精确的数据模式(data patterns)在测试和调试环境中很有用。由于加扰是在物理层复位的,通过软件没有较合理的方式(reasonable way)来可靠地控制数据转换的状态(state of the data transitions)。禁用加扰位(Disabling scrambling bit)在训练序列中被提供,以用于此目的。用于通知物理层禁用加扰的机制和/或接口是元件特定于具体实现的,超出了本规范的范围。【译注,关于Disabling scrambling bit,请参考表6-5,链路配置字段】

---------------------------------------------------------------------------------------------

关于加扰的更多信息,请参考附录B。

6.3.4 8b/10b解码错误(Decode Errors)

当接收到的符号(received Symbol)与附录A中列出的任意有效符号都不匹配时,将会产生8b/10b解码错误(Decode error)。 任何接收到的不能与附录A中列出的8b/10b符号相匹配的8b/10b符号都应该通过被替代为一个K28.4符号而转发给链路层(forwarded to the link layer by substituting a K28.4 symbol)(参考表6-1)。8b/10b错误可以不(may not)直接导致发起恢复(Recovery)。

6.3.5 用于分帧(Framing)和链路管理(Link Management)的特殊符号

8b/10b编码机制(encoding scheme)提供与代表字符的数据符号(Data Symbols)相区分的特殊符号(Special Symbols)。这些特殊符号(Special Symbols)被用于各种链路管理(Link Management)机制(后面将会描述这些机制)。表6-1列出了所用的特殊符号,并且每一个都给出了简要的描述。特殊符号必须遵循恰当的8b/10b不均等性规则(disparity rules)。在USB SuperSpeed Compliance Methodology白皮书中定义了兼容性测试。

6.4 链路初始化和训练(Link Initialization and Training)

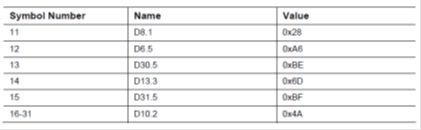

本节定义用于配置和初始化(configuration and initialization)的序列(sequences)。该序列用于对下列功能的初始化状态机(Initialization State Machine)(参考第7章):

• 配置和初始化链路(Configuring and initializing the link)

• 比特锁和符号锁(Bit-lock and symbol lock)

• Rx均衡训练(Rx equalization training)

• 巷道极性反转(Lane polarity inversion)

训练序列(Training sequences)由用于初始化比特对齐(bit alignment),符号对齐(Symbol alignment)以及优化均衡(optimizing the equalization)的有续集(Ordered Sets)组成。训练序列有续集(Training sequence Ordered Sets)绝不会被加扰,但是总会被8b/10b编码。

比特锁(Bit lock)是指时钟/数据恢复电路【Clock/Data Recovery (CDR) circuit】将相位和频率信息从输入数据流中提取出来的能力。比特锁(Bit lock)是通过发送足够长的比特序列(包含交替变换的0和1的D10.2符号),以便CDR粗略地将时钟定位在比特中间(roughly centers the clock within the bit)而实现的。

一旦CDR恰当地恢复了数据比特位,下一步就是定位一个10比特符号的起始和结束。为此,从8b/10b码中选出特殊的叫做COMMA的K-码(K-Code)。COMMA码的比特模式(bit pattern)是唯一的(unique),因此从来不会在其他数据模式(data pattern)中找到,包括D-码跟其它D-码(D-Code appended to any other D-Code)或者D-码跟K-码(D-Code appended to any K-Code)的任何组合。这适用于编码的任意极性。唯一的例外是包含有一个比特错误的各种比特模式(various bit patterns that include a bit error)。

训练序列 (TS1 或 TS2) 被连续传送,且只能被SKP有续集在有续集之间出现时所中断(在连续的TS1集之间,连续的TS2集之间,或者当TS1跟着TS2时(在它们之间))。

6.4.1 强制性训练序列规则(Normative Training Sequence Rules)

训练序列(Training sequences)由用于初始化比特对齐(bit alignment),符号对齐(Symbol alignment)以及接收器均衡(receiver equalization)的有续集(Ordered Sets)组成。

下面的规则适用于训练序列:

• 训练序列有续集(Training sequence Ordered Sets)应该被8b/10b编码。

• 传送TS1或TS2有续集不应该被SKP有续集中断。SKP有续集应该在任何TS1或TS2有续集完成之前或者之后插入。

• 在整个TSEQ时间内(65,536个有续集),不能有SKP有续集传送。

这就意味着PHY必须比在通常操作下对弹性缓冲(elasticity buffer)进行不同的管理。

在第7章可以找到关于使用TSEQ, TS1, 以及TS2有续集的更多信息。

6.4.1.1 训练控制位(Training Control Bits)

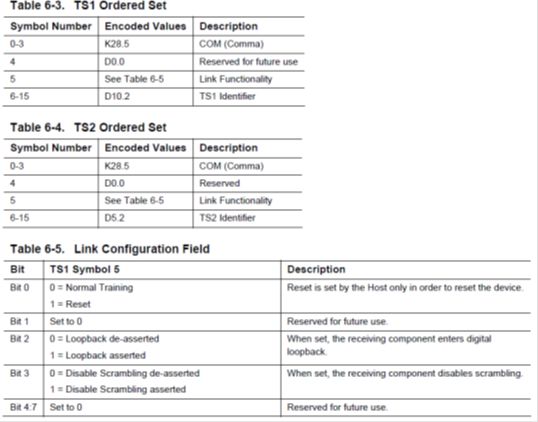

训练控制位(training control bits)存在于TS1和TS2有续集中的链路功能性符号(Link Functionality symbol)中。它们被在表6-5中描述。

链路配置字段(link configuration field)的比特0和比特2不能同时被设置为1。如果接收器在接收到的链路配置字段(link configuration field)中检测到这一情形,那么所有的训练控制位(training control bits)都将会被忽略。

6.4.1.2 训练序列值(Training Sequence Values)

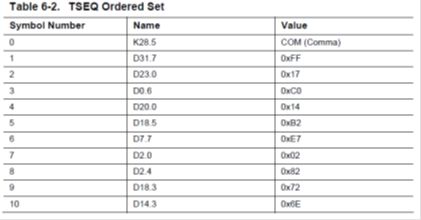

TSEQ训练序列重复65,536次,以允许测试多个系数设置(coefficient settings)。

6.4.2 巷道极性反转(Lane Polarity Inversion)

在TSEQ训练序列期间,接收器必须使用TSEQ有续集中的D10.2符号(D10.2 Symbol)来判定巷道极性反转(lane polarity inversion)(即Rxp和Rxn被交换)。如果发生了极性反转,TSEQ有续集中的D10.2符号会被接收为D21.5,而不是D10.2,从而接收器必须反转接收到的位极性。这必须在TSEQ符号1-15被使用(来做极性反转判断)之前完成,因为这些符号在8b/10b域内并不是全都在反转情况下对称(not all symmetric under inversion in the 8b/10b domain)。如果接收器不使用TSEQ训练序列,那么极性反转应该针对TS1有续集的D10.2符号作检查。

6.4.3 弹性缓冲和SKP有续集(Elasticity Buffer and SKP Ordered Set)

超高速体系结构支持在超高速链路的两端都有独立的参考时钟。每个参考时钟的精确度要求在+-300 ppm以内。这就给出了链路两端的两个设备的最大频率差异为+- 600 ppm。此外,SSC产生具有最大差异为5000 ppm的频率变动(frequency delta)。频率变动(frequency delta)的总体幅度可以在-5300 到 300 ppm范围内。这个频率变动由消耗或者插入SKP有续集的弹性缓冲来管理。【译注:ppm,parts per million,即百万分之一。关于ppm的概念,参考附加文档<Clock accuracy in ppm>】

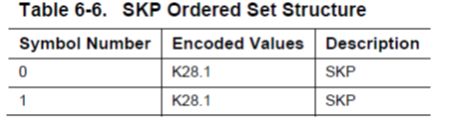

SKP有续集应该被用来补偿链路两端的频率差异。发送器平均每354个符号发送SKP有续集。SKP有续集不应该插入任何包中。发送器被允许缓冲最多4个SKP有续集。接收器必须实现能够缓冲(buffering)(或者挨饿(starving))数据的8个符号。

SKP规则【SKP Rules (Host/Device/Hub)】:

• SKP有续集应该由一个SKP K-符号紧跟一个SKP K-符号组成。一个SKP有续集代表两个符号,可用于时钟补偿。【已勘误】

• 设备必须维护一个自从上一个SKP有续集开始已经传送了的符号的运行计数(running count)。这个计数值将被称为Y。每当发送器进入Polling.Active时,或者退出U1/U2/U3 低功耗状态时,Y值被重置复位。

• 除非特别指出,在发送完TS1, TS2有续集,LMP,TP,DP,或者逻辑空闲(Logical idle)之后,发送器应该立即插入Y/354计算的整数结果有续集(the integer result of Y/354 calculation Ordered sets)。只有在训练中,发送器被允许在Y/354的整数结果达到2时,可以选择等待插入2个SKP有续集。发送器不应该在任何其他时候传送SKP有续集。

注意:SKP计算中,Y/354的非整数余数不应该被丢弃掉,而应该被用于调度下一个SKP有续集的计算中。

• 在对有续集(即,在Polling 和 Recovery中的连续的TS1,TS2有续集)进行监控时,SKP命令(SKP Commands)不被作为中断(interruptions)计数。

6.4.4 兼容模式(Compliance Pattern)

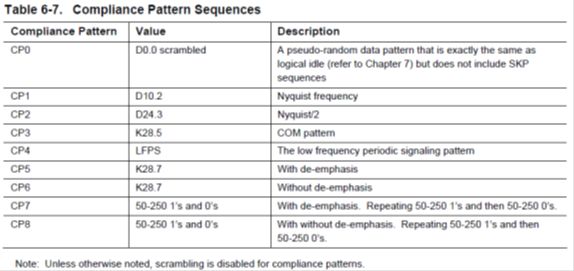

在第7章描述兼容模式(Compliance Mode)的进入【已勘误】。这就启动了对加扰后的D0.0兼容性序列(scrambled D0.0 compliance sequence)所生成的伪随机数据模式(pseudo-random data pattern)的传送【已勘误】。在兼容性模式(compliance pattern)过程中,不发送SKP。兼容性模式(compliance pattern)应该被连续传送,或者直到在接收器端检测到一个ping LFPS(参考第6.9节)为止。一旦检测到一个ping LFPS,(当前)兼容性模式应该步进到下一个兼容性模式。一旦检测到复位(reset),兼容性模式就应该被终止(terminated)【已勘误】。兼容性模式(compliance pattern)序列在表6-7中描述。

6.5 时钟和抖动(Clock and Jitter)

6.5.1 参考性抖动裕量(Informative Jitter Budgeting)

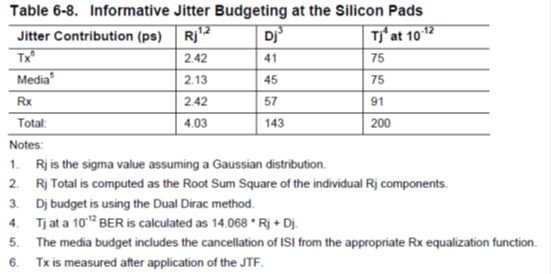

针对USB 3.0的抖动,在组成端到端连接的原件之间做出了预算:发送器,通道(包括封装,连接器和线缆),以及接收器。抖动裕量是从芯片焊盘(silicon pads)处导出。Dj分布(Dj distribution)采用双狄拉克式方法(dual Dirac method)。表6-8列出了Tx, Rx,以及通道抖动裕量。【译注,关于Dual Dirac方法,参见文档< What the Dual-Dirac Model is and What it is Not >以及< Jitter Analysis - The dual-Dirac Model, RJ-DJ, and Q-Scale >】

注意:系留线缆(Captive cables)必须满足第5.6.1.2节中的成对(mated)连接器规范。但是系留线缆不被认为是独立的组件。为了满足电气裕量的目的,系留线缆被认为是设备的一部分,因此必须满足表6-8中设备的抖动要求。

【译注:Captive cable 即与设备不可分离的电缆。这种线缆一端是插头,另一端是非标准的连接方式(分为hardwire或customize两种情况)。】

6.5.2 强制性时钟恢复函数(Normative Clock Recovery Function)

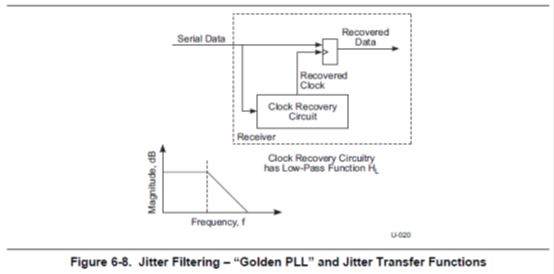

Tx相位抖动(Tx Phase jitter)的测量是通过使用标准时钟恢复方法完成的,显示于图6-8中。关于golden PLL测量的信息,请参考最新版的INCITS TR-35-2004, INCITS Technical Report for Information Technology – Fibre Channel – Methodologies for Jitter and Signal Quality Specification (FC-MJSQ).

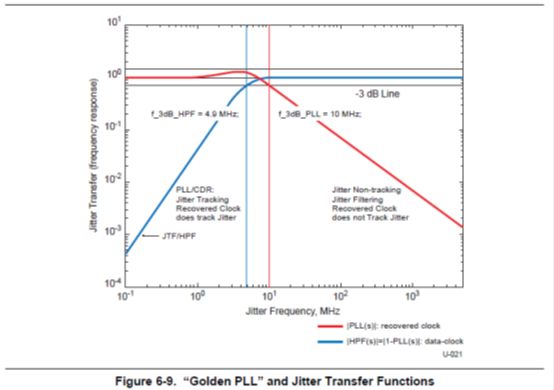

时钟恢复函数(clock recovery function)在等式1-3中给出。正如所示,时钟恢复电路具有低通响应(low pass response)特性。在恢复的时钟与数据相比较(相减)后,总体时钟恢复变成一个高通函数(high pass function)。这在图6-9中显示。

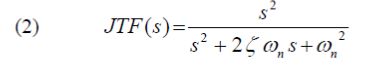

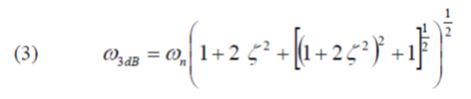

这些函数的等式如下:

以及

其中ωn 是自然频率(natural frequency),ξ 是阻尼系数(damping factor)。 与3dB频率的关系如下:

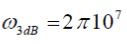

正如图5-7所示,拐角频率(corner frequency)  以及

以及 。这个传输函数(Transfer Function)具有2 dB最大峰值(maximum peaking)。

。这个传输函数(Transfer Function)具有2 dB最大峰值(maximum peaking)。

6.5.3 强制性扩频时钟【Normative Spread Spectrum Clocking (SSC)】

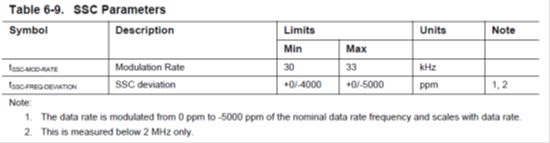

所有端口都要求具有扩频时钟调制【Spread Spectrum Clocking (SSC) modulation】。允许给两个不同元件提供相同SSC时钟,但不是必需的,SSC可以是异步生成的。没有指定的SSC配装(SSC profile),这是厂商特定的。SSC调制的要求列于表6-9。SSC调制不能违反在第6.5.4节中描述的相位转换速率(phase slew rate,也即相位斜率)。

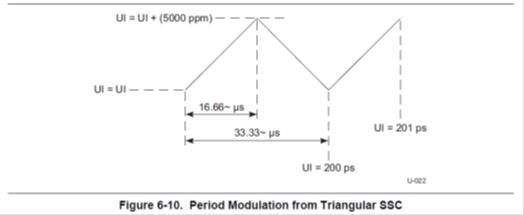

图6-10中显示了一个来自三角SSC的周期调制(period modulation from triangular SSC)的示例。

6.5.4 强制性转换斜率限制(Normative Slew Rate Limit)

CDR是一个转换斜率受限的相位跟踪设备(slew rate limited phase tracking device)。SSC和其他在CDR带宽范围内的抖动源的组合必须不超过最大可允许的转换斜率。

执行这一测量是通过使用CDR转换函数滤除相位抖动(filtering the phase jitter with the CDR transfer function),并选取相位抖动的首个误差来获取过滤后的周期抖动(taking the first difference of the phase jitter to obtain the filtered period jitter)。周期抖动的峰值必须不能超过表6-10列出的TCDR_SLEW_MAX。

在USB 3.0 Jitter Budgeting中有关于转换斜率测量的更多细节。

6.6 信号(Signaling)

6.6.1 眼图(Eye Diagrams)

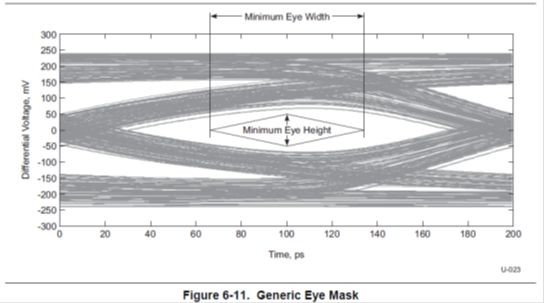

眼图(eye diagrams)是信号的电压和时间限制(voltage and time limits of the signal)的图形化表示。在应用了恰当的抖动传输函数(jitter transfer function)和参考接收器均衡(reference receiver equalization)之后,这一眼图波罩(eye mask)应用于抖动(applies to jitter)。在所有情况下,眼睛(eye)都要被测量106个连续的UI(consecutive UI)。链路的裕量是假设总共10-12比特误差率,且在假设随机抖动符合高斯规律(Gaussian)的情况下,推论(extrapolated)到对106个UI的测量而获得的。【译注:UI即Unit Interval,单位时间间隔,对于5Gbps,长度为200ps。】

图6-11显示了对所有眼图测试都使用的眼图波罩(eye mask)。参考该图,时间是从Txp/Txn的交叉点测量的。时间叫做眼宽度(eye width),而电压是眼高度(eye height)。眼高度(eye height)要在张开最大处测量(在眼宽度的中间± 0.05 UI)。

眼图要使用抖动传输函数【jitter transfer function (JTF)】来使之居中。恢复的时钟是从数据中得到的,并由JTF处理。在眼图中,恢复的时钟的中心用于定位数据的中心。

眼图要在50-Ω单端负载(single-ended loads)下测量。

6.6.2 电压级别定义(Voltage Level Definitions)

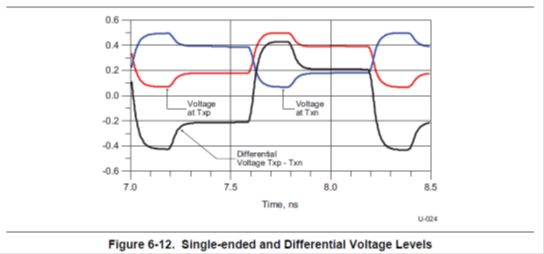

参考图6-12,差分电压,VDIFF,是Txp上的电压(在接收器端的Rxp)相对于Txn上的电压(在接收器端的Rxn)。VDIFF是与一个传导器上的单信号电压摆幅相同的电压(the swing on the single signal of one conductor)。差分电压是:

(4) VDIFF = Txp – Txn

总的差分电压摆幅(differential voltage swing)是差分电压的峰峰值,VDIFF-PP。这是差分电压的两倍。差分电压峰峰值是:

(5) VDIFF-PP=2 * VDIFF

共模电压【Common Mode Voltage (VCM)】是呈现在同一差分对上相对于地的平均电压。这是相对于地,如此测量而得:

(6) VCM = (Txp + Txn) / 2

DC定义为所有频率组件小于FDC = 30 kHz。 AC定义为所有频率组件大于或者等于FDC = 30 kHz。这些定义适合于所有电压和电流规范。

图6-12显示了一个示例波形。在这个波形中,差分电压峰峰值,VDIFF-PP,是800 mV。差分电压,VDIFF,是400 mVPP。注意,尽管Txp和Txn的中心交叉点显示在300 mV,相应的差分电压的跨越点(crossover point)是0.0 V。中央交叉点在300 mV也是共模电压,VCM。注意这些波形包含了解加重(de-emphasis)。依赖于发送器设置,根据图6-10所允许的范围,实际的去加重(de-emphasis)可以改变。

6.6.3 Tx和Rx输入寄生现象(Tx and Rx Input Parasitics)

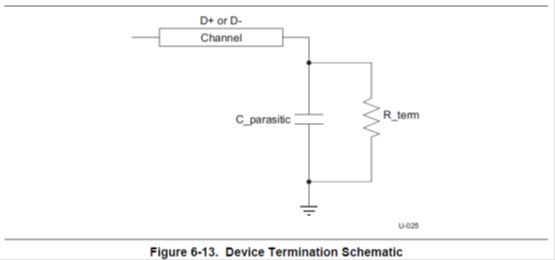

Tx和Rx输入寄生现象(Tx and Rx input parasitics)如图6-13中所指的集总电路(lumped circuit)所示。

在该电路中,输入缓冲被简化为一个与寄生电容并联的终端电阻(termination resistance)。这一简化电路就是负载阻抗(load impedance)。

6.7 发送器规范(Transmitter Specifications)

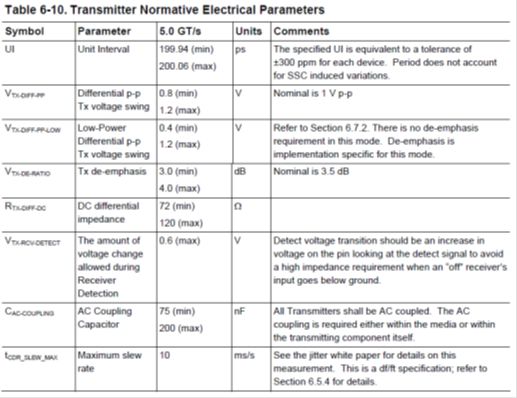

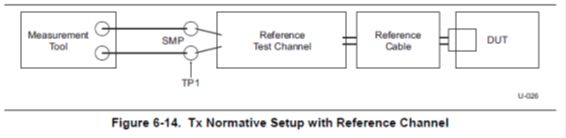

6.7.1 发送器电气参数(Transmitter Electrical Parameters)

峰值【Peak (p)】以及峰峰值【peak-peak (p-p)】定义与第6.6.2节。

表6-11中的值只具有信息参考意义(informative),不是标准必须的(not normative)。 它们被包含在本文档中,以提供在表6-10中用于发送器设计和开发的标准要求(normative requirements)之外的指导。发送器可以与标准要求完全兼容,但不一定满足在这个表中的所有值(在完成的产品中,许多都是不可测量的)。类似地,满足这个表中所有值的发送器并不能保证与本规范的标准要求部分完全兼容。

6.7.2 低功耗发送器(Low Power Transmitter)

除了全摆幅模式(full swing)发送器规范之外,对于超高速应用,还指定了一个可选的低功耗摆幅模式(low power swing)发送器规范。低功耗发送器典型地用于对电源和噪声干扰敏感的系统,并具有相对短的通道。对于是否一个发送器要支持全摆幅模式(full swing),低功耗摆幅模式(low power swing),或者两者都兼顾模式(both swings),这是依赖于使用模型的。所有超高速发送器都必须支持全摆幅模式(full swing),而对低功耗摆幅模式(low power swing)的支持是可选的。本规范没有定义如何选取输出摆幅模式(output swing)的方法,因此是特定与具体实现的。

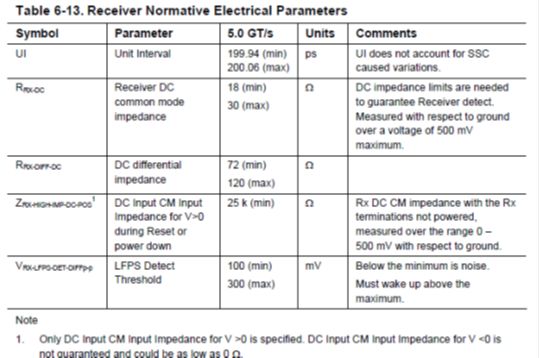

尽管指定了两个不同的发送器规范,只定义有一个接收器规范。这就隐含着,如果使用了低功耗发送器,接收器边界(receiver margins)(如表6-13所指定的)就必须被满足。

6.7.3 发送器眼睛(Transmitter Eye)

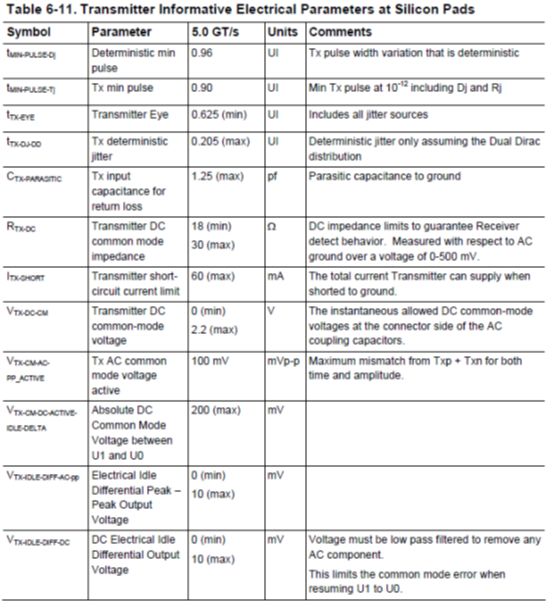

眼图波罩(eye mask)是使用第6.4.4节所描述的兼容性数据模式(DJ用CP0,RJ用CP1)测量得到的。眼高(Eye height)被测量连续106个UI。抖动被推论(extrapolated)是106个UI达到10-12BER。

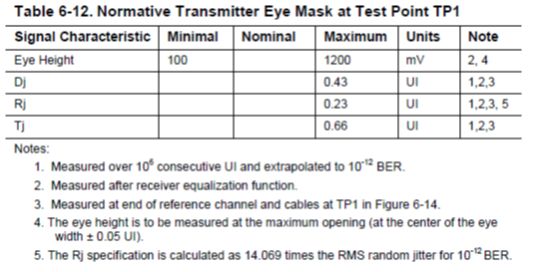

兼容性测试的建立如图6-14。所有的测试都是在测试点(TP1)处进行的,且在使用兼容性参考均衡器传输函数(compliance reference equalizer transfer function)(在下节将描述之)处理测试数据之后,应用了Tx规范。

6.7.4 Tx兼容性参考接收器均衡函数 (Compliance Reference Receiver Equalize Function)

正规性发送器眼睛(normative transmitter eye)是在参考通道的末端捕捉的。在这一点眼睛可能是闭合的。为了使眼睛张开以便可以测量,对信号应用参考Rx均衡器。该参考均衡器的详情在第6.8.2节描述。

6.7.5 参考性发送器去加重(Informative Transmitter De-emphasis)

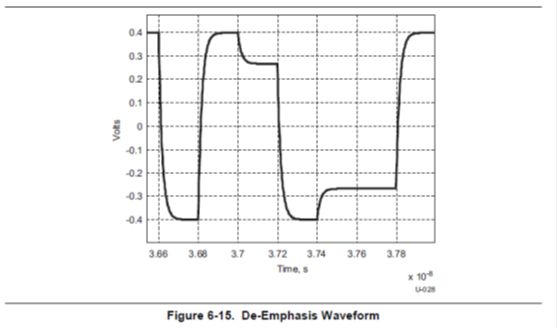

通道裕量(channel budgets)和眼图(eye diagrams)是通过使用对主机和设备参考通道(Host and the Device reference channels)的发送端去加重(transmit de-emphasis)的VTX-DE-RATIO而得到的。差分峰峰去加重(differential peak-to-peak de-emphasis)波形的示例显示于图6-15。

6.7.6 进入电气空闲U1(Entry into Electrical Idle, U1)

电气空闲(Electrical Idle)是一个稳定状态,此时发送器Txp和Txn电压被保持在相同值,且接收器终端(Receiver Termination)处于由ZRX-DC所指定的范围内。电气空闲(Electrical Idle)被用于U1节能模式。

在电气空闲(Electrical Idle)时,低阻抗共模(low impedance common mode)和差分接收器终端阻抗(differential Receiver terminations)值(见表6-13)必须被满足。在电气空闲(Electrical Idle)期间,发送器(Transmitter)可以要么处于低阻抗模式,要么处于高阻抗模式。

6.8 接收器规范(Receiver Specifications)

6.8.1 接收器均衡训练(Receiver Equalization Training)

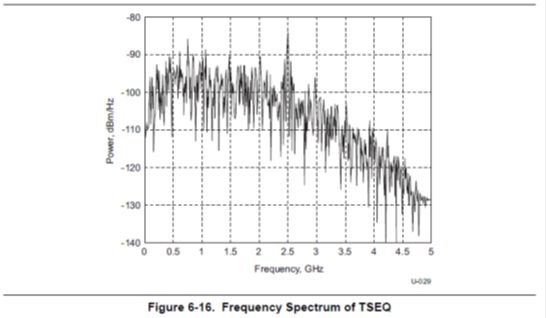

接收器均衡训练序列(receiver equalization training sequence)(详见第6.3.1节),可以用来训练接收器均衡器(receiver equalizer)。TSEQ训练序列(TSEQ training sequence)被设计来提供频谱上(spectrally)丰富的数据模式(data pattern),有益于训练典型的接收器均衡体系(receiver equalization architectures)。此外,在数据中穿插(interleaved)了高边缘密度模式(high edge density pattern),以帮助CDR维持比特锁(bit lock)。TSEQ训练序列(TSEQ training sequence)重复65536次,以允许测试许多系数设置(coefficient settings)。在TSEQ训练序列(TSEQ training sequence)中不会插入SKPs。TSEQ序列(TSEQ sequence)的频谱显示于图6-16。

接收器均衡训练是特定于具体实现的。

6.8.2 参考性接收器CTLE函数(Informative Receiver CTLE Function)

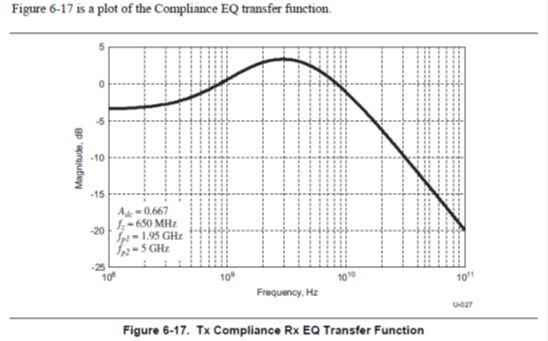

USB 3.0允许使用接收器均衡(receiver equalization)来满足系统时序(timing)和电压(voltage)边界(margins)。对于较长线缆和通道,(眼图的)眼睛在Rx端是闭合的,因此如果不先应用均衡函数的话就没有有意义的(眼图的)眼睛。Rx均衡器(Rx equalizer)可能被要求使用Rx EQ训练周期来适配不同的通道损耗(channel losses)。确切的Rx均衡器(Rx equalizer)和训练方法是特定于具体实现的。

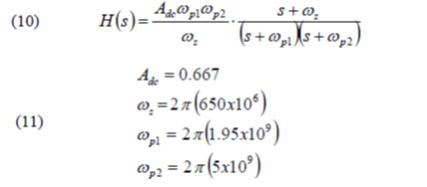

用于开发本规范的连续时间线性均衡器【continuous time linear equalizer (CTLE)】等式是下面描述的兼容性Rx EQ传输函数(compliance Rx EQ transfer function)。

6.8.3 接收器电气参数(Receiver Electrical Parameters)

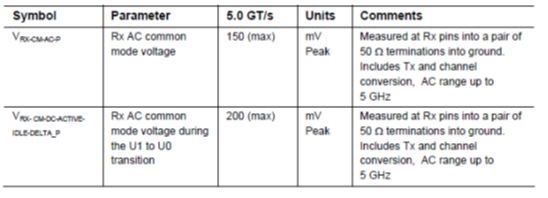

强制性规范(Normative specifications)应在连接器处测试。峰值(p)以及峰峰值(p-p)定义于第6.6.2节。

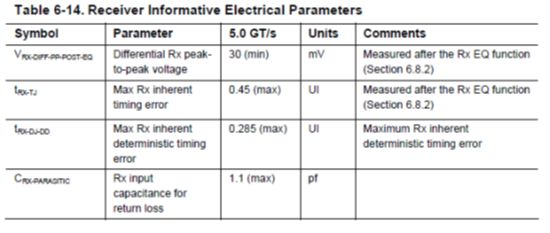

表6-14中的值只是参考性的(informative),不是标准要求的(normative)。它们被包含在本文档中,以提供一些对于表6-13中关于接收器设计和开发的标准要求之外的引导。接收器可以完全兼容与本规范的标准要求,却不满足这个表中的所有值(其中许多在完成的产品中都是不可测量的)。类似的,满足这个表中所有值的接收器也不能保证就完全兼容与本规范的标准部分。

6.8.4 接收器回环(Receiver Loopback)

第7章描述接收器回环(receiver loopback)的进入和退出过程。收器回环(receiver loopback)必须被重新定时(retimed)。在回环模式,从Rx放大器到发送器的直接连接是不允许的。接收器必须继续恰当地处理SKPs。为了合适的时钟容忍补偿(clock tolerance compensation),SKP符号必须按照要求被消耗或者插入。时钟容忍缓冲(clock tolerance buffers)运行过度或者不足(Over runs or under runs)都会重置缓冲到中间位置(neutral position)。在回环期间,接收器必须处理比特误差率测试【Bit Error Rate Test (BERT)】命令。回环必须在10-bit域(10-bit domain)发生。不允许错误校正(error correction)。所有的符号(除了SKP和BERT命令之外),都必须被按照接收到的样子被发送(transmitted as received)。

6.8.4.1 回环BERT(Loopback BERT)

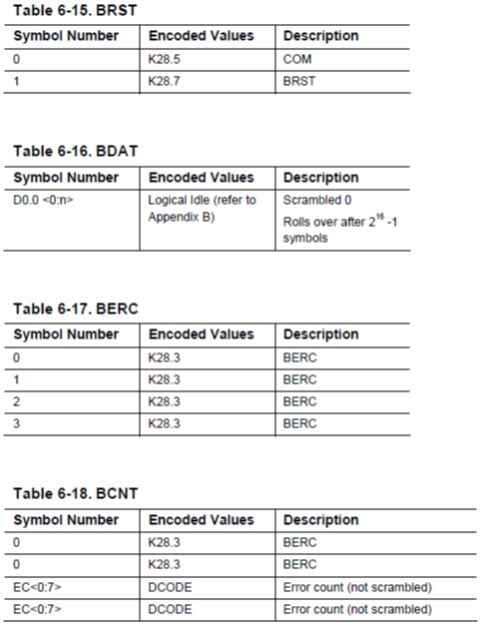

在回环期间,接收器处理BERT有续集(ordered sets)BRST(测试复位), BDAT(开始测试数据), 以及BERC(误码查询)。这些有续集(ordered sets)在表6-15到表6-18中被描述。BRST和BDAT如接收到一样被回环。BERC有续集不是被回环,而是被用BCNT有续集替换。任何时间一旦收到一个BRST,错误计数寄存器EC就被设为0,且加扰LFSR(scrambling LFSR)被设为0FFFFh。任何个数的连续BRST有续集都可能被收到。

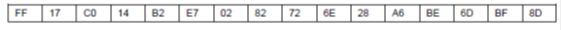

BRST(后面紧跟BDAT)启动比特误差率测试(bit error rate test)。BDAT序列是加扰器(scrambler)的输出,等效于逻辑空闲序列。它由如附录B中所描述的被加扰的0(scrambled 0)组成。如附录B所列出的,该序列的最先16个字符被重新印于此处:

接收器必须将接收到的数据与BDAT序列比较。错误将使得错误计数寄存器(EC)增加1。EC可以不翻转(如果满足翻转条件的话),但是必须被保持在FFh。LFSR除了SKPs之外,对每个字符都要做步进(advanced)。

LFSR在216-1个符号后翻转。为了时钟容忍补偿(clock tolerance compensation),必须在必要时插入或者删除SKPs。

BERC命令不会使错误计数寄存器增加。LFSR会被步进。BERC有续集被BCNT有续集替换。BCNT有续集包含基于运行不均等性(running disparity)的未加扰(non-scrambled)8b/10b编码的错误计数(EC)寄存器。在返回BCNT有续集之后,回环从端(loopback slave)应该继续重复收到的符号。BERC可以被多次发送。EC寄存器不会被BERC有续集清除。

BERT继续直到回环模式被如第7章描述的那样终止。

回环模式BERT的错误计数寄存器以及相关的控制机制是可选的。没有实现回环模式BERT的错误计数的设备将BERC不做修改地回环。

6.8.5 强制性接收器容忍兼容性测试(Normative Receiver Tolerance Compliance Test)

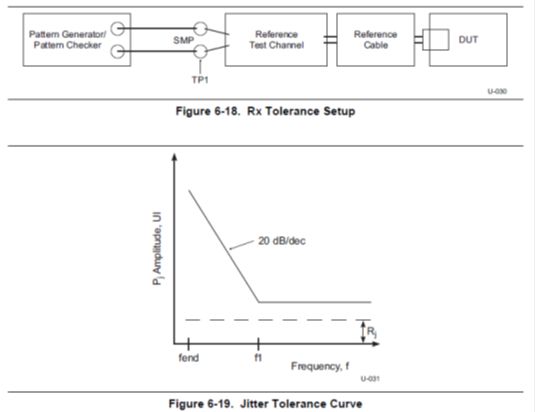

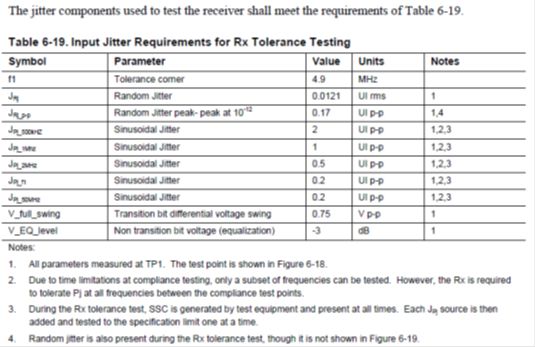

接收器容忍测试(receiver tolerance test)在兼容性参考通道上测试。模式生成器(pattern generator)会通过兼容性参考通道发送一个附加有抖动的兼容性模式给接收器。接收器会回环(loop back)数据,且从模式生成器(pattern generator)和返回的数据间的任何差异(any difference)都会是一个错误。在运行兼容性测试时,接收器应该被置于回环模式(loopback mode)。

更多的关于接收器兼容性测试的详情被包含在参考文档USB SuperSpeed Compliance Methodology中。

6.9 低频周期信号【Low Frequency Periodic Signaling (LFPS)】

低频周期信号【Low frequency periodic signaling (LFPS)】被用于处于低功耗链路状态的链路的两个端口之间进行边带通信(side band communication)。它也被在链路处于训练时,或者下游端口发送热重启(Warm Reset)去重置链路时。

6.9.1 LFPS 信号定义(LFPS Signal Definition)

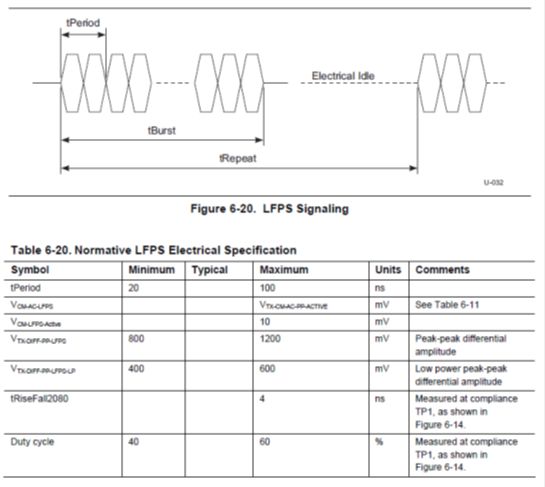

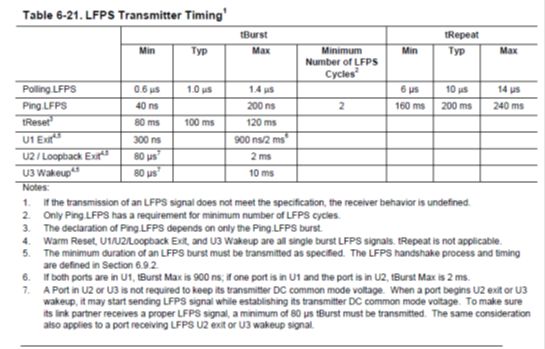

表6-20定义了LFPS在发送器端的规范。图6-20显示了一个示例差分LFPS波形。tPeriod是LFPS循环的周期。LFPS突发(LFPS burst)是在tBurst定义的时间内连续传送LFPS信号。LFPS序列(LFPS sequence)定义为在一段定义为tRepeat的时间内发送时间长度为tBurst的单个LFPS突发。链路在紧邻的(contiguous)LFPS突发之间处于电气空闲(electrical idle)。LFPS消息(LFPS message)基于tBurst的变化(variation of tBurst)进行编码。tRepeat定义为下一个LFPS消息(LFPS message)被传送的时间间隔。LFPS消息(LFPS messages)包含如表6-21定义的Polling.LFPS和Ping.LFPS。还有为U1/U2,以及Loopback exit,U3 wakeup和Warm Reset定义的LFPS信号。

LFPS信号的详细使用在后面几节和第7章指定。

---------------------------------------------------------------------------------------------------------------------

实现注记(IMPLEMENTATION NOTE)

检测并区分对于处于U1或者U2的下游端口的Ping.LFPS以及 U1 LFPS Exit信号

当下游端口处于U1时,它可能从其链路伙伴接收到Ping.LFPS消息来通知其存在,或者接收到U1 LFPS exit信号来告知其链路伙伴正尝试从U1退出。这在下游端口处于U2时也会发生,因为存在这样的情形,当下游端口因U2不活动定时器超时而从U1进入U2时,其链路伙伴仍然还处于U1。

一旦检测到由于接收到LFPS而打破电气空闲时,下游端口可以启动一个定时器来测量LFPS信号的长度(duration)。如果电气空闲情形在定时器300 ns过期时没有发生,下游端口可以申明所接收到的LFPS信号是U1 exit,并通过发送U1 LFPS exit handshake信号来响应该U1 exit。如果在定时器到达300 ns之前检测到了电气空闲,下游端口可以申明所接收到的LFPS信号是Ping.LFPS。

---------------------------------------------------------------------------------------------------------------------

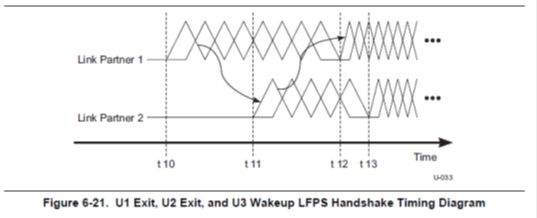

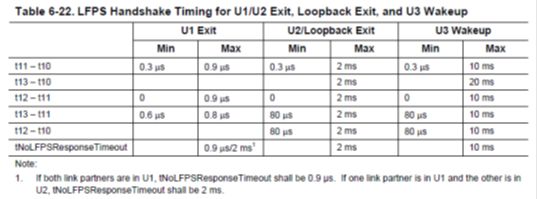

6.9.2 U1/U2 Exit, Loopback Exit, 以及U3 Wakeup的LFPS握手示例

除了表6-22中定义的超时值之外,用于U1/U2 exit, Loopback exit, 以及U3 wakeup的LFPS信号定义与连续LFPS信号相同。对U1/U2 exit以及U3 wakeup的握手过程示于图6-21中。对于U1 exit, U2 exit, Loopback exit, 以及U3 wakeup的时序要求是不同的。它们被列于表6-22中。

注意:图6-21中的时序图仅仅是用于说明LFPS握手过程。

握手过程如下:

• 链路伙伴1通过在t10传送LFPS而发起退出(见图6-21)。LFPS的传送一直持续到握手被申明要么成功或者失败为止。

- 链路伙伴2在接收器检测到有效的LFPS,并在时间t11传送LFPS作出响应。LFPS的传送一直持续到握手被申明要么成功或者失败为止。

• 如果在t10后的"tNoLFPSResponseTimeout"时间内下面的条件被满足,则对链路伙伴1申明成功的握手(见图6-21和表6-22):

1. 从链路伙伴2接收到有效的LFPS。

2. 对于U1 exit, U2 exit, U3 Wakeup且不是Loopback exit,链路伙伴1准备好传送训练序列,且在LFPS发送器停止传送之后,以及超高速发送器开始传送之前,最大时间空隙是20ns。

注意:对于超高速发送器和接收器没有近端串扰【Near End Cross Talk (NEXT)】规范。因此,当端口进入恢复(Recovery)并开始传送TS1有续集而其链路伙伴在成功LFPS握手后处于空闲,由于NEXT,端口潜在地可以使用自己的TS1有续集来训练其接收器。添加第二个退出条件的意图是为了防止端口在转换到恢复(Recovery)之前进入电气空闲(electrical idle)。

• 如果在t11后的"tNoLFPSResponseTimeout"时间内下面的条件被满足,则对链路伙伴2申明成功的握手:

1. 链路伙伴2已经传送了在表6-22中定义的最小LFPS,即 (t13 – t11)。

2. 对于U1 exit, U2 exit, U3 Wakeup且不是Loopback exit,链路伙伴2准备好传送训练序列,且在LFPS发送器停止传送之后,以及超高速发送器开始传送之前,最大时间空隙是20ns。

• 如果成功握手的条件没有被满足,则应该申明响应的U1 exit, U2 exit, Loopback exit, 以及U3 wakeup握手失败。

- 如果成功握手的条件没有被满足,链路伙伴1应该申明一个失败的握手。

- 如果成功握手的条件没有被满足,链路伙伴2应该申明一个失败的握手。

注意:除了Ping.LFPS,当处于Ux或者Loopback.Active的上游端口接收到一个LFPS信号时,它应该继续进行U1/U2 exit, 或者U3 wakeup, 或者Loopback exit握手,即使该LFPS后来被判定为一个Warm Reset。如果该LFPS就是一个Warm Reset,如果一个上游端口处于Ux,将进入恢复(Recovery),并最后超时进入SS.Inactive;或者(如果一个上游端口)处于Loopback Active,则会进入Rx.Detect并接着转换到Polling.LFPS。当检测到Warm Reset,上游端口会进入Rx.Detect。

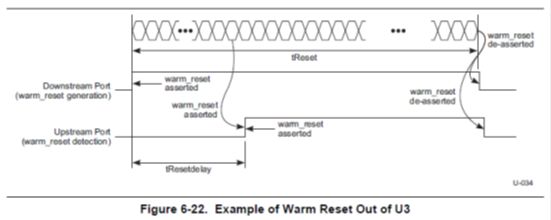

6.9.3 Warm Reset

一个Warm Reset是一个仅由下游端口(downstream port)向一个上游端口(upstream port)生成的复位(reset)信号。下游端口可以在除了SS.Disabled之外的任何链路状态下发起一个Warm Reset。上游端口被要求要能够在除了SS.Disabled之外的任何链路状态下检测到Warm Reset。

一个Warm Reset共享相同的连续LFPS信号,将其作为低功耗链路状态退出握手(low power Link state exit handshake)信号。为了使得一个上游端口能够区分开这两个信号,Warm Reset的tBurst被扩展了,正如表6-20所定义的。

Warm Reset的有效(assertion)在下游端口和上游端口之间是异步的(asynchronous),因为必须要一段时间让上游端口申明检测到了Warm Reset。然而,Warm Reset在下游端口和上游端口之间的无效(de-assertion)必须是同步的。图6-22显示了当一个端口处于U3时, Warm Reset的时序图的生成和检测。一旦一个Warm Reset被下游端口发送,就至少需要tResetDelay来使得一个上游端口来申明检测到了Warm Reset。一旦检测到Warm Reset,上游端口必须继续使Warm Reset有效,直到不再从下游端口接收到任何LFPS信号。

• 一个上游端口应该在tResetDelay时间内申明检测到Warm Reset。tResetDelay 最小应该是18 ms;tResetDelay 最大应该是50 ms 。

6.10 发送器和接收器DC规范

6.10.1 参考性ESD保护(Informative ESD Protection)

所有的信号和电源管脚必须能忍受(withstand)使用依据JEDEC JESE22-A114-A的Class 2的ESD 2000 V人体模型,以及使用依据JEDEC JESD22-C101D的CLASS III的充满电的ESD 500 V设备模型的,而不造成破坏(damage)【已勘误】。这个ESD保护机制也帮助保护电源关闭的接收器(powered down Receiver),以免在某些可能的复位(reset)和意外插入(surprise insertion)条件下出现潜在的共模瞬变(potential common mode transients)。

6.10.2 参考性短路要求(Informative Short Circuit Requirements)

所有的发送器(Transmitters)和接收器(Receivers)都必须支持意外热插入/拔出而不造成对元件的破换。发送器(Transmitters)和接收器(Receivers)必须能够容忍Txp (Rxp) 以及 Txn (Rxn)到地的持续(sustained)短路电流。

6.10.3 强制性高阻抗反射(Normative High Impedance Reflections)

在异步复位事件(asynchronous reset event)期间,一个设备可能在另一个设备正在传输时被复位。被复位的设备被要求断开接收器终端阻抗(disconnect the receiver termination)。在此期间,被复位的设备可能正在接收活跃的数据。由于数据没有被终结,进入接收器的差分电压(differential voltage)将会翻倍(doubled)。对于一个短通道,接收器可能经受总共2* VDIFF。

接收器必须容忍这一在Rx终端阻抗被断开时的负电压(doubling of the negative voltage)的翻倍(doubling)的情形。元件(part)必须承受在其终生的时间内(over the life time)终端阻抗被断开10,000次,且每次时长20 ms的接收器输入端电压翻倍的事件。

6.11 接收器检测(Receiver Detection)

6.11.1 Rx检测概览(Rx Detect Overview)

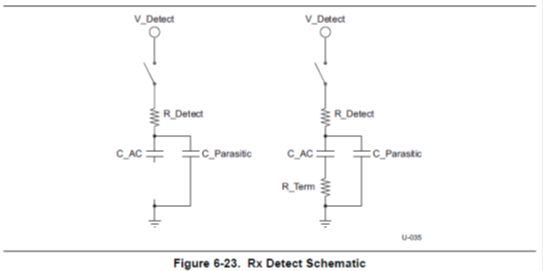

接收器检测电路(Receiver Detection circuit)是作为发送器(Transmitter)的一部分实现的,且必须正确检测出是否存在与直流阻抗RRX-DC (表6-13)相等效的负载阻抗(load impedance)。 Rx检测(Rx detection)是基于电路的RC时间常量(RC time constant)的原理操作的。这一时间常量根据是否存在接收器终端阻抗而改变。这在图6-23中作出了概念性的说明。在此图中,R_Detect是特定于具体实现的充电电阻(charging resistor)。C_AC是AC电容,它只有当R_Term存在时才在电路中存在,否则,只有C_Parasitic存在。

图6-23的左侧显示了没有终端阻抗存在的接收器检测电路(Receiver Detection circuit)。图的右侧是具有终端阻抗的相同电路。检测电压转换必须是共模的(common mode)。检测电压转换必须遵循表6-10中所描述的VTX_RCV_DETECT。接收器检测序列(receiver detect sequence)必须只能处于正共模方向(positive common mode direction)。负向的接收器检测是不被允许的。

6.11.2 Rx检测序列(Rx Detect Sequence)

建议的接收器检测序列(Receiver Detection sequence)如下:

1. 在检测共模漂移(detect common mode shift)之前发送器必须开始一个稳定的电压。

2. 发送器(Transmitter)改变Txp和Txn上的共模电压,与接收器高阻抗(由表6-13中列出的参数ZRX -HIGH-IMP-DC-POS所限制)的检测一致。

3. 接收器的检测基于信号线改变到新电压的速率(A Receiver is detected based on the rate that the lines change to the new voltage)。

• 如果发送器一端的电压(voltage at the Transmitter)的充电速率只由(dictated only by)发送器阻抗(Transmitter impedance),互连容抗(capacitance of the interconnect)以及序列电容(series capacitor)所决定,则接收器(Receiver)就不存在。

• 如果发送器一端的电压(voltage at the Transmitter)的充电速率由(dictated by)发送器阻抗(Transmitter impedance),序列电容(series capacitor), 互连容抗(capacitance of the interconnect)以及接收器终端阻抗(Receiver termination)所决定,则接收器(Receiver)就存在。

每当电气空闲(Electrical Idle)退出时,检测序列不一定都要运行,或者可以被中止。在设备连接(Device connect)过程中,设备接收器(Device receiver)都必须保证当电源平面层(power plane)还正在稳定时,它总是处于高阻抗(high impedance)状态。这是必须的,以防止主机(Host)错误检测设备(Device)并在设备准备好之前开始训练序列。类似的,一个被禁用的端口(disabled port)必须保持其接收器终端阻抗(receiver termination)处于高阻抗(high impedance)(这由参数ZRX -HIGH-IMP-DCPOS所限制),直到被高层引导(directed)从被禁用状态(Disabled state)退出。相反地,处于U1/U2/U3电气空闲(Electrical Idle)的端口必须将其接收器终端阻抗打开(Receiver Termination turned on),并满足RRX-DC规范。

6.11.3 通道容抗的上限(Upper Limit on Channel Capacitance)

由接收器检测电路(Receiver Detection circuit)所见的到地的互连总容抗(interconnect total capacitance)必须不超过3nF(到地),包括附着的测试仪器所添加的容抗。这一限制的需要是因为要保证在接收器检测(Receiver detect)期间的恰当操作。注意这个容抗是独立的,并区分于(distinct)AC耦合容抗值(AC coupling capacitance value)。