CR0-4寄存器介绍

控制寄存器(CR0~CR3)用于控制和确定处理器的操作模式以及当前执行任务的特性,如图4-3所示。

CR0中含有控制处理器操作模式和状态的系统控制标志;

CR1保留不用;

CR2含有导致页错误的线性地址;

CR3中含有页目录表物理内存基地址,因此该寄存器也被称为页目录基地址寄存器PDBR(Page-Directory Base addressRegister)。

x86_32的CR0为32bit。X86_64下为64bit,其中低32bit与x86_32的CR0保持一致,高32bit没有定义,作保留使用,除了bit 4其他所有位都是可读可写的。

Protected-Mode Enable (PE) Bit. Bit0. PE=0,表示CPU处于实模式; PE=1表CPU处于保护模式,并使用分段机制。

Paging Enable (PG) Bit. Bit 31. 该位控制分页机制,PG=1,启动分页机制;PG=0,不使用分页机制。

CR2

存放发生页错误时的虚拟地址,格式如下:

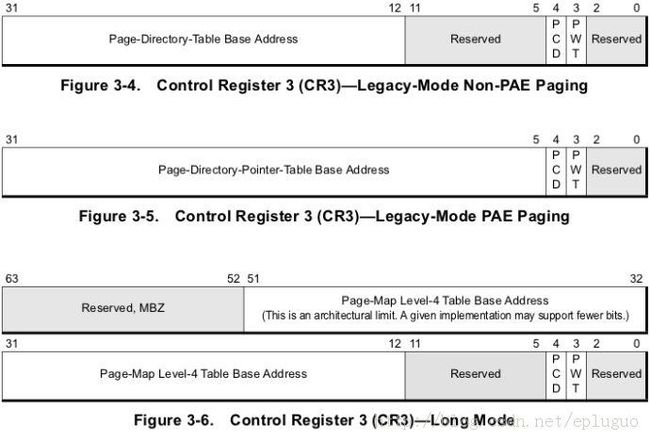

CR3

用来存放最高级页目录地址(物理地址),各级页表项中存放的也是物理地址。格式如下:

Page-Level Writethrough (PWT) Bit. Bit3. Page-level writethrough indicates whether the highest-

level page-translation table has a writeback orwritethrough caching policy. When PWT=0, the table

has a writeback caching policy. When PWT=1, the tablehas a writethrough caching policy.

Page-Level Cache Disable (PCD) Bit. Bit4. PCD=1,表示最高目录表不可缓存,PCD=0,相反。

图3-4中不使用PAE技术,有两层页表。最高层为页目录有1024项,占用4KB。page_directory_table baseaddress为物理地址,指向4KB对齐的页目录地址。

图3-5中,使用PAE技术,三层页表寻址。最高层为页目录指针,4项,占用32B空间。所以 page_directory_table baseaddress为27位,指向32B对齐的页目录指针表。

CR4

legacy mode 下低32位与x86_32的CR4一致,

Virtual-8086 Mode Extensions (VME) Bit. Bit0. Setting VME to 1 enables hardware-supported

performance enhancements for software running invirtual-8086 mode. Clearing VME to 0 disables

this support. The enhancements enabled when VME=1include:

Virtualized, maskable, external-interrupt control andnotification using the VIF and VIP bits in the

rFLAGS register. Virtualizing affects the operation ofseveral instructions that manipulate the

rFLAGS.IF bit.

Selective intercept of software interrupts (INTninstructions) using the interrupt-redirection

bitmap in the TSS.

Protected-Mode Virtual Interrupts (PVI) Bit. Bit1. Setting PVI to 1 enables support for protected-

mode virtual interrupts. Clearing PVI to 0 disablesthis support. When PVI=1, hardware support of

two bits in the rFLAGS register, VIF and VIP, isenabled.

Only the STI and CLI instructions are affected byenabling PVI. Unlike the case when CR0.VME=1,

the interrupt-redirection bitmap in the TSS cannot beused for selective INTn interception.

PVI enhancements are also supported in long mode. See“Virtual Interrupts” on page 251 for more

information on using PVI.

Time-Stamp Disable (TSD) Bit. Bit 2. TheTSD bit allows software to control the privilege level at

which the time-stamp counter can be read. When TSD iscleared to 0, software running at any privilege

level can read the time-stamp counter using the RDTSCor RDTSCP instructions. When TSD is set to

1, only software running at privilege-level 0 canexecute the RDTSC or RDTSCP instructions.

Debugging Extensions (DE) Bit. Bit3. Setting the DE bit to 1 enables the I/O breakpoint capability

and enforces treatment of the DR4 and DR5 registers asreserved. Software that accesses DR4 or DR5

when DE=1 causes a invalid opcode exception (#UD).

When the DE bit is cleared to 0, I/O breakpointcapabilities are disabled. Software references to the

DR4 and DR5 registers are aliased to the DR6 and DR7registers, respectively.

Page-Size Extensions (PSE) Bit. Bit4. PSE=1,启用PSE,PSE=0,不启用。

Physical-Address Extension (PAE) Bit. Bit5.PAE=1,启用PAE,支持2MB的超级页(superpage);PAE=0,不启用PAE。

Machine-Check Enable (MCE) Bit. Bit6. Setting MCE to 1 enables the machine-check exception

mechanism. Clearing this bit to 0 disables themechanism. When enabled, a machine-check exception

(#MC) occurs when an uncorrectable machine-check erroris encountered.

Regardless of whether machine-check exceptions areenabled, the processor records enabled-errors

when they occur. Error-reporting is performed by themachine-check error-reporting register banks.

Each bank includes a control register for enablingerror reporting and a status register for capturing

errors. Correctable machine-check errors are also reported,but they do not cause a machine-check

exception.

See Chapter 9, “Machine Check Mechanism,” for adescription of the machine-check mechanism, the

registers used, and the types of errors captured bythe mechanism.

Page-Global Enable (PGE) Bit. Bit7. When page translation is enabled, system-software

performance can often be improved by making some pagetranslations global to all tasks and

procedures. Setting PGE to 1 enables the global-pagemechanism. Clearing this bit to 0 disables the

mechanism.

When PGE is enabled, system software can set theglobal-page (G) bit in the lowest level of the pagetranslation hierarchy to 1,indicating that the page translation is global. Page translations markedasglobal are not invalidated in the TLB when the page-translation-table baseaddress (CR3) is updated.

When the G bit is cleared, the page translation is notglobal. All supported physical-page sizes also support the global-pagemechanism. See “Global Pages” on page 142 for information on usingthe global-page mechanism.

Performance-Monitoring Counter Enable (PCE) Bit. Bit8. Setting PCE to 1 allows software running at any privilege level to usethe RDPMC instruction. Software uses the RDPMC instruction to read theperformance-monitoring MSRs, PerfCtrn. Clearing PCE to 0 allows only themost-privileged software (CPL=0) to use the RDPMC instruction.

FXSAVE/FXRSTOR Support (OSFXSR) Bit. Bit9. System software must set the OSFXSR bit to 1 to enable use of the256-bit and 128-bit media instructions. When this bit is set to 1, it alsoindicates

that system software uses the FXSAVE and FXRSTORinstructions to save and restore the processor

state for the x87, 64-bit media, and 128-bit mediainstructions.

Clearing the OSFXSR bit to 0 indicates that 256-bitand 128-bit media instructions cannot be used.

Attempts to use those instructions while this bit isclear result in an invalid-opcode exception (#UD).

Software can continue to use the FXSAVE/FXRSTORinstructions for saving and restoring the processor state for the x87 and64-bit media instructions.

Unmasked Exception Support (OSXMMEXCPT) Bit. Bit10. System software must set the OSXMMEXCPT bit to 1 when it supports theSIMD floating-point exception (#XF) for handling of unmasked 256-bit and128-bit media floating-point errors. Clearing the OSXMMEXCPT bit to0 indicates the #XF handler is not supported. When OSXMMEXCPT=0, unmasked128-bit media floating-point exceptions cause an invalid-opcode exception(#UD). See “SIMD Floating-Point Exception Causes” in Volume 1 for moreinformation on unmasked SSE floating-point exceptions.

XSAVE and Extended States (OSXSAVE) Bit. Bit18. If this bit is set to 1 then the operating system

supports the XGETBV, XSETBV, XSAVE and XRSTOR instructions.The processor will also be able

to execute XGETBV and XSETBV instructions in order toread and write XCR0. Also, if set, the

XSAVE and XRSTOR instructions can save and restore thex87 FPU state (including MMX registers),

the SSE state (YMM/XMM registers and MXCSR), alongwith other processor extended states

enabled in XCR0.

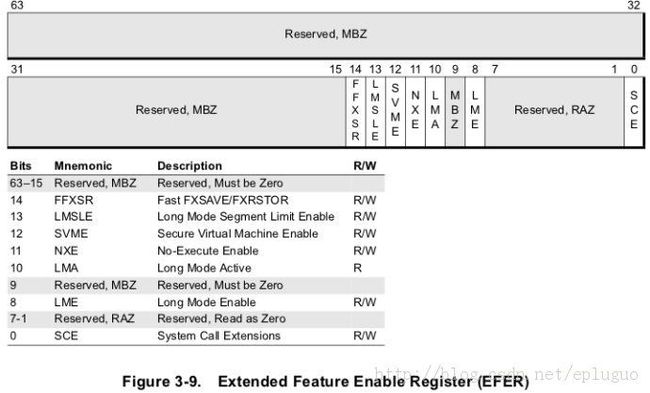

Extended Feature Enable Register (EFER)

System-Call Extension (SCE) Bit. Bit0. Setting this bit to 1 enables the SYSCALL and SYSRET

instructions. Application software can use theseinstructions for low-latency system calls and returns in a non-segmented(flat) address space. See “Fast System Call and Return” on page 152 foradditional information.

Long Mode Enable (LME) Bit. Bit 8. LME=1,启用longmode,注意必须先将CR0.PG=0后才能设置LME=1,然后再设置CR0.PG=1,则进入longmode。LME=0 ,使用legacy mode。

Long Mode Active (LMA) Bit. Bit 10, read-only. This bitindicates that long mode is active. The

processor sets LMA to 1 when both long mode and paginghave been enabled by system software. See

Chapter 14, “Processor Initialization and Long ModeActivation,” for more information on activating long mode.

When LMA=1, the processor is running either incompatibility mode or 64-bit mode, depending on the

value of the L bit in a code-segment descriptor, asshown in Figure 1-6 on page 12.

When LMA=0, the processor is running in legacy mode.In this mode, the processor behaves like a

standard 32-bit x86 processor, with none of the new64-bit features enabled.

No-Execute Enable (NXE) Bit. Bit 11. Setting this bitto 1 enables the no-execute page-protection

feature. The feature is disabled when this bit iscleared to 0. See “No Execute (NX) Bit” on page 145 for more information.

Before setting NXE, system software should verify theprocessor supports the feature by examining

the extended-feature flags returned by the CPUIDinstruction. For more information, see the CPUID

Specification, order# 25481.

Secure Virtual Machine Enable (SVME) Bit. Bit 12.Enables the SVM extensions. When this bit is

zero, the SVM instructions cause #UD exceptions.EFER.SVME defaults to a reset value of zero. The

effect of turning off EFER.SVME while a guest isrunning is undefined; therefore, the VMM should

always prevent guests from writing EFER. SVMextensions can be disabled by setting VM_CR.SVME_DISABLE . For more information, see descriptions of LOCK and SMVE_DISABLE bitsin Section 15.29.1, “VM_CR MSR (C001_0114h),” on page 431.

Long Mode Segment Limit Enable (LMSLE) bit. Bit 13.Setting this bit to 1 enables certain limit

checks in 64-bit mode. See Section 4.12.2, "DataLimit Checks in 64-bit Mode", for more information

on these limit checks.

Fast FXSAVE/FXRSTOR (FFXSR) Bit. Bit 14. Setting thisbit to 1 enables the FXSAVE and FXRSTOR instructions to execute faster in64-bit mode at CPL 0. This is accomplished by not saving or restoring theXMM registers (XMM0-XMM15). The FFXSR bit has no effect whenthe FXSAVE/FXRSTOR instructions are executed in non 64-bit mode, or whenCPL > 0. The FFXSR bit does not affect the save/restore of the legacyx87 floating-point state, or the save/restore of MXCSR.

Before setting FFXSR, system software should verifywhether this feature is supported by examining

the CPUID extended feature flags returned by the CPUID instruction.For more information, see

"Function 8000_0001h: Processor Signature and AMDFeatures" in Volume 3.