Intel80386知识总结: 基本要素

====================================================================

本文用于汇总整理Intel80386的系统架构中的基本要素,

参考文献:

本文是系列文章《Intel80386知识总结》的一部分。

===================================================================

1. 支持的内存模型

i386在设计上力图将内存的管理分为两层,底层功能的实现由系统软件负责,保证上层应用程序的设计可以与物理内存的现实隔离,这意味着在开发应用软件的过程中中可以完全不知道指令和数据在物理内存中具体是怎么存放的。最终,由系统软件暴露给应用软件的内存模型可以为以下两种:

2. 支持的数据类型

2.1 基本数据类型

基本数据类型三种:

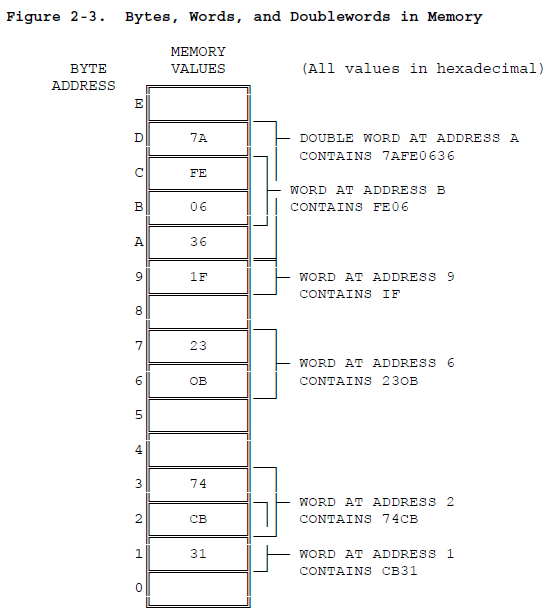

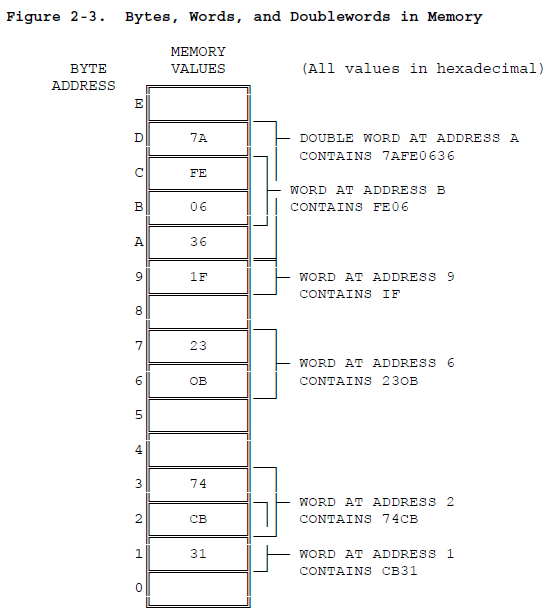

关于对齐:i386没有强制性的内存对齐的要求,即word不需要一定被放在偶数地址处,doubleword不一定要被放在4的倍数地址处,如下图所示:

但是从性能角度考虑,需要考虑到以下事实:如果系统使用32bit系统总线,则在内存与处理器之间真实传输的数据,每次都是内存中4的倍数地址处起始的4byte数据,获取非对齐的word或doubleword可能会造成多次访存后数据mask的多余操作,造成性能开销。

2.2 高级数据类型

3. 寄存器

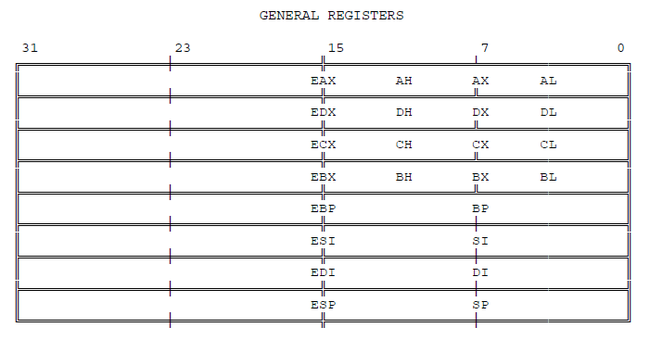

3.1通用寄存器

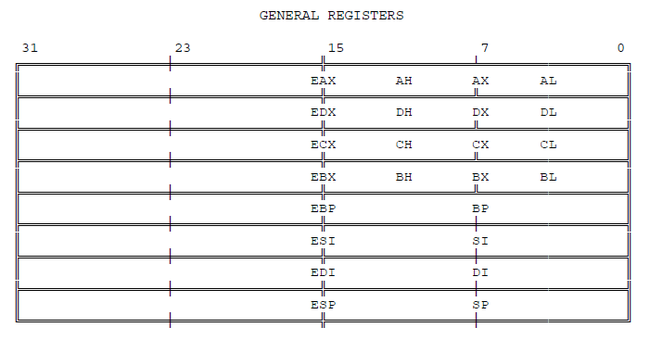

通用寄存器用于保存操作数用于算数/逻辑计算,也用于寻址,i386包含以下通用寄存器:

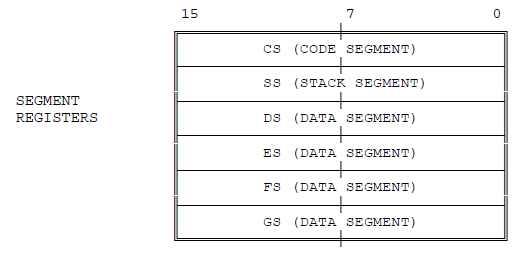

3.2段寄存器

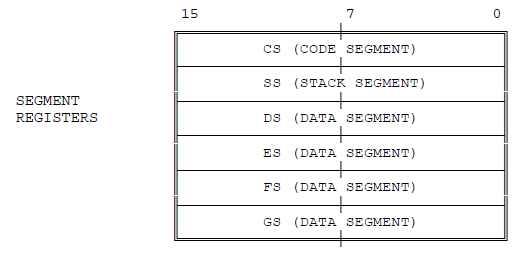

在系统运行的任意时刻,程序可以直接访问6个段,这6个段就由下列6个寄存器指明。

其中CS和SS分别被称为当前代码段和当前堆栈段。同一时刻可以访问的数据段有上图所示的四个。

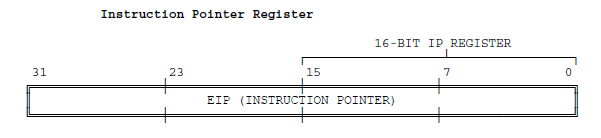

3.3EIP、ESP和EBP寄存器

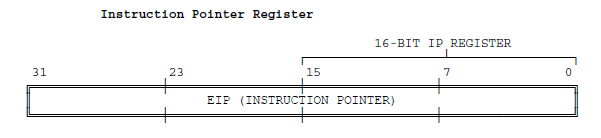

EIP寄存器给出了当前代码段中的一个Offset,用于指明下一条执行的指令,其长度如下图所示。

ESP和EBP给出了当前堆栈段中的一个Offset,用于堆栈的实现:

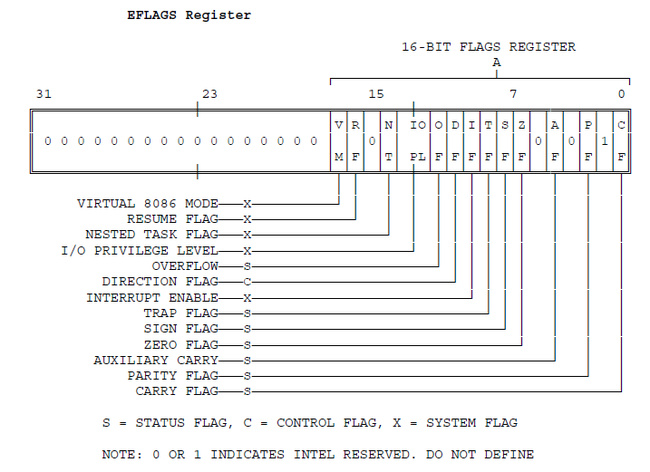

3.4 标志位寄存器

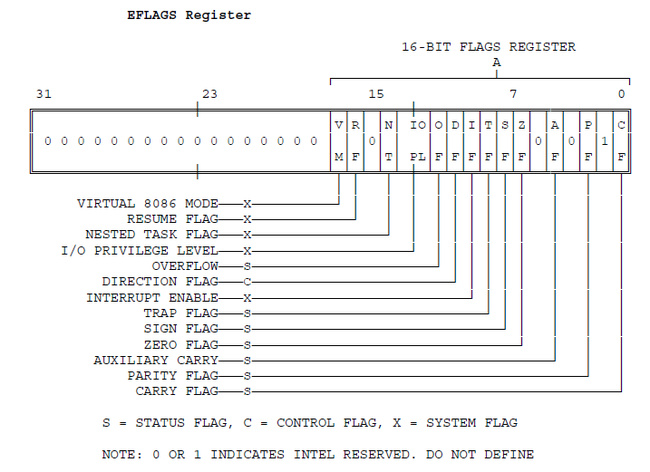

标志位寄存器EFLAGS,用于设置系统的状态,影响系统的行为,其结构如下图所示:

标志位寄存器中的标志位可以分为三组:状态标志位、控制标志位和系统级标志位。

3.4.1 状态标志位

状态标志位用于表示一条指令的执行状态或结果,进而影响之后指令的执行。状态标志位包括:OF、SF、ZF、AF、PF和CF六个。

3.4.2 控制标志位

控制标志位只有一个:DF。当DF=1时,所有的String指令进入auto-decrement状态,由高位向低位处理String。当DF=0时,所有的String指令进入auto-increment状态,由低位向高位处理String。

3.4.3 系统级标志位

3.5 内存管理寄存器

共四个:

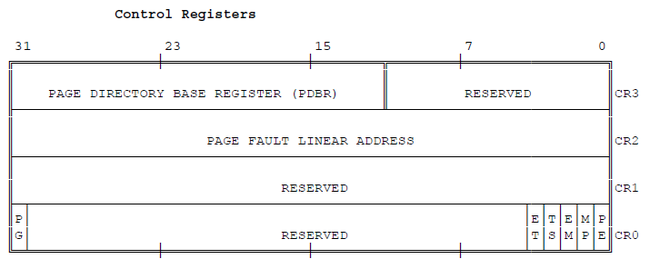

3.6 控制寄存器

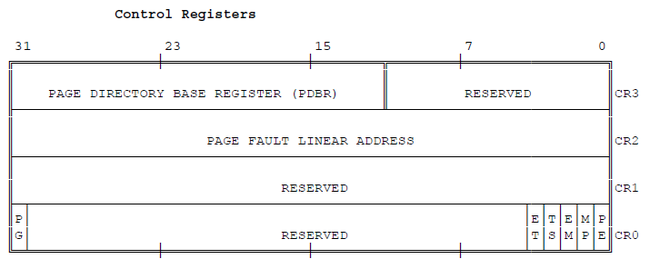

控制寄存器包扩CR0、CR1、CR2和CR3四个,它们只能通过几个MOV指令访问,下图是它们的结构:

其中CR0用于设置一些系统的属性,这些属性都是全局有效的,而不是针对某个Task:

CR2用于处理Page Fault,保存Fault发生的线性地址。

CR3用于保存PageDir(i386二级页表体系中的第一级页表)的基地址。

3.7 Debug寄存器

提供高级Debug功能,略。

3.8 Test寄存器

仅用于测试TLB(Translation Lookaside Buffer)的正确性,略。

4. 指令设计

i386的所有指令有许多共同点,都包含以下元素,其中只有Opcode是必须包含的,其他元素都只在部分指令中出现。

4.1 前缀

可以包含以下信息:

4.2 Opcode

指明指令要进行的操作。

4.3 寄存器Specifier

指明要操作的寄存器。

4.4 寻址模式信息

指明操作数的寻址模式。

4.5 立即操作数

可供立即使用的操作数。

本文用于汇总整理Intel80386的系统架构中的基本要素,

参考文献:

- 《INTEL 80386 programmer's reference manual 1986》

本文是系列文章《Intel80386知识总结》的一部分。

===================================================================

1. 支持的内存模型

i386在设计上力图将内存的管理分为两层,底层功能的实现由系统软件负责,保证上层应用程序的设计可以与物理内存的现实隔离,这意味着在开发应用软件的过程中中可以完全不知道指令和数据在物理内存中具体是怎么存放的。最终,由系统软件暴露给应用软件的内存模型可以为以下两种:

- Flat模型:包含一个单独的4G字节的内存空间

- Segmented模型:包含16383(2^14)个隔离的线性地址空间,每个线性地址空间的大小为4G,共计64T的地址空间

2. 支持的数据类型

2.1 基本数据类型

基本数据类型三种:

| 数据类型 | 长度 |

| byte | 8 bit |

| word | 16 bit |

| doubleword | 32 bit |

关于对齐:i386没有强制性的内存对齐的要求,即word不需要一定被放在偶数地址处,doubleword不一定要被放在4的倍数地址处,如下图所示:

但是从性能角度考虑,需要考虑到以下事实:如果系统使用32bit系统总线,则在内存与处理器之间真实传输的数据,每次都是内存中4的倍数地址处起始的4byte数据,获取非对齐的word或doubleword可能会造成多次访存后数据mask的多余操作,造成性能开销。

2.2 高级数据类型

| 数据类型 | 长度 | 定义 |

| Integer | 32或16或8 bit | 有符号整数,补码编码 |

| Ordinal | 32或16或8 bit | 无符号整数,所有数据都被解码为非负数 |

| Near Pointer | 32 bit | 逻辑地址指针,同一段中的offset |

| Far Pointer | 48 bit | 16 bit段选择符+32bit段内偏移 |

| String | 0 ~ (2^32-1) bytes | 表示一组连续的byte |

| Bit Field | 0~32 bit | 表示一组连续的bit,可以从任意byte的任意一个bit开始,最长32bit |

| Bit String | 0 ~ (2^32-1) bytes | 表示一组连续的bit,可以从任意byte的任意一个bit开始,最长(2^32-1) bytes |

| BCD(unpacked representation of decimal digit) | 1byte每1个十进制数字 | 用一个byte保存一个十进制数字,只有低四位是有效的。在做乘除法时必须保证高四位为0,在做加减法时高四位可以任意取值 |

| Packed BCD | 1byte每两个十进制数字 | 一个byte的高四位和低四位分别保存一个十进制数字,表示范围为0-99,其中低四位对应十进制个位,高四位对应十进制十位 |

3. 寄存器

3.1通用寄存器

通用寄存器用于保存操作数用于算数/逻辑计算,也用于寻址,i386包含以下通用寄存器:

3.2段寄存器

在系统运行的任意时刻,程序可以直接访问6个段,这6个段就由下列6个寄存器指明。

其中CS和SS分别被称为当前代码段和当前堆栈段。同一时刻可以访问的数据段有上图所示的四个。

3.3EIP、ESP和EBP寄存器

EIP寄存器给出了当前代码段中的一个Offset,用于指明下一条执行的指令,其长度如下图所示。

ESP和EBP给出了当前堆栈段中的一个Offset,用于堆栈的实现:

- ESP给出SS段中一个Offset,用于指明栈顶

- EBP又被称为stack-frame base pointer,可用于辅助栈的实现

3.4 标志位寄存器

标志位寄存器EFLAGS,用于设置系统的状态,影响系统的行为,其结构如下图所示:

标志位寄存器中的标志位可以分为三组:状态标志位、控制标志位和系统级标志位。

3.4.1 状态标志位

状态标志位用于表示一条指令的执行状态或结果,进而影响之后指令的执行。状态标志位包括:OF、SF、ZF、AF、PF和CF六个。

3.4.2 控制标志位

控制标志位只有一个:DF。当DF=1时,所有的String指令进入auto-decrement状态,由高位向低位处理String。当DF=0时,所有的String指令进入auto-increment状态,由低位向高位处理String。

3.4.3 系统级标志位

- IF(Interrupt_Enable Flag):设置处理器对external(maskable)中断的处理是否开启,对异常或non maskable中断无效。

- NT(Nested Task):用于多任务和中断处理方面

- RF(Resume Flag):暂时屏蔽debug异常,避免一个debug异常打断一个正在处理的debug异常

- TF(Trap Flag):当TF=1时,处理器进入单步调试状态,在此状态中,处理器在每条指令结束的时候会自动产生一个异常,用于处理程序的监控

- VM(Virtual 8086 Mode):用8086兼容模式执行当前Task

3.5 内存管理寄存器

共四个:

- GDTR:Global段描述符表寄存器

- LDTR:Local段描述符表寄存器

- IDTR(Interrupt Descriptor Table Register):中断描述符表寄存器

- TR(Task Register):用于指向当前的任务描述数据结构

3.6 控制寄存器

控制寄存器包扩CR0、CR1、CR2和CR3四个,它们只能通过几个MOV指令访问,下图是它们的结构:

其中CR0用于设置一些系统的属性,这些属性都是全局有效的,而不是针对某个Task:

- EM(Emulation): 指明是否模拟协处理器的功能

- ET(Extension Type):用于指明系统中配置的协处理器的类型(80287或80387)

- MP(Math Present):用于影响WAIT指令(协调处理器与协处理器)的行为。

- PE(Protection Enable):PE=1处于保护模式,PE=0处于实模式

- PG(Paging):是否使用分页机制

- TS(Task Switched):每次切换Task的时候处理器都会设置此状态位,并且在每次解释协处理器指令的时候都会检查该状态位

CR2用于处理Page Fault,保存Fault发生的线性地址。

CR3用于保存PageDir(i386二级页表体系中的第一级页表)的基地址。

3.7 Debug寄存器

提供高级Debug功能,略。

3.8 Test寄存器

仅用于测试TLB(Translation Lookaside Buffer)的正确性,略。

4. 指令设计

i386的所有指令有许多共同点,都包含以下元素,其中只有Opcode是必须包含的,其他元素都只在部分指令中出现。

4.1 前缀

可以包含以下信息:

- 段重载信息:显示指明指令该使用哪个段寄存器

- 地址长度:在32bit/16bit两代地址间切换

- 操作数长度:在32bit/16bit操作数间切换

- Repeat:某些String指令可以针对一个String的每个元素反复执行

4.2 Opcode

指明指令要进行的操作。

4.3 寄存器Specifier

指明要操作的寄存器。

4.4 寻址模式信息

指明操作数的寻址模式。

4.5 立即操作数

可供立即使用的操作数。