Samsung CPU clock

use each PLL. The PLL begins the lockup sequence toward the new frequency only after the S/W configures the PLL with a new frequency-value. The PLL output is immediately fed to SYSCLK after lock time.

首先要了解什么是FCLK,HCLK和PCLK

FCLK用于CPU内核,HCLK用于AHB总线上设备,比如CPU核、存储器控制器、中断控制器、LCD控制器、DMA和USB主机模块等;PLCK用于APB总线上的设备,比如WATCHDOG、IIS,IIC、PWM定时器等。

系统上电时,MPLL没有启动,FCLK等于外部输入的时钟,称为Fin。要提高系统时钟就需要启用MPLL。

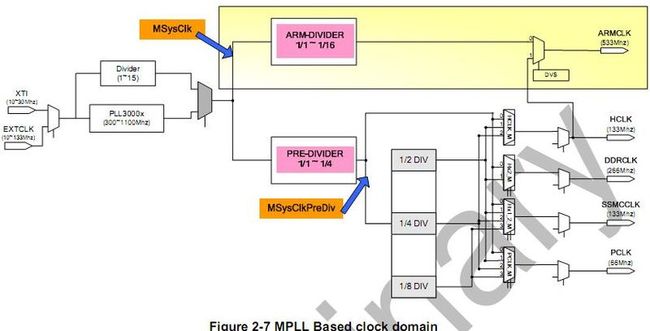

当MPLL启动之后,Fin经过MPLL之后,产生的是MPLL CLK,也即MCLK,MCLK=SYSCLK。再经过ARM DIV之后,产生ARMCLK,ARMCLK = FCLK.这个就是我们平时说的CPU的主频,300MHz,400MHz,533MHz等

The output frequencies of MPLL can be calculated using the following equations:

FOUT = (m x FIN) / (p x 2s) (should be 300~1100Mhz) //2s指的是2的s次方,Fout即经过PLL之后的频率

where, m = MDIV , p = PDIV, s = SDIV, Fin = 10~30Mhz

现在HW提供的Fin = 12MHz; MDIV = 400; PDIV = 3; SDIV = 1;

所以, Fout = ( 400 *12)/ (3*2) = 800MHz

ARMCLK = MPLL/2; PREDIV_CLK = MPLL/3; HCLK = PREDIV_CLK/2; PCLK = HCLK/2;

所以,ARMCLK = 800/2 = 400MHz; HCLK = 133; PCLK = 133/2 = 66MHz;

; Fin = 12MHz,

; Kathy090709 modify for S3C2450 CPU clock

; MPLLout = (m x Fin)/(p x 2**s), m=MDIV, p=PDIV, s=SDIV, Fin=10~30MHz

; Note: Don't set the value PDIV[5:0] or MDIV[9:0] to all zeros. (6’b00 0000 / 10’b00 0000 0000)

; (50,1,1)=300Mhz, (200,3,1)=400Mhz, (150,2,1)=450Mhz, (178,2,1)=534Mhz,

; (50,1,0)=600Mhz, (400,3,1)=800Mhz

;

; EPLLout = (m + k/2**16)xFin/(p x 2**s), m=MDIV, p=PDIV, s=SDIV,k=KDIV, Fin=10~40MHz

; Note: Don't set the value PDIV[5:0] or MDIV[7:0] to all zeros. (6’b00 0000 / 8’b0000 0000)

; (12,1,2,0)=36Mhz, (16,1,2,0)=48Mhz, (10,1,1,0)=60Mhz, (12,1,1,0)=72Mhz, (14,1,1,0)=84Mhz

; (32,1,2,0)=96Mhz

6443 CPU

S5P6443 has three PLLs which are APLL for ARM operating clock, MPLL for main operating clock, and EPLL for special purpose. The operating clocks are divided into three groups. The first is the ARM clock, which is generated from APLL. MPLL generates the main system clocks, which are used for operating AXI, AHB, and APB bus operation. The last group of clocks is generated from EPLL. Mainly, the generated clocks are used for peripheral IPs, i.e., UART, I2S_V40, I2C, etc.

The lowest three bits of CLK_SRC0 register control the source clocks of three groups. When the bit has 0, the input clock is bypassed to the group. Otherwise, the PLL output will be supplied to the group.