ARM开发步步深入之SDRAM编程示例

实验环境及说明:恒颐S3C2410开发板H2410。H2410核心板扩展有64MB的SDRAM,用于设置程序堆栈和存放各种变量。SDRAM选用了两片三星公司的K4S561632(4M*16bit*4BANK),两片拼成32位数据宽度的SDRAM存储系统,并映射到S3C2410的SROM/SDRAM的BANK6,地址范围是0x30000000~0x33FFFFFF。

实验思路:开发板上电启动后,自动将NandFlash开始的4K数据复制到SRAM中,然后跳转到0地址开始 执行,然后初始化存储控制器,把程序本身从SRAM中复制到SDRAM中,最后跳转到SDRAM中运行。故问题的关键是SDRAM的初始化,根据 S3C2410的Datasheet,要使用SDRAM,就需配置存储控制器的13个寄存器。

知识掌握:SDRAM和13个存储控制器的寄存器。

一、SDRAM:

CPU提供了一组用于SDRAM的信号:SDRAM时钟有效信号SCKE;SDRAM时钟信号 SCLK0/SCLK1;数据掩码信号DQM0/DQM1/DQM2/DQM3;SDRAM片选信号nGCS0(与nGCS6是同一引脚的两个功 能);SDRAM行地址选通脉冲信号nSRAS;SDRAM列地址选通脉冲信号nSCAS;写允许信号nWE(不是SDRAM专用的);

★SDRAM结构:SDRAM的内部是一个存储阵列,检索时先指定一个行,再指定一个列,就可以准确地找到所需要的单元格,这就是SDRAM寻址的基本原理;单元格被称为存储单元,表格就是逻辑BANK,SDRAM一般含有4个逻辑BANK。

★SDRAM的访问:SDRAM片选信号nGCS0有效;逻辑BANK选择;对选中的芯片进行统一的行/列寻 址;CPU会从32位的地址中自动分出 逻辑BANK选择信号、行地址信号、列地址信号,然后先后发出行地址信号、列地址信号,逻辑BANK选择信号在发出行地址信号的同时发出,并维持到列地址 信号结束;找到了存储单元后,被选中的芯片就要进行统一的数据传输了。

二、存储控制器的寄存器:

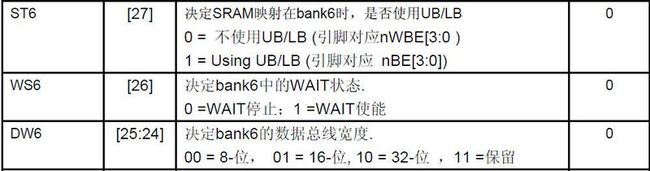

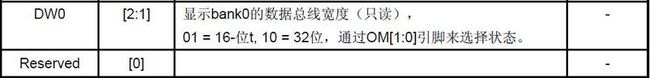

★BWSCON(Bus width & wait status control register,总线位宽和等待状态控制寄存器):此寄存器用于配置BANK0~BANK7的位宽和状态控制,每个BANK用4位来配置,分别是:

● ST(启动/禁止SDRAM的数据掩码引脚。对于SDRAM,此位置0;对于SRAM,此位置1)

● WS(是否使用存储器的WAIT信号,通常置0为不使用)

● DW(两位,设置位宽。此板子的SDRAM是32位,故将DW6设为10)

特殊的是bit[2:1],即DW0,设置BANK0的位宽,由板上的跳线决定,只读的。其实只需将BANK6 对应的4位设为0010即可,在此处BWSCON先设置为0x02000000。SDRAM接BANK6对应的[27:24]位,同时注意BANK0比较 特殊,如下图所示:

★BANKCON0~BANKCON7:用来分别配置8个BANK的时序等参数。SDRAM是映射到BANK6 和BANK7上的(内存只能映射到这两个BANK,具体映射多大的空间,可用BANKSIZE寄存器设置),所以只需参照SDRAM芯片的 Datasheet配置好BANK6和BANK7,BANKCON0~BANKCON5使用默认值0x00000700即可。对于BANKCON6和 BANKCON7中的各个位的描述:

●MT(bit[16:15]):设置本BANK映射的物理内存是SRAM还是SDRAM,后面的低位就根据此MT的选择而分开设置。本板子应置0b11,所以只需要再设置下面两个参数

●Trcd(bit[3:2]):RAS to CAS delay(00=2 clocks,01=3 clocks,10=4 clocks),推2410手册上的荐值是0b01。我们PC的BIOS里也可以调节的,应该玩过吧。

●SCAN(bit[1:0]):Column address number(00 = 8-bit,01 = 9-bit,10= 10-bit),SDRAM列地址位数。查阅K4S561632芯片手册得知此值是9,所以SCAN=0b01。如果使用其他型号的SDRAM,您需要查 看它的数据手册来决定SCAN的取值:00-8位、01-9位、10-10位。综合以上各值,BANKCON6~BANKCON7设为 0x00018005。

★REFRESH(刷新控制寄存器):此寄存器的bit[23:11]可参考默认值,或自己根据经验修改,这里 用0x008e0000,关键是最后的Refresh Counter(简称R_CNT,bit[10:0])的设置,2410手册上给出了公式计算方法。SDRAM手册上“8192 refresh cycles/64ms”的描述,得到刷新周期为64ms/8192=7.8125us,结合公式,R_CNT=2^11 + 1 – 12 * 7.8125 = 1955。所以可得REFRESH=0x008e0000+1995=0x008e07a3。

●Trp([21:20]):设置为0即可。

●Tsrc([19:18]):设置默认值即可。

★BANKSIZE:设置SDRAM的一些参数。位[7]=1:Enable burst operation(0=ARM核禁止突发传输,1=arm核 支持突发传输);位[5]=1:SDRAM power down mode enable(0=不使用SCKE信号令SDRAM进入省电模式,1=使用SCKE信号令SDRAM进入省电模式);位[4]=1:SCLK is active only during the access (recommended);位[2:1]=010:BANK6、BANK7对应的地址空间与BANK0-5不同。BANK0-5的地址空间都是固定的 128M,地址范围是(x*128M)到(x+1)*128M-1,x表示0到5。但是BANK6-7的起始地址是可变的,您可以从S3C2410数据手 册第5章"Table 5-1. BANK6-7 Addresses"中了解到BANK6-7的地址范围与地址空间的关系。本开发板仅使用BANK6的64M空间,其中 BK76MAP(bit[2:0])配置BANK6/7映射的大小,可设置为010 = 128MB/128MB或001 = 64MB/64MB,只要比实际RAM大都行,多出来的空间程序会检测出来,不会发生使用不存在的内存的情况(Bootloader和Linux内核都会 作内存检测)。BANKSIZE=0x000000b2。

★MRSRB6、MRSRB7(Mode register set register BANK6/7,SDRAM模式设置寄存器):可以修改的只有CL[6:4](CAS latency,000 = 1 clock, 010 = 2 clocks, 011=3 clocks),其他的全部是固定的(fixed),故值为0x00000030。SDRAM 不支持CL=1的情况,所以位[6:4]取值为010(CL=2)或011(CL=3),开发板保守的值为0b11。

至此,13个存储控制器的寄存器全部介绍完了,下面就可以配置各寄存器的值,完成SDRAM初始化,实现代码复制到SDRAM中执行的操作(注:同样的程序速度要比片内SRAM运行的慢)。

存储控制器13个寄存器的设置值:

mem_cfg_val:

.long 0x02000000 @BWSCON;此处只用到BANK6对应的[27:24],其它位没理会,想理论上应该可以?

.long 0x00000700 @BANKCON0;BANKCON0~BANKCON5没用到,使用默认值0x00000700

.long 0x00000700 @BANKCON1

.long 0x00000700 @BANKCON2

.long 0x00000700 @BANKCON3

.long 0x00000700 @BANKCON4

.long 0x00000700 @BANKCON5

.long 0x00018005 @BANKCON6

.long 0x00018005 @BANKCON7

.long 0x008e07a3 @REFRESH

.long 0x000000b1 @BANKSIZE

.long 0x00000030 @MRSRB6

.long 0x00000030 @MRSRB7

汇编过程主要代码:

.equ MEM_CTL_BASE, 0x48000000 @ 定义存储控制器寄存器基址

.equ SDRAM_BASE, 0x30000000 @ 定义SDRAM起始地址

.text

.global _start

_start:

bl disable_watch_dog @ 去关门喂狗

bl mem_control_setup @ 去设置存储控制器

bl copy_steppingstone_to_sdram @ 复制代码到SDRAM中

ldr pc, =on_sdram @ 跳到SDRAM中继续执行

on_sdram:

ldr sp, =0x34000000 @ 设置堆栈,执行C点灯代码

bl main

halt_loop:

b halt_loop