基于DSP与AD9852的任意信号发生器的设计

直接数字式频率合成(DDS)技术是继直接频率合成和间接频率合成之后,随着数字集成电路和微电子技术的发展而迅速发展起来的第三代频率合成技术。DDS技术具有相对带宽宽、频率转换时间短、频率分辨率高等优点,输出相位连续,频率、相位和幅度均可实现程控,常用于高精度频率合成和任意信号发生。本文在发动机电控单元(ECU)硬件在环仿真系统的设计中,使用 TMS320 LF2407A控制2片 AD9852 产生2路同步的任意信号,仿真发动机工作时的真实信号。

1 AD9852 和 TMS320LF2407A 简介

AD9852 是美国ANALOG Devices公司生产的新型直接数字频率合成器,具有频率转化速度快、频谱纯度高、工作温度范围宽、集成度高等特点。工作电压为3.3 V,片内有4~20倍可编程时钟乘法电路,系统最高时钟可达300 MHz,输出频率可达120 MHz,频率转化速度小于1μs。内部有12位D/A转化器、48位可编程频率寄存器和14位可编程相位寄存器,具有12位振幅调谐功能,能产生频率、相位、幅度可编程控制的高稳定模拟信号。

TMS320LF2407A 是TI公司推出的一款定点DSP控制器,他采用高性能静态CMOS技术,使供电电压降为3.3 V,减小了控制器的功耗;指令最短为25 ns,具有较强的实时控制能力;片内有32 kB可加密的FLASH程序存储器、2.5 kB的RAM,500 ns转换时间的A/D转换器,片上事件管理器提供了可以满足各种电机控制要求的PWM接口和I/O功能,此外片内还集成了SPI,SCI和CAN控制器。

2 TMS320LF2407A 与 AD9852 的硬件接口电路

在本系统中, TMS320LF2407A 的功能是计算所要产生信号的波形参数,并发送控制字到 AD9852 内部的控制寄存器,以实现可编程的任意信号发生。数据的传输有串行、并行2种方式,串行传输速率最大为10 MHz,并行传输速率最大为100 MHz。为了节约DSP资源,在满足系统要求的前提下,采取串口连接方式,利用 TMSLF2407A 片内的串行外设接口(SPI)控制 AD9852 。接口电路的原理框图如图1所示。

3 AD9852 的串行通信工作过程

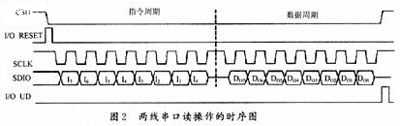

AD9852 的串行接口与 TMS320LF2407A 的SPI接口兼容,通过5个端口即可实现串行数据的传输控制。PRD/CSB是复用信号,在串行工作状态下CSB作为 AD9852 串行总线的片选信号,I/O RESET是串口总线复位信号,SCLK是串口时钟信号,系统采用的是2线串口通信模式,使用SDIO端口进行双向输入输出操作,I/O UD是更新时钟信号。串行通信工作的时序如图2所示。

AD9852 的串行通信周期分为2个阶段,SCLK的前8个上升沿对应于指令周期,在指令周期中,用户向 AD9852 的串口控制器发送命令字来控制随后进行的串行数据传输。数据传输周期从SCLK的第9个上升沿开始,输入数据在时钟上升沿写入,输出的数据则在时钟的下降沿读出。由串口传送的数据首先被写入I/O缓存寄存器中,当系统接收到有效的更新信号时,才将这些数据写入内部控制寄存器组,完成相应的功能。当完成了通信周期后, AD9852 的串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字。

当I/O SESET引脚出现一个高电平输入时,将会立即终止当前的通信周期,当I/O RESET引脚状态回到低电平时, AD9852 串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字,这一点对保持通信的同步十分有益。

4 2片 AD9852 同步工作

实现2片 AD9852 输出信号波形相位同步的关键是使他们工作在相同的系统时钟下,每个 AD9852 的系统时钟之间的相位误差最大不能超过1个周期。 AD9852 的系统时钟可由参考时钟直接提供,或将参考时钟通过内部的时钟倍频器放大而成。异步的更新时钟经过 AD9852 内部的边沿检测电路后与系统时钟同步,形成上升沿,触发内部控制寄存器更新内容。因此,要实现2片 AD9852 的同步,必须使其参考时钟与更新信号的上升沿同步。下面是确保2片 AD9852 同步工作需要注意的一些要点。

4.1 参考时钟信号

AD9852 的参考时钟有差分输入和单端输入2种形式,由于差分时钟在脉冲边沿具有更短的上升和下降时间以及最小的抖动率,可以有效地降低2片 AD9852 参考时钟间的相位误差,因此本系统采用了参考信号差分输入的方式。对于差分输入方式,输入端信号可以是方波或正弦波,推荐使用MAXIM公司的 MAX9371 ,他可以将普通时钟信号转化成系统所需的差分时钟信号。为了实现参考时钟同步,令2片 AD9852 合用一个晶振,晶振输出的信号先分别传给两个差分时钟生成器,经过转化后输入2片 AD9852 。为了使每片 AD9852 参考时钟信号在传输过程中的延迟时间一致,PCB布线时必须确保时钟信号走线距离相同。

4.2 更新时钟信号

在对 AD9852 进行编程时,串行输入的数据被缓存在内部的I/O缓冲寄存器中,不会影响到 AD9852 的工作状态;在更新时钟信号的上升沿到来后,触发I/O缓冲寄存器把数据传送给内部控制寄存器,这时才能完成相应功能,实现对输出信号的控制。更新时钟信号的产生有2种方式,一种是由 AD9852 芯片内部自动产生,用户可以对更新时钟的频率进行编程来产生固定周期的内部更新时钟;另一种是由用户提供外部更新时钟,此时 AD9852 I/OUD引脚为输入引脚,由外部控制器提供信号。要实现2片 AD9852 同步,必须确保他们的更新时钟信号的上升沿同时来临,因此系统采取外部时钟更新的方式。使用DSP的一个I/O端口与 AD9852 的I/O UD相连接,可以通过软件的方式实现对更新时钟信号上升沿的精确控制。对外部更新时钟信号的布线要求同参考时钟一样。

4.3 参考时钟倍频器

AD9852 的工作时钟高达300 MHz,为了降低时钟信号的干扰,系统应采用低频时钟信号源,然后通过 AD9852 片内的参考时钟倍频器,对外部参考时钟实现4~20倍频。参考时钟倍频器的锁相环电路有2个工作状态:锁定状态和获得锁定状态。在锁定状态,系统时钟信号和参考时钟信号可以保持同步。但当给 AD9852 发送控制指令时,在其参考时钟倍频器工作后的短暂时间内,锁相环不能立刻锁定,仍然工作在获得锁定状态。而此时传送到 AD9852 相位累加器的系统时钟周期的个数是不可控的,这可能导致2片 AD9852 的输出信号之间相位不同步,因此系统初始化以后,一定要先确保锁相环进入锁定状态,然后才能更新 AD9852 内部的各种控制字。 AD9852 片内锁相环锁定的典型时间约为400μs,建议至少留出1 ms时间使锁相环进入锁定状态。

5 AD9852 的控制流程

(1)给系统上电,由DSP向 AD9852 发出复位信号,此信号需要至少保持10个参考时钟周期的高电平。

(2)将S/P SELECT置0,选择串行数据输入方式。

(3)依次给每个 AD9852 发送控制字,使每个 AD9852 工作状态由缺省的内部更新时钟模式改变成外部时钟更新模式。

(4)将 AD9852 时钟倍频器工作的控制字依次写入每个 AD9852 的I/O缓冲寄存器中,然后由DSP发出外部更新时钟,更新每个 AD9852 内部控制寄存器。

(5) DSP发出外部更新信号,至少等待1.0 ms时间使 AD9852 内部锁相环锁定。然后由DSP发送有关信号波形参数给 AD9852 ,对他们的内部控制寄存器内容进行同步更新,使2片 AD9852 输出同步的模拟信号。

6 结语

使用DSP控制 AD9852 产生的爆震信号和凸轮轴信号,在精确度和实时性两个方面都能够满足发动机电控单元硬件在环仿真系统的要求。在此系统的基础上,可以进一步扩展为多片DDS同步使用,适用于更多硬件在环仿真系统。

1 AD9852 和 TMS320LF2407A 简介

AD9852 是美国ANALOG Devices公司生产的新型直接数字频率合成器,具有频率转化速度快、频谱纯度高、工作温度范围宽、集成度高等特点。工作电压为3.3 V,片内有4~20倍可编程时钟乘法电路,系统最高时钟可达300 MHz,输出频率可达120 MHz,频率转化速度小于1μs。内部有12位D/A转化器、48位可编程频率寄存器和14位可编程相位寄存器,具有12位振幅调谐功能,能产生频率、相位、幅度可编程控制的高稳定模拟信号。

TMS320LF2407A 是TI公司推出的一款定点DSP控制器,他采用高性能静态CMOS技术,使供电电压降为3.3 V,减小了控制器的功耗;指令最短为25 ns,具有较强的实时控制能力;片内有32 kB可加密的FLASH程序存储器、2.5 kB的RAM,500 ns转换时间的A/D转换器,片上事件管理器提供了可以满足各种电机控制要求的PWM接口和I/O功能,此外片内还集成了SPI,SCI和CAN控制器。

2 TMS320LF2407A 与 AD9852 的硬件接口电路

在本系统中, TMS320LF2407A 的功能是计算所要产生信号的波形参数,并发送控制字到 AD9852 内部的控制寄存器,以实现可编程的任意信号发生。数据的传输有串行、并行2种方式,串行传输速率最大为10 MHz,并行传输速率最大为100 MHz。为了节约DSP资源,在满足系统要求的前提下,采取串口连接方式,利用 TMSLF2407A 片内的串行外设接口(SPI)控制 AD9852 。接口电路的原理框图如图1所示。

3 AD9852 的串行通信工作过程

AD9852 的串行接口与 TMS320LF2407A 的SPI接口兼容,通过5个端口即可实现串行数据的传输控制。PRD/CSB是复用信号,在串行工作状态下CSB作为 AD9852 串行总线的片选信号,I/O RESET是串口总线复位信号,SCLK是串口时钟信号,系统采用的是2线串口通信模式,使用SDIO端口进行双向输入输出操作,I/O UD是更新时钟信号。串行通信工作的时序如图2所示。

AD9852 的串行通信周期分为2个阶段,SCLK的前8个上升沿对应于指令周期,在指令周期中,用户向 AD9852 的串口控制器发送命令字来控制随后进行的串行数据传输。数据传输周期从SCLK的第9个上升沿开始,输入数据在时钟上升沿写入,输出的数据则在时钟的下降沿读出。由串口传送的数据首先被写入I/O缓存寄存器中,当系统接收到有效的更新信号时,才将这些数据写入内部控制寄存器组,完成相应的功能。当完成了通信周期后, AD9852 的串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字。

当I/O SESET引脚出现一个高电平输入时,将会立即终止当前的通信周期,当I/O RESET引脚状态回到低电平时, AD9852 串口控制器认为接下来的8个系统时钟的上升沿对应的是下一个通信周期的指令字,这一点对保持通信的同步十分有益。

4 2片 AD9852 同步工作

实现2片 AD9852 输出信号波形相位同步的关键是使他们工作在相同的系统时钟下,每个 AD9852 的系统时钟之间的相位误差最大不能超过1个周期。 AD9852 的系统时钟可由参考时钟直接提供,或将参考时钟通过内部的时钟倍频器放大而成。异步的更新时钟经过 AD9852 内部的边沿检测电路后与系统时钟同步,形成上升沿,触发内部控制寄存器更新内容。因此,要实现2片 AD9852 的同步,必须使其参考时钟与更新信号的上升沿同步。下面是确保2片 AD9852 同步工作需要注意的一些要点。

4.1 参考时钟信号

AD9852 的参考时钟有差分输入和单端输入2种形式,由于差分时钟在脉冲边沿具有更短的上升和下降时间以及最小的抖动率,可以有效地降低2片 AD9852 参考时钟间的相位误差,因此本系统采用了参考信号差分输入的方式。对于差分输入方式,输入端信号可以是方波或正弦波,推荐使用MAXIM公司的 MAX9371 ,他可以将普通时钟信号转化成系统所需的差分时钟信号。为了实现参考时钟同步,令2片 AD9852 合用一个晶振,晶振输出的信号先分别传给两个差分时钟生成器,经过转化后输入2片 AD9852 。为了使每片 AD9852 参考时钟信号在传输过程中的延迟时间一致,PCB布线时必须确保时钟信号走线距离相同。

4.2 更新时钟信号

在对 AD9852 进行编程时,串行输入的数据被缓存在内部的I/O缓冲寄存器中,不会影响到 AD9852 的工作状态;在更新时钟信号的上升沿到来后,触发I/O缓冲寄存器把数据传送给内部控制寄存器,这时才能完成相应功能,实现对输出信号的控制。更新时钟信号的产生有2种方式,一种是由 AD9852 芯片内部自动产生,用户可以对更新时钟的频率进行编程来产生固定周期的内部更新时钟;另一种是由用户提供外部更新时钟,此时 AD9852 I/OUD引脚为输入引脚,由外部控制器提供信号。要实现2片 AD9852 同步,必须确保他们的更新时钟信号的上升沿同时来临,因此系统采取外部时钟更新的方式。使用DSP的一个I/O端口与 AD9852 的I/O UD相连接,可以通过软件的方式实现对更新时钟信号上升沿的精确控制。对外部更新时钟信号的布线要求同参考时钟一样。

4.3 参考时钟倍频器

AD9852 的工作时钟高达300 MHz,为了降低时钟信号的干扰,系统应采用低频时钟信号源,然后通过 AD9852 片内的参考时钟倍频器,对外部参考时钟实现4~20倍频。参考时钟倍频器的锁相环电路有2个工作状态:锁定状态和获得锁定状态。在锁定状态,系统时钟信号和参考时钟信号可以保持同步。但当给 AD9852 发送控制指令时,在其参考时钟倍频器工作后的短暂时间内,锁相环不能立刻锁定,仍然工作在获得锁定状态。而此时传送到 AD9852 相位累加器的系统时钟周期的个数是不可控的,这可能导致2片 AD9852 的输出信号之间相位不同步,因此系统初始化以后,一定要先确保锁相环进入锁定状态,然后才能更新 AD9852 内部的各种控制字。 AD9852 片内锁相环锁定的典型时间约为400μs,建议至少留出1 ms时间使锁相环进入锁定状态。

5 AD9852 的控制流程

(1)给系统上电,由DSP向 AD9852 发出复位信号,此信号需要至少保持10个参考时钟周期的高电平。

(2)将S/P SELECT置0,选择串行数据输入方式。

(3)依次给每个 AD9852 发送控制字,使每个 AD9852 工作状态由缺省的内部更新时钟模式改变成外部时钟更新模式。

(4)将 AD9852 时钟倍频器工作的控制字依次写入每个 AD9852 的I/O缓冲寄存器中,然后由DSP发出外部更新时钟,更新每个 AD9852 内部控制寄存器。

(5) DSP发出外部更新信号,至少等待1.0 ms时间使 AD9852 内部锁相环锁定。然后由DSP发送有关信号波形参数给 AD9852 ,对他们的内部控制寄存器内容进行同步更新,使2片 AD9852 输出同步的模拟信号。

6 结语

使用DSP控制 AD9852 产生的爆震信号和凸轮轴信号,在精确度和实时性两个方面都能够满足发动机电控单元硬件在环仿真系统的要求。在此系统的基础上,可以进一步扩展为多片DDS同步使用,适用于更多硬件在环仿真系统。

你们想了解更多的IC资讯吗?那么请进[url]www.dzsc.com[/url]