3.Makefile工程管理

3.Makefile工程管理

一、体验

在前面的笔记里可以看到,要编译一个简单的工程需要的编译步骤是很多的。前面还是只有一个汇编文件,在一个工程里,会有很多文件的,如果像前面的那种编译方式是很不可靠的。这就需要Makefile工程管理。

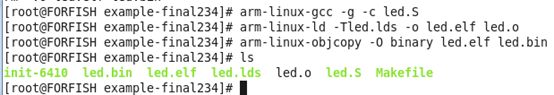

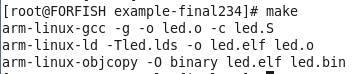

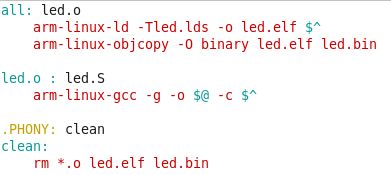

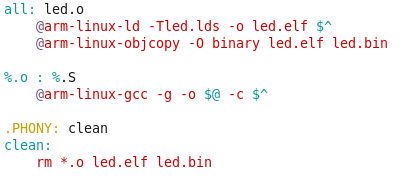

例如前面的那个led.S,要编译成led.bin的步骤:图1-1:

arm-linux-gcc -g -c led.S

arm-linux-ld -Tled.lds -o led.elf led.o

arm-linux-objcopy -O binary led.elf led.bin

图1-1

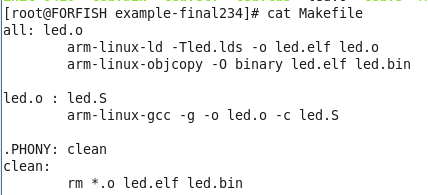

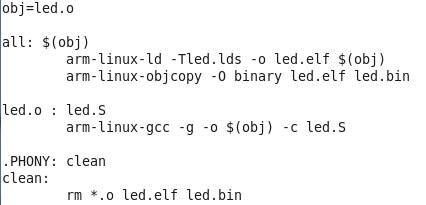

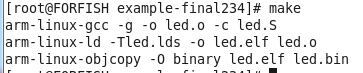

经过上面的三个步骤,编译出了led.bin。看到里面也有一个Makefile文件,里面的内容:图1-2:

all: led.o

arm-linux-ld -Tled.lds -o led.elf led.o

arm-linux-objcopy -O binary led.elf led.bin

led.o : led.S

arm-linux-gcc -g -o led.o -c led.S

.PHONY: clean

clean:

rm *.o led.elf led.bin

图1-2

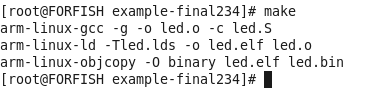

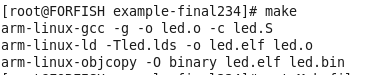

在该目录下执行make,效果:图1-3:

图1-3

看到,一个make命令和上面的一堆命令得到相同的结果。所以学习makefile是很必要的。

二、Makefile的用途:

使用GNU make工具来管理工程是很重要的。一个Makefile工程会让编译一个工程变得简单。只需要一个make命令即可。Make的执行主要依赖于一个Makefile文件。该文件是一系列的编译、链接等规则。这些规则包括如何编译工程中的源文件,如何产生目标文件。

三、Makefile的构成:

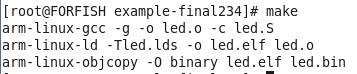

一个Makefile的构成其实很简单,就是规则和变量。所谓的规则就是如何产生目标文件。规则的格式:图1-4:

图1-4

特别注意的是,缩进是按Tap键来的。

例如前面的这个Makefile:

all: led.o

arm-linux-ld -Tled.lds -o led.elf led.o

arm-linux-objcopy -O binary led.elf led.bin

led.o : led.S

arm-linux-gcc -g -o led.o -c led.S

.PHONY: clean

clean:

rm *.o led.elf led.bin

all是最终目标,led.o是生产最终目标的依赖,下面的命令就是利用依赖,通过命令产生最终目标。

led.o也是一个目标,只是不是最终目标,它的依赖是led.S,通过命令产生目标led.o。

在Makefile中还有一个伪目标概念。所谓的为目标就是只有命令,没有依赖的目标称之为伪目标:

在上面的例子中,用.PHONY声明一个伪目标clean。该伪目标执行的操作是:

rm *.o led.elf led.bin

最终目标:如果用户没有指定要执行某一条规则,make会默认执行makefile中的第一条规则,而这条规则中的目标称之为最终目标。

下面指定makefile生成的目标,与不指定生成的目标:图1-5:

图1-5

可以看到,当make后面跟指定的目标是,他会执行产生该目标,当没有加要产生的目标时,默认产生的是最终目标。如上图1-5:

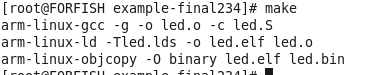

四、Makefile中的变量:

注意Makefile中的变量是没有类型的。

下面就是把变量引入上面的Makefile中:图1-6:

obj=led.o

all: $(obj)

arm-linux-ld –Tled.lds –o led.elf $(obj)

arm-linux-objcopy –O binary led.elf led.bin

led.o : led.S

arm-linux-gcc –g –o $(obj) –c led.S

.PHONY: clean

clean:

rm *.o led.elf led.bin

图1-6

编译,能够顺利生成应用程序。图1-7:

图1-7

上面就是Makefile文件中变量的定义和使用。上面看不出简洁,这是因为该程序太简单了。

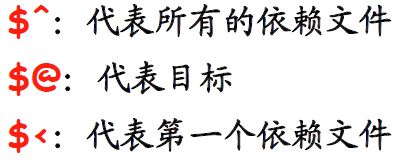

在Makefile中除了上面用户自定义变量外,Makefile中还有系统默认的变量:图1-8:

图1-8

下面就把系统自定义的三个变量加入到上面的那个Makefile文件:图1-9:

all: led.o

arm-linux-ld -Tled.lds -o led.elf $^

arm-linux-objcopy -O binary led.elf led.bin

led.o : led.S

arm-linux-gcc -g -o $@ -c $^

.PHONY: clean

clean:

rm *.o led.elf led.bin

图1-9

可以正常运行:

这就是简化Makefile的一部分。

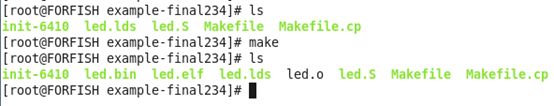

当makefile中有多个相同的类型的文件,通过相同的命令,得到相同类型的目标文件的时候可以使用如下的方法简化。首先编译一下该工程:图1-10:

这是该工程的Makefile:

all: led.o

arm-linux-ld -Tled.lds -o led.elf $^

arm-linux-objcopy -O binary led.elf led.bin

%.o : %.S

arm-linux-gcc -g -o $@ -c $^

.PHONY: clean

clean:

rm *.o led.elf led.bin

图1-10

这样当有很多个.S文件要编译成.o文件的时候,使用上面的这种简化方式就使得Makefile工程简介了许多。

上面是Makefile的基本用法。

五、去掉回显:

在上面的操作中发现,当执行make命令的时候,会显示编译的过程叫回显,当工程很大的时候,这回显的时间也是很费时间的。所以去回显是很必要的。去回显其实很简单就是在命令前加@符号:图1-11:

没加@前:

加入@之后:

图1-11

从上面的运行结果看到,在命令前加@之后,编译生成led.bin的时候没有回显了。

六、Makefile参数:

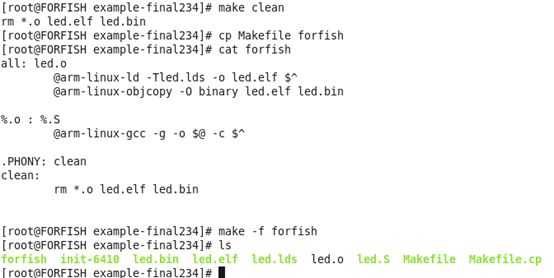

最后要注意的是在Makefile工程中,不是非必要工程文件必须命名为Makefile,这是为了方便,可以根据需要命名的。只是编译工程的命令不同而已。例如工程文件的名字叫forfish。编译的过程如下图1-12:

命令是:make –f forfish:就是make命令+参数-f+工程文件:

图1-12

可以看到编译的工程的结果跟前面的效果一样的。