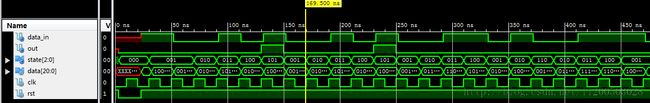

状态机的应用之序列检测器的实现与仿真

序列检测器的作用就是将一个指定的序列从一个数字码流中提取出来,本例将设计一个' 10010 ’序列检测器,data为输入的数字码流,data_in 为每过一个时钟所提取到的data中的一个值。本设计用到了一个简单的 Moore状态机,八个状态分为空闲 Idle 和k1~k7,为了方便用手绘了该状态机的状态转换图,还算比较清楚吧(- ,-) , 其中输入A对

应程序中的data_in ,当状态state为k5时,认为检测到10010序列,此时out为1。

CODE:

module seq_detector(data_in,data,out,clk,rst,state

);

input clk,rst,data_in; //检测10010序列

input [20:0]data;

output wire out;

output reg [2:0] state;

parameter idle=3'b000;

parameter k1=3'b001;

parameter k2=3'b010;

parameter k3=3'b011;

parameter k4=3'b100;

parameter k5=3'b101;

parameter k6=3'b110;

parameter k7=3'b111;

assign out=(state==k5)?1:0;

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

state<=idle;

end

else begin

case(state)

idle: if(data_in==1)

state<=k1;

else

state<=idle;

k1: if(data_in==0)

state<=k2;

else

state<=k1;

k2: if(data_in==0)

state<=k3;

else

state<=k6;

k3: if(data_in==1)

state<=k4;

else

state<=k7;

k4: if(data_in==0)

state<=k5;

else

state<=k1;

k5: if(data_in==0)

state<=k3;

else

state<=k1;

k6: if(data_in==0)

state<=k2;

else

state<=k1;

k7: if(data_in==0)

state<=k7;

else

state<=k6;

default state<=idle;

endcase

end

end

endmodule

TESTBENCH:

module testbench;

// Inputs

reg [20:0] data;

reg clk;

reg rst;

// Outputs

wire data_in,out;

// Instantiate the Unit Under Test (UUT)

seq_detector uut (

.data(data),

.data_in(data_in),

.out(out),

.clk(clk),

.rst(rst)

);

assign data_in=data[20];

initial begin

// Initialize Inputs

clk = 0;

rst = 1;

// Wait 100 ns for global reset to finish

#3

rst=0;

#20

rst=1;

// Add stimulus here

data=21'b 1100_1010_0101_0011_01001;

end

always #10 clk=~clk;

always@(posedge clk)

begin

#2 data={data[19:0],data[20]};

end

endmodule