WINCE6.0+I.MX515下A61485显示屏(驱动IC ST7789V)调试

平台:WINCE6.0+I.MX515

显示屏驱动IC:ST7789V_SPEC_V1.0

1. 左边花屏问题

图1

调整SRC\DRIVERS\IPUV3\DISPLAY \panels.h文件中

PANEL_INFOg_PanelArray[NUM_SUPPORTED_PANELS]下面的值 UINT32HSYNCWIDTH; // HSync widthin pixel clock cycles UINT32HSTARTWIDTH; // HStartwidth in pixel clock cycles UINT32HENDWIDTH; // HEnd widthin pixel clock cycles

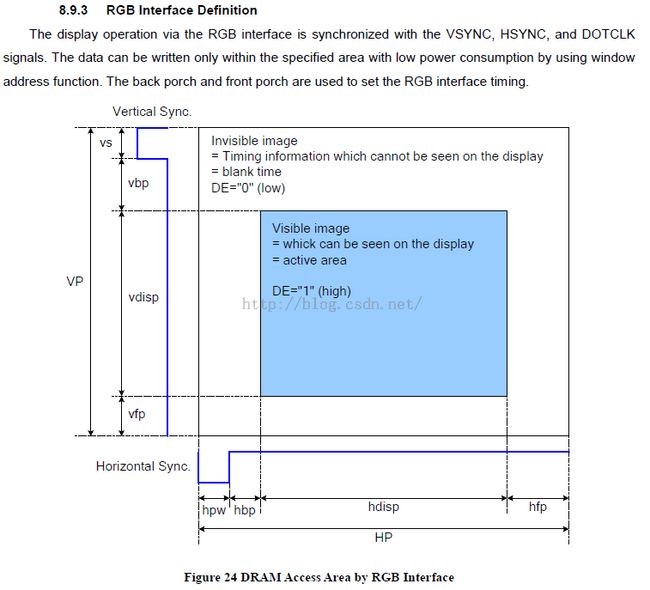

先来给出显示屏驱动IC VSYNC和HSYNC相关的RGB接口定义图:

图2

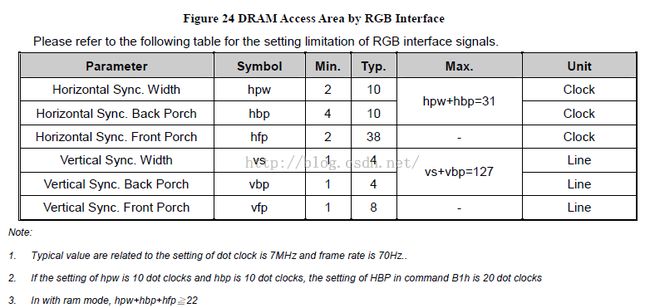

再来看驱动IC中对同步参数的要求:

图3

根据时序参数的要求,我们把上面的值分别由6、2、4改为10、10、38就OK了。

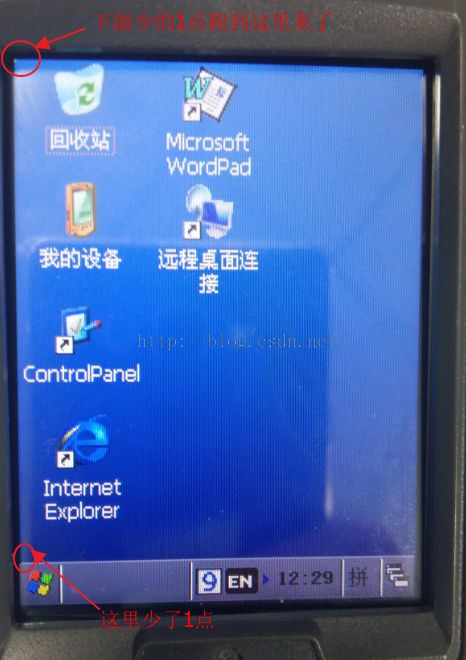

2. 显示屏左上角一个白点问题

图4

这个问题调试第1个问题哪些参数解决不了问题,先来看驱动IC相关的时序要求:

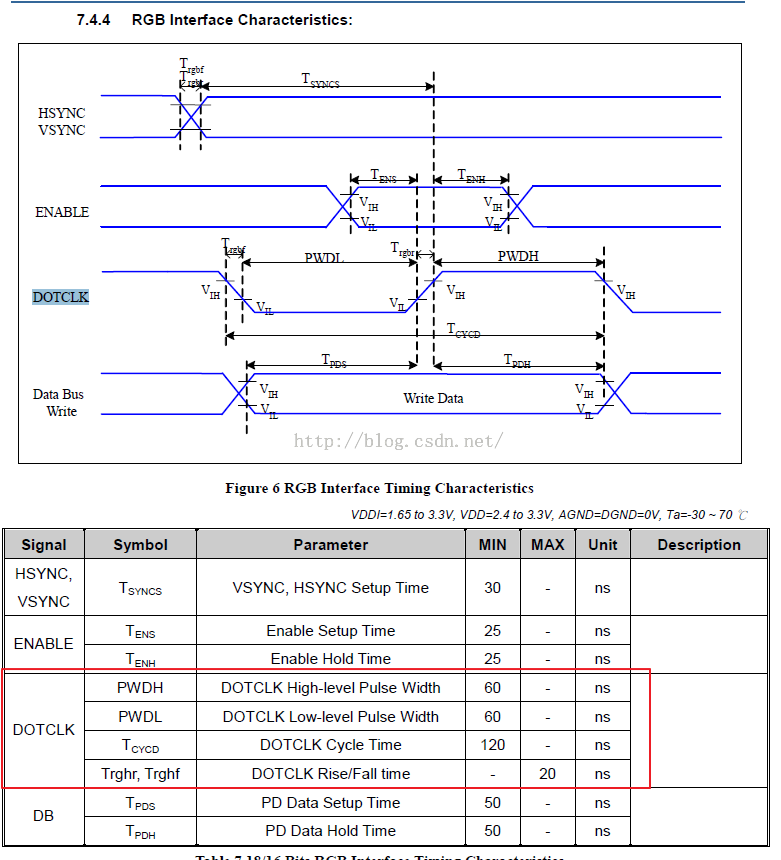

图5

代码中相关的参数:

INTPIX_CLK_UP; // Pixelclock up position, in ns INTPIX_CLK_DOWN; // Pixelclock down position, in ns

这个3个值分别为4、42。这里把PIX_CLK_UP由4改为20就OK了,对应的设置函数是DI下面的DIConfigureBaseSyncClockGen(),如下:

// Up and Down edge position values haveunits of HSP CLK periods

// Multiplied by 2 because there is onefractional bit in the

// register field.

dwEncodedUpPos = (DWORD)((LONGLONG)dwUpPos* g_dwHSPCLKFreq * 2 / 1000000000);

dwEncodedDownPos =(DWORD)((LONGLONG)dwDownPos * g_dwHSPCLKFreq * 2 / 1000000000);

if (di_sel == DI_SELECT_DI0)

{

INSREG32BF(&g_pIPUV3_DI0->DI0_BS_CLKGEN0,

IPU_DI_BS_CLKGEN0_DI_DISP_CLK_PERIOD, dwDIClkDivider);

INSREG32BF(&g_pIPUV3_DI0->DI0_BS_CLKGEN0,

IPU_DI_BS_CLKGEN0_DI_DISP_CLK_OFFSET, dwOffsetClocks);

INSREG32BF(&g_pIPUV3_DI0->DI0_BS_CLKGEN1,

IPU_DI_BS_CLKGEN1_DI_DISP_CLK_UP,dwEncodedUpPos);

INSREG32BF(&g_pIPUV3_DI0->DI0_BS_CLKGEN1,

IPU_DI_BS_CLKGEN1_DI_DISP_CLK_DOWN,dwEncodedDownPos);

}

else

{

INSREG32BF(&g_pIPUV3_DI1->DI1_BS_CLKGEN0,

IPU_DI_BS_CLKGEN0_DI_DISP_CLK_PERIOD, dwDIClkDivider);

INSREG32BF(&g_pIPUV3_DI1->DI1_BS_CLKGEN0,

IPU_DI_BS_CLKGEN0_DI_DISP_CLK_OFFSET, dwOffsetClocks);

INSREG32BF(&g_pIPUV3_DI1->DI1_BS_CLKGEN1,

IPU_DI_BS_CLKGEN1_DI_DISP_CLK_UP,dwEncodedUpPos);

INSREG32BF(&g_pIPUV3_DI1->DI1_BS_CLKGEN1,

IPU_DI_BS_CLKGEN1_DI_DISP_CLK_DOWN,dwEncodedDownPos);

}

HSP_CLK—Internalhigh-speed processing clock: up to 133 MHz,是IPUV3EX的时钟,最高位133MHz。

PIX_CLK_UP=4的意义是4/(2*HSP_CLK)=15ns,满足不了图5中最少的60ns要求,我这里改为20,也就是20/(2*HSP_CLK)=75ns,但如果同时也把PIX_CLK_DOWN改为20,显示的却是花屏,这个值应该是在合理范围内的,不知道为什么会这样。