一位全加器 VHDL设计与实现

作者:chenjieb520

一.设计目的

熟悉Quartus II的VHDL文本设计流程全过程,学习组合电路的设计,仿真和测试。

二.设计内容

设计一位全加器,给出程序的设计、软件编译、仿真分析、硬件测试及详细实验过程。

三.程序设计原理

实验步骤:

(1) 新建一个QuartusⅡ工程,用以在DE2平台上实现所要求的电路。

(2) 建立一个VHDL文件,实现一位全加器电路,完成编译。

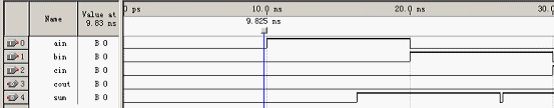

(3) 新建一个波形文件,进行仿真分析,验证功能。

(4) 参照DE2平台的引脚分配表分配引脚,用SW2~SW0作为输入ain bin cin,DE2平台上的LEDR0输出sum, LEDR1输出cout。

(5) 编译工程,完成后下载到FPGA中。

(6) 拨动波段开关并观察LED灯的显示,以验证设计的功能是否正确。

原理:

本实验的原理是利用两个一位的半加器来组成一个一位的全加器。在程序设计中,利用组件化的思想来调用两个功能比较简单的半加器来实现功能稍加复杂的全加器。而一位半加器的设计思想就是利用真值表来进行设计即可。真值表如下:

| a |

b |

so |

co |

| 0 |

0 |

0 |

0 |

| 0 |

1 |

1 |

0 |

| 1 |

0 |

1 |

0 |

| 1 |

1 |

0 |

1 |

四.程序流程图

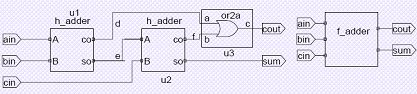

电路图:

程序流程图:由于本程序的逻辑设计比较简单,这里就不画程序流程图。程序的主要逻辑设计就是根据半加器的真值表进行设计的。

五.源程序

//h_adder.vhdl

library ieee;

use ieee.std_logic_1164.all;

entity h_adder is

port (a,b:in std_logic ;co,so:out std_logic);

end entity h_adder;

architecture fh1 of h_adder is

begin

so<=NOT(a XOR (NOT b));

co<=a AND b;

end architecture fh1;

// or2a.vhdl

library ieee;

use ieee.std_logic_1164.all;

entity or2a is

port (a,b:in std_logic;c:out std_logic );

end entity or2a;

architecture one of or2a is

begin

c<=a OR b;

end architecture one;

// adder.vhdl

library ieee;

use ieee.std_logic_1164.all;

entity adder is

port(ain,bin,cin:in std_logic;cout,sum:out std_logic);

end entity adder;

architecture fd1 of adder is

component h_adder

port(a,b:in std_logic;co,so:out std_logic);

end component;

component or2a

port(a,b:in std_logic;c:out std_logic);

end component;

signal d,e,f:std_logic;

begin

u1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e);

u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum);

u3:or2a port map(a=>d,b=>f,c=>cout);

end architecture fd1;

六.调试过程

七.遇到的问题及解决方法

1、由于这是第一的实验,对于实验的环境很是陌生,导致在刚开始的时候,对整个程序的运行的过程很不熟悉,后来在老师的指导下,才懂得一些入门的知识。

2、在VHDL编程中,实体名要和文件名一样,否则编译就会出现错误。

3、在建立一般的仿真波形时,要注意将相应的引脚添加进来,在对各个输入的引脚进行波形编辑,然后尽量地遍历所有的情况。

4、在将程序下载的硬件的时候,不能只是单纯地就进行下载,应该在设置所有的硬件参数之后,要对整个项目重新编译一次,这样才能保证下载到机器上的程序是最新的,否则是得不到我们想要的结果的。

5、总之,经过这次的实验,了解到了VHDL的一般编写过程,如何进行调试和分析运行结果。

八.参考文献

EDA技术与VHDL(第二版) 潘松 黄继业 编著