Modelsim使用详解(一)

作者:李秋凤,华清远见嵌入式学院讲师。

FPGA的设计过程中,modelsin是我们最常用的工具之一,大部分FPGA的初学者对Modelsim的使用不熟练,也只能使用最简单的一部分,其实它的功能很强打,在这里我就modelsim的使用写个详细文档,希望对初学者有帮助。

共13部分,今天先写第一部分,每周写一部分,大家要有耐心,嘿嘿。

一、概述

ModelSim能够对VHDL、Verilog、SystemVerilog、SystemC和混合语言设计的仿真和验证。

有三种仿真模式

(1)基本仿真流程,这是最简单的仿真方法,不用建立工程

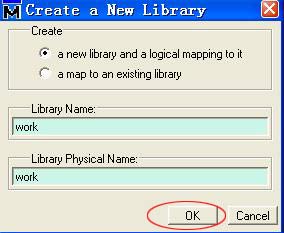

创建work库:打开modelsim,在file菜单下,点new-library

Work 是modelsim默认的库,也可以改成自己有含义的名字, 也可以通过输入命令建立库 如在modelsim〉 vlib wwww回车,则建立了wwww库

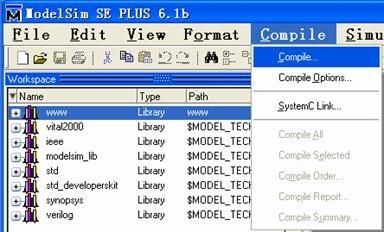

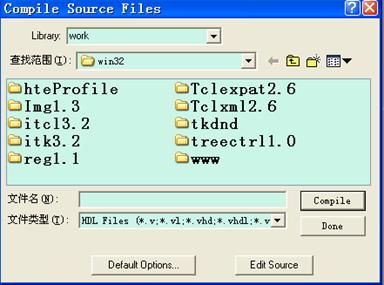

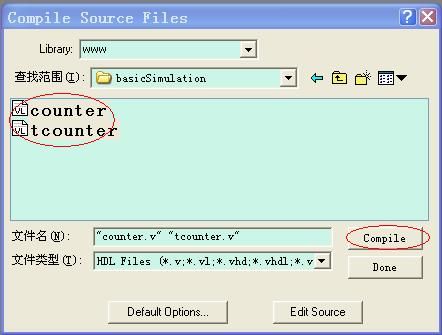

编译文件

建立库完成后,你该把你的设计文件在库里面进行编译,方法有菜单操作和命令输入两种菜单操作:在copile菜单下点compile选项,或 在modelsim〉下输入 vcom ,回车。

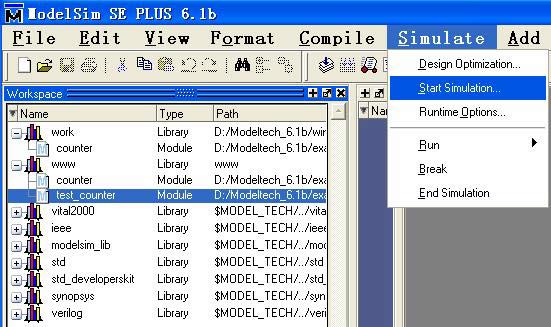

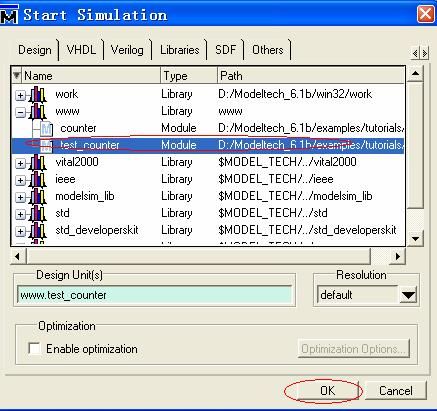

运行仿真

编译完成后,唤醒testbench文件进行仿真,在菜单simulate菜单下点击start simulate….按钮或在命令行输入Vsim命令,回车

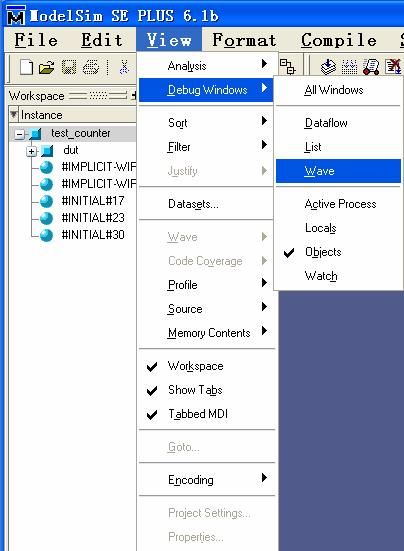

在菜单栏,点击view- Debug Windows –Wave,打开wave窗口,

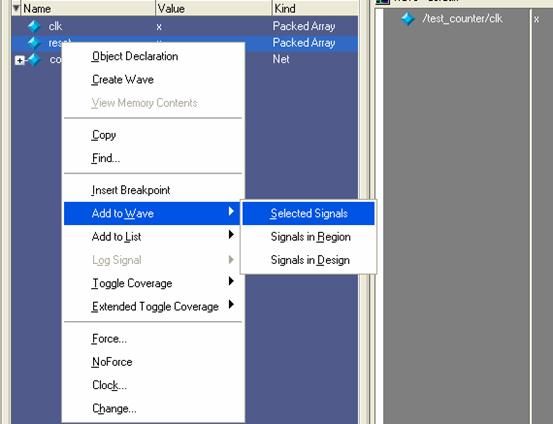

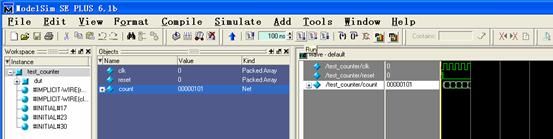

添加需观测的信号进入波形文件。可以右键添加,也可以用鼠标直接拖进wave中

运行

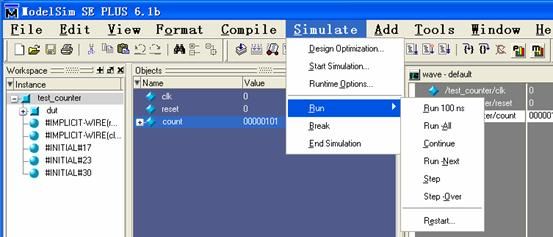

输入 run 100ns回车 或simulate—run—run 100ns 或

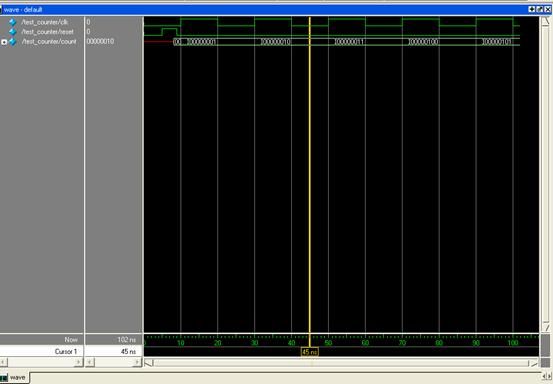

观看仿真波形

(2)通过建立项目进行仿真

仿真流程如下图

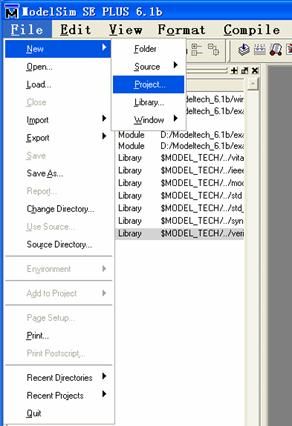

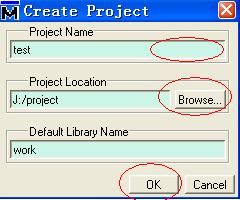

首先建立一个工程

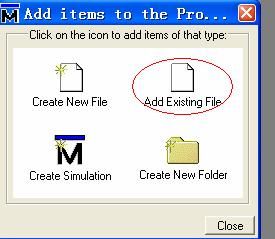

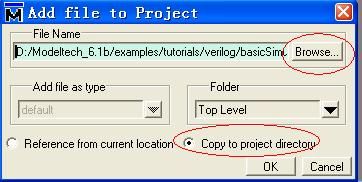

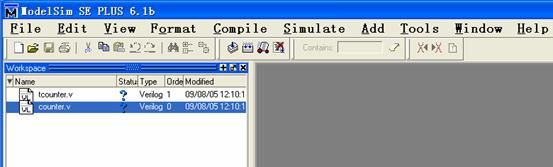

添加文件

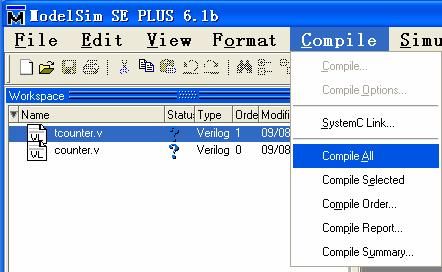

编译文件

菜单操作:在copile菜单下点compile all选项,或 在modelsim〉下输入 vcom ,回车在工程目录下编译文件

运行仿真,此过程同前面相同添加信号进入波形文件 运行 上面三过程均与前面相同。

(3)多个库的仿真流程

在modelsim仿真中,也可以使用多个库进行仿真,仿真流程如下。

前两个步骤与前面相同,链接资源库,在命令栏输入Vlog,回车,然后选择要编译的源库。