段地址和偏移地址

8086:关于物理地址=段地址*16+偏移

首先我们知道8086中段地址是从能被10H整除的地址开始的,即地址最后一位都是0(16进制表示)。这样在设计CPU时就没有必要表示这个最后一个0了。例如FFFF[0]H,这个地址,假设段地址是FFFFH,那么它的偏移地址就是0000H了。 因为CPU在设计时去掉了一个16进制的0,所以要乘以10H(十进制的16)。

8086CPU有20位地址总线,这个总线是指的外部总线(也就是CPU与内存交换数据时的总线的宽度),可以传送20位的地址,达到1M的寻址能力。

8086CPU又是16位的结构,在内部一次处理,暂时存储,传输的地址为16位,这里的16位指的是CPU内部总线(也就是CPU内各个寄存器直接传送数据时的总线宽度)。

所以如果从CPU内部直接发送数据只能送出16位的地址,表现出的寻址能力只有64KB(小于前面说的1M)。为了解决这个问题,8086CPU在内部采用两个16位的地址(一个是段地址,一个是偏移地址)合成一个20位的地址。所以合成的方法就是:段地址*16+偏移=物理地址。

段地址*16的意思是:让段地址左移4位,比如2000H左移4位,成为20000H。再加上一个16位的偏移地址。这样就是20位的物理地地址了。

实模式与保护模式

16位实模式下,一个物理地址由段地址和偏移地址两部分组成,段地址在16位段寄存器中,然后在指令中用16位偏移地址寻址。物理地址=段地址*0x10+偏移地址

------关于“实模式与保护模式”定义的相关内容,参看:http://www.cppblog.com/mydriverc/articles/30719.html

----对于8086/8088来说计算实际地址是用绝对地址对1M求模。8086的地址线的物理结构:20根,也就是它可以物理寻址的内存范围为2^20个字节,即1 M空间,但由于8086/8088所使用的寄存器都是16位,能够表示的地址范围只有0-64K,这和1M地址空间来比较也太小了,所以为了在8086/8088下能够访问1M内存,Intel采取了分段寻址的模式:16位段基地址:16位偏移EA。其绝对地址计算方法为:16位基地址左移4位+16位偏移=20位地址。

----如果访问100000h~10FFEFh之间的内存(大于1M空间),则必须有第21根地址线来参与寻址(8086/8088没有)。因此,当程序员给出超过1M(100000H-10FFEFH)的地址时,因为逻辑上正常,系统并不认为其访问越界而产生异常,而是自动从0开始计算,也就是说系统计算实际地址的时候是按照对1M求模的方式进行的,这种技术被称为wrap-around

-----在80286以及更高系列的PC中,即使A20 Gate被打开,在实模式下所能够访问的内存最大也只能为10FFEFH,尽管它们的地址总线所能够访问的能力都大大超过这个限制。为了能够访问10FFEFH以上的内存,则必须进入保护模式

32位保护模式下,问题变复杂了。首先要明白,保护模式保护什么?保护的是:分清楚各个程序使用的存储区域,不允许随便跨界访问。然后,怎么保护?方式是:为内存里的每段地址空间定义一些安全上的属性,比如可以被多少优先级的代码写入,是不是允许执行等。这个时候,段寄存器远远不能满足要求了。原因有二:段寄存器只有32位,保存不了这么多信息;段寄存器个数有限,不能保存内存中所有段的信息。

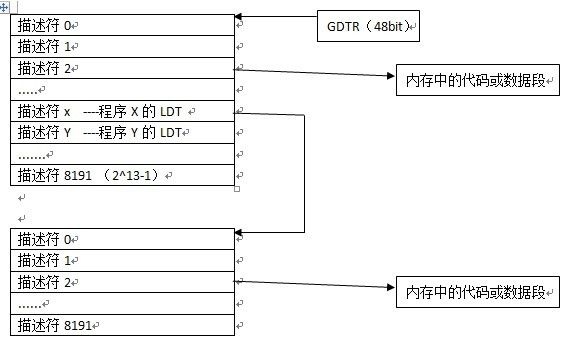

intel的工程师们就想出了用64位的段描述符表(descriptor table)来存储所有的段信息,段描述符表存放在内存的某个位置。段寄存器不再表示段首地址了,而是表示这个段在段描述符表的索引信息。通过段寄存器在段描述符表里找到关于这个段的所有信息。

但是,段描述符表不止一个。首先有一个全局段描述符表,简称GDT,每个程序都有自己的段描述符表,简称LDT。相应的,80386里面引入了两个新的寄存器,一个是48位的全局描述符表寄存器GDTR,指向全局描述符表GDT的首地址,一个是16位的局部描述符表寄存器LDTR,它的值随时变化,总是指向CPU当时正在执行的那个程序的局部描述符表LDT。注意,这里不说指向LDT的首地址,是因为LDTR和CS、DS等段寄存器一样,存放的也是在GDT中的索引值,而不是实际地址。

那么段寄存器里的索引到底是GDT的索引还是LDT得索引呢?下面是实模式下段寄存器的结构

TI位为0 表示从全局描述符表中找

TI位为1 表示从局部描述符表中找

以保护模式下的虚拟地址xxxx:yyyyyyyy(16位段地址,32位偏移)为例,首先看xxxx的TI位,如果为0,那么在GDT中以xxxx的高13位作为索引找出段描述符,这样就得到了段基址、段限长、优先级等信息。如果TI位为1,那么从LDTR中得到当前程序的LDT在GDT中的索引,再在GDT里找到这个LDT的描述符,得到LDT的首址,然后再以xxxx的高13位为LDT里的索引找到段基址、段限长、优先级等信息。(LDTR,TR的内容只在第一次运行任务0的时候(init/main.c)需要“人工”加载,之后都由CPU自动完成)

在保护模式下,虚拟地址xxxx:yyyyyyyy(16位段地址,32位偏移),xxxx为段选择子,是段描述符相对于GDT首地址的偏移字节数。通过xxxx找到段描述符从而得到段首址,再加上偏移地址得到实际地址。

GDTR寄存器的结构

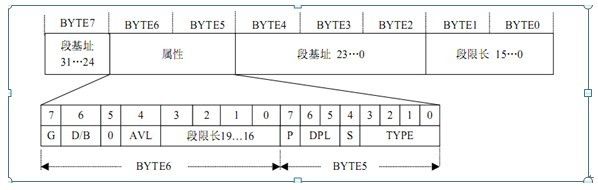

GDT和LDT里的描述符的通用结构

各属性位作用如下:

G:G=0时,段限长的20位为实际段限长,最大限长为2^20=1MB

G=1时,则实际段限长为20位段限长乘以2^12=4KB,最大限长达到4GB

D/B:当描述符指向的是可执行代码段时,这一位叫做D位,D=1使用32位地址和32/8位操作数,D=0使用16位地址和16/8位操作数。如果指向的是向下扩展的数据段,这一位叫做B位,B=1时段的上界为4GB,B=0时段的上界为64KB。如果指向的是堆栈段,这一位叫做B位,B=1使用32位操作数,堆栈指针用ESP,B=0时使用16位操作数,堆栈指针用SP。

AVL:available and reserved bit 通常为0

P:存在位,P=1表示段在内存中

DPL:特权级,0为最高特权级,3为最低,表示访问该段时CPU所需处于的最低特权级

S:S=1表示该描述符指向的是代码段或数据段;S=0表示系统端(TSS、LDT)和门描述符

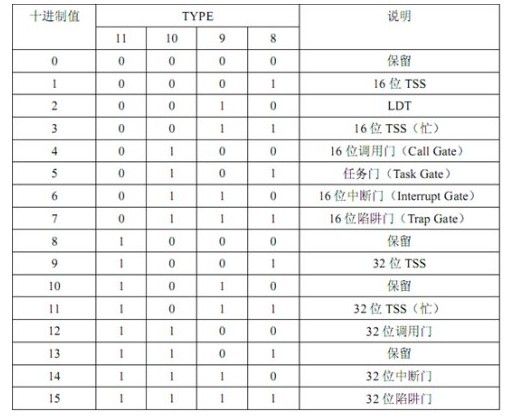

TYPE:类型,和S结合使用

S=1且TYPE<8时,为数据段描述符。数据段都是可读的,但不一定可写。

S=1且TYPE>=8时,为代码段描述符。代码段都是可执行的,一定不可写,不一定可读

S=0时,描述符可能为TSS、LDT和4种门描述符

GDT和LDT的关系