第四节:C64+ DSP 的CPU及存储器体系中存储器关系

这里以DM6437为例,这个DSP是非常经典的一个。

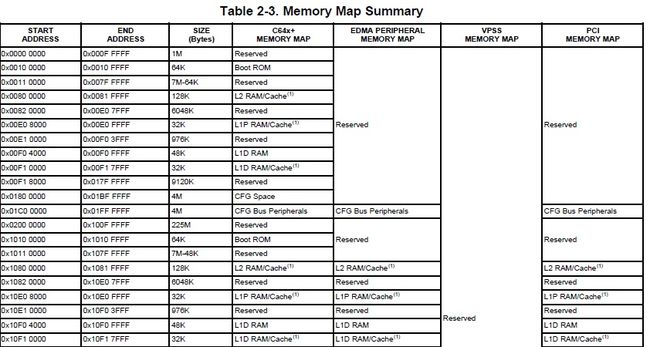

我们首先看memry-map

表4.1 memry map

通过上表可以看到L1P,L1D,L2的存储器区间范围。真正有用的是从C64+和EDMA peripheral memory map 视角都能访问的内存范围,若是有一方是reserved状态,则

不能访问。因此

LIP RAM/CACHE的范围是0x10e08000~0x10e0ffff 共32K

L1D RAM的范围是0x10f04000~0x10f0fff 共48K

L1D RAM/CACHE的范围是0x10f10000~0x10f17fff 共32K

L2 RAM/CACHE 的范围是0x10800000~0x1081ffff 共128K

总结:除了L1D有一段48K的是纯RAM外(不可作缓存使用),其他几段都是可以作为存储器或者缓存混合使用的。

从某种意义上说,这是6437的先进之处,正是因为L1D中多了这么一段RAM。所以性能很好。

当然,你可以通过DSPBIOS或者cmd文件去配置RAM或者CACHE的范围,

这里给出示例代码

MEMORY {

CACHE_L2 : origin = 0x10810000, len = 0x10000

CACHE_L1D : origin = 0x10f10000, len = 0x8000

DDR2 : origin = 0x80000000, len = 0x2000000

L1DSRAM : origin = 0x10f04000, len = 0xc000

IRAM : origin = 0x10800000, len = 0x10000

CACHE_L1P : origin = 0x10e08000, len = 0x8000

}

注意:

DDR2的区间是肯定从0X8000000开始的。

IRAM和CACHE_L2共同分配了L2的地址范围。前者表示RAM,后者表示cache

L1DSRAM和CACHE_L1D共同分配了L2的地址范围。前者表示RAM,后者表示cache

可能有些人还是不明白RAM和CACHE到底啥区别:这里简单的说下

RAM即可你可以访问的区域,比如通过malloc申请的区域。你可以往这区域内写数据,也可以读数据。

CACHE即你不可以访问的区域,一般由CPU自己控制,你不可以往这个区域内写数据,也不可以读数据,完全是CPU在控制