使用ModelSim自动生成状态机FSM的状态转换图

HDL代码设计中重要的内容之一就是设计程序的状态机FSM,状态转换控制着整个程序的流程,为了理解程序,我们经常需要把状态机的状态转换图画出来,这样看起来很直观,但是,有没有办法自动生成状态转换图呢?

在ISE或者ModelSim中有没有这样的工具呢?

答案是肯定的,ModelSim中即有这样的工具,下面以ISE13.4和ModelSim6.5为例,使用一段最简单的状态机代码说明如何操作来自动生成状态转换图。

代码如下:

module Top_fsm(

input clk,

input rst,

output reg fsm_out

);

parameter IDLE = 3'd0, S1 = 3'd1, S2 = 3'd2, S3 = 3'd3, S4 = 3'd4, S5 = 3'd5;

reg [2:0] status;

always @ (posedge clk)

if(!rst)begin

status <= IDLE;

end

else begin

case(status)

IDLE:begin

fsm_out <= 1'b0;

status <= S1;

end

S1:begin

fsm_out <= 1'b1;

status <= S2;

end

S2:begin

fsm_out <= 1'b0;

status <= S3;

end

S3:begin

fsm_out <= 1'b1;

status <= S4;

end

S4:begin

fsm_out <= 1'b0;

status <= S5;

end

S5:begin

fsm_out <= 1'b1;

status <= IDLE;

end

default:begin

fsm_out <= 1'b0;

end

endcase

end

endmodule

我们在ISE中直接切换到ModelSim仿真模式,如图所示:

双击Simulate Behavioral Model,将打开ModelSim。

在ModelSim中执行View---FSM list命令,如下图所示:

然后就会发现ModelSim左边这部分的标签多了一项,如下面两幅图的对比:

未执行命令前是这样子的:

执行完命令是这样子的:

![]()

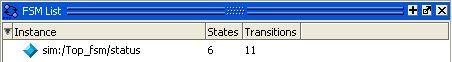

这时候在FSM List标签下,可以看到如下内容,双击之:

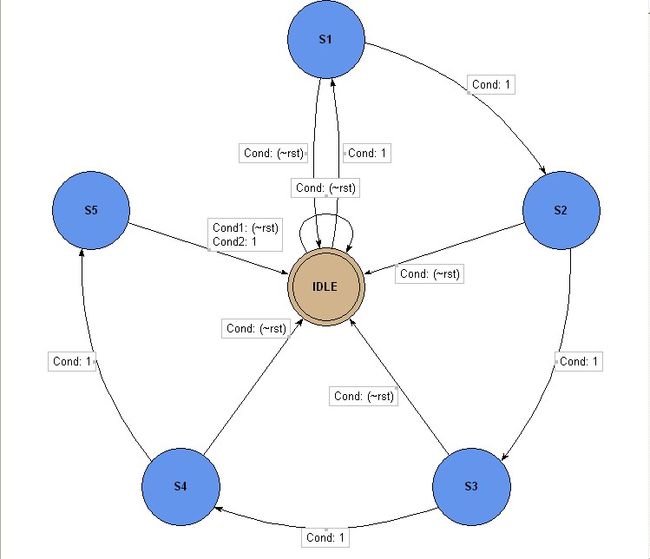

于是出现了下面的状态转换图:

这时观察生成的状态转换图发现,所有的状态都在复位的情况下返回了状态IDLE,这是我们不期望的,仔细观察这时的菜单栏可以发现,有一个FSM View项:

将Show Transitions to "Reset"项前面的对勾去掉,就会发现不显示复位情况下返回状态IDLE了,如下图所示:

细心的人会发现状态到了S5并未返回IDLE,但在前面的状态转换图中的确有Cond2:1这种状态转到状态IDLE,这估计是软件所导致的吧。

简单的应用就这些,深一些的功能自己好好探索吧。

最后说一下这种自动生成的状态转换图的缺点:因为它默认生成的状态转换图一定是一个圆,所以当你的状态比较复杂时,并非是一个简单的切换时,生成的状态转换图也就会很乱很乱,可读性直接下降,不知道是可以可调节或者有什么更好的生成工具?