Davinci调试环境的搭建(一)

说明:本文的内容都是本人从网上各处copy拼凑而来,若是出本书的话,实在是非常符合“编著”这个词(虽然我心里对这个词总有些不以为然),所以标的是原创,却并没有什么原创性,只是略加整理,便于参考而已。

Davinci调试环境的搭建

目录

一、达芬奇(DaVinci)技术介绍

1、TMS320DM6446的结构特点

2、达芬奇技术及其芯片的应用和开发前景

二、Davinci调试环境搭建的几大步

1、Davinci调试环境搭建所需软件

2、Davinci调试环境搭建及使用总体步骤

三、搭建linux环境

四、安装ARM程序的编译环境

1、安装ARM交叉编译环境

(1)搭建MontaVista Linux开发环境

(2)安装dvsdk工具链

(3)dvsdk工具链的路径配置

2、系统配置

(1)设置NFS

(2)设置DHCP服务器

(3)配置samba服务

(4)设置DVEVM

(5)编译调试工具框图

五、安装DSP程序的编译环境

1、安装CCS3.3

2、安装TDS560USB驱动

(1)安装TDS560USB驱动时注意事项

(2)USB设备驱动程序安装

(3)安装TDS560USB仿真器工具软件

3、进行CCS setup

4、运行CCS

六、程序编译

1、在Windows上编译DSP端运行库

2、在Linux中编译DSP可执行程序

3、在Linux中编译ARM可执行程序

4、启动板卡,执行程序

六、脱机运行

1,烧写uboot

(1)编译uboot

(2)烧写uboot

2,烧写Linux内核

(1)编译Linux内核

(2)烧写Linux内核

3,烧写根文件系统

(1)制作ramdisk

(2)烧写ramdisk

一、 达芬奇(DaVinci)技术介绍

面对日新月异的多媒体标准与应用,德州仪器公司提供了基于达芬奇(DaVinci)技术及其产品(如TMS320DM6446)的解决方案,以简化数字视频创新。包括基于数字信号处理器(DSP)的片上系统(SoC)以及多媒体编解码器、应用编程接口(API)、框架与开发工具等。

达芬奇技术由达芬奇处理器、达芬奇软件、达芬奇开发工具和达芬奇技术支持系统等组件优化构成。其中,达芬奇处理器基于业界最高性能的DSP平台-TI TMS320C6000,利用了TI最新的C64x+ DSP内核。达芬奇处理器包含基于可扩展、可编程DSP的SoC(可从DSP与ARM内核进行定制),同时还包含优化的加速器与外设,以全方位满足各种数字视频终端设备对价格、性能以及功能等多方面的需求。

运行于达芬奇处理器之上的达芬奇软件充分利用芯片资源。其内置于可配置的框架内,通过流行操作系统内部已公布的API提供,以实现快速的软件实施。

达芬奇技术为各种应用领域及设计提供一系列工具与套件,其中包括:低成本入门工具、完整的开发套件以及参考设计,以加速OEM厂商的设计与开发进程。ARM/DSP集成开发环境(IDE)、操作系统工具以及DSP工具使开发人员能够在熟悉的环境中编程,同时还能获得达芬奇技术的优势。TMS320DM6446芯片就是达芬奇(DaVinci)技术的杰出代表。

1、TMS320DM6446的结构特点

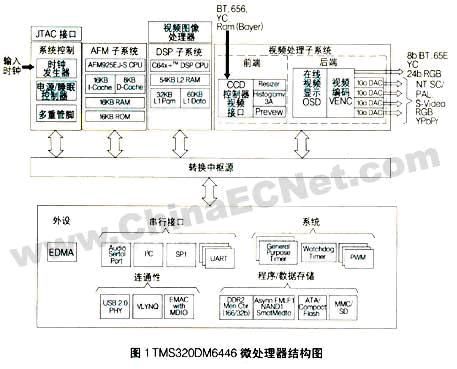

TMS320DM6446的结构图如图1所示。

结构特点

(1)高性能。采用低功耗、高性能的32位TMS320C64x内核和ARM926EJ-S内核,工作频率分别高达594MHz和297MHz;支持多媒体处理技术,采用的是TMS320C64x DSP内核,增强了对视频和音频的解码能力。

(2)低功耗。多电源管理模式,双内核电压供给为1.6V;ARM926EJ-S内核具有16KB指令和8KB数据Cache,TMS320C64x DSP内核具有32KB程序RAM/Cache、80KB数据RAM/Cache及64KB未定义RAM/Cache;支持3.3V或1.8V的I/O接口和存储器接口。

(3)专用的视频图像处理器和视频处理子系统。专用的视频图像处理器用于对视频数据处理;视频处理子系统包括1个视频前端输入接口和1个视频末端输出接口,视频前端输入接口用于接收外部传感器或视频译码器等图像,视频末端输出接口输出图像到SDTV、LCD、HDTV等显示屏上。

(4)存储容量。有256MB的32位DDR2 SDRAM存储空间,128MB的16位FLASH存储空间。

(5)众多的外设。64通道增强型DMA控制器;串行端口(3个UARTs、 、SPI、音频串口);3个64位通用定时器;10/100M以太网;USB2.0端口;3个PWM端口;多达71个通用I/O口;支持MMC/SD/CF卡等。

(6)时钟控制。时钟源:27MHz系统振荡器;24MHzUSB振荡器。

ARM926EJ-S内核

ARM926EJ-S内核是采用管道化流水线的32位RISC处理器,同时配备Thumb扩展。它能够处理32位或16位的指令和8位、16位、32位的数据。它通过使用协处理器CP15和保护模块使体系结构得到增强,并提供数据和程序内存管理单元(MMU)。

MMU具有两个64项的转换旁路缓存器(TLB)用于指令和数据流,每项均可映射存储器的段、大页和小页。为了保证内核周期的存取指令和数据,提供了独立的16K字节指令Cache和8K字节数据Cache,指令和数据Cache都是通过VIVT四路连接。另外,还提供一个写缓冲用于提升内核性能,其缓冲数据容量高达17字。

TMS320C64x DSP内核

TMS320C64x DSP内核构建在VelociTI.2体系结构的基础上,是VelociTI.2体系结构的进一步增强,以其C64x内核的先进超长指令字(VLIW)结构,获得当前应用设备所需要的极高性能。

在结构上其特点为:1)C64x片内有2个数据通道、8个功能单元和2个一般目的寄存器文件(A和B)。而8个功能单元和2个寄存器文件又分成了相同的两组,每组占用一个数据通道。两个数据通道之间包含有两个数据交叉通路。2)C64xDSP采用超长指令字(VLIW),即在每个时钟周期最高可提供8条32位指令,总字长为256位的指令包同时分配到8个并行处理单元。在594MHz的时钟频率下,当片内8个处理单元同时运行时,其最大处理能力可以达到4800MIPS。3)C64x DSP具有双16bit扩充功能,芯片能在一个周期内完成双16位的乘法、加减法、比较、移位等操作。C64x通过把DSP运算压缩在较少的周期里,加速通信和图像应用。在增强并行性的扩展中,四组8位/两组16位指令允许每秒进行约90亿次8位乘法上累加周期(MAC)运算。

系统控制功能

TMS320DM6446微处理器的系统控制模块提供了看门狗(WT)、中断控制器、电源管理控制器、复位控制器及2个片上振荡器。

视频处理子系统(VPSS)

TMS320DM6446中的视频处理子系统有两个接口,分别为用于视频输入的视频前端输入(VPFF)接口和用于图像输出的视频末端输出(VPBE)接口。

视频前端输入(VPFE)接口由1个CCD控制器(CCDC)、1个预处理器、柱状模块、自动曝光/白平衡/聚焦模块(H3A)和寄存器组成。CCD控制器可以与视频解码器、CMOS传感器或电荷耦合装置连接;预处理器是一个实时的图形处理器,它把CMOS或CCD得到的原始图形从RGB(三原色)转变为YUV4:2:0编码;柱状模块和H3A模块则提供原始图形信息。

视频末端输出(VPBE)接口由1个在线视频显示处理器(OSD)和1个视频编码器组成。在线视频显示处理器既能够显示两组独立的视频窗口或两组独立的OSD窗口,还可以以1个视频窗口、1个OSD窗口和1个属性窗口的形式显示。视频解码器以54MHz进行D/A转换,可以提供NTSC/PAL、S等格式的视频或音频输出。

电源管理

TMS320DM6446有三种电源管理模式:备用电源模式、低功耗运行模式和正常运行模式。备用电源模式下运行的功耗是最低的,DSP核和视频处理器子系统都不运行,除了通用I/O、UART和PWM运行以外,其他的外设都不运行,而且只有27MHz时钟工作。低功耗模式下,仅仅运行一些ARM的基本功能,DSP核和视频处理器子系统也都不运行,除了通用I/O、UART、PWM、SPI和定时器运行以外,其他的外设都不运行,而且也是只有27MHz时钟工作。正常运行模式下,除了所有的模块和外设都可以运行外,两个时钟也正常运行。

外部存储器接口

在TMS320DM6446中有与几种形式的外部存储器接口:异步EMIFA(NOR Flash、SDRAM)、NARD Flash以及CF卡等。异步EMIFA包括1个8位或16位数据线,1个24位地址总线,4个专用片选线,支持的存储接口有NAND、ATA/CF、主机端接口。NAND接口包括的存储类型有NAND卡、SM卡和xD卡。DDR2存储控制器用于与16位或32位的DDR2 SDRAM连接。DDR2 SDRAM在达芬奇(DaVinci)技术中有很重要的作用,它可以用来缓冲视频输入图形数据,作为OSD的缓冲器,存储ARM和DSP代码等。

外围控制模块

TMS320DM6446有3个64位通用定时器和3个PWM模块。其中定时器0和1具有32位通用定时器模式,定时器2具有WD模式以及产生ARM和DSP中断,产生EDMA同步事件。而PWM模块既可以作周期性记数,也可以作重复记数。

TMS320DM6446微处理器有64个独立的通道高级DMA控制器。DMA控制器用于可响应内部和外部设备的请求。在MPU TI926(ARM926EJ-S)运行条件下,完成外部寄存器/内部寄存器和外部设备之间的数据传输。DMA的设置取决于MPU TI926(ARM926EJ-S)内核。

GPIO外设控制器可以配置通用管脚为输入或输出。当配置为输出管脚时,写内部寄存器可以控制输出管脚的状态。当配置为输入管脚时,可以通过读内部寄存器的状态位知输入的状态。此外,GPIO外设可以产生CPU中断和DMA事件。GPIO管脚以16个为一列,它支持的功能如下:54个1.8V GPIO管脚和17个3.3V GPIO管脚;从O列开始每列有8个GPIO[0:7]中断,可以在上升沿或下降沿触发中断等。

TMS320DM6446支持多种串行接口:(1)3个UART接口,其中UART2具有的功能是:对于接收器和发送器的FIFO有16个字节的存储空间,DMA既可以接收数据也可以发送数据,在自动控制时可编程自动发送请求和自动清除请求,还具有内部诊断功能。(2)SPI外设,它提供一个可编程长度寄存器,通过3或4线接口与其他SPI设备连接。(3) 接口,可以与遵守总线2.1规约的其设备连接。在模式下通过2条串行总线可以发送/接收8位数据。(4)音频串行接口(ASP),ASP模块具有的功能为:全双工通信,直接与媒体数字信号编解码器、A/D、D/A等连接。

此外,还有USB2.0接口,USB2.0具有以下特点:作为外设时可达到高速480Mb/s和全速12Mb/s传输,作为主机时可以进行高速、全速和低速传输,与标准的UTMI+ PHY接口连接,FIFO中还有4K可编程RAM。

以太网控制器(EMAC)模块在网络与芯片间提供一个接口,支持10M/100M以太网的访问,支持硬件流控制和QOS。

数据输入/输出管理(MDIO)模块是用于管理与芯片相连的PHY设备。主机软件使用MDIO模块配置每个PHY对应EMAC的参数,找回对应结果,以便于在EMAC模块配置所需的参数。

2、达芬奇技术及其芯片的应用和开发前景

由于达芬奇技术成功实现数字视频需要四大要素的最新进步,即:处理器、开发工具、软件以及系统专业技术,因此达芬奇技术为数字视频的当前变革打下基础。

显著降低系统成本

达芬奇技术利用数字信号处理与集成电路专业技术来提供高度集成的片上系统(SoC),集成了可编程数字信号处理器(DSP)内核、ARM处理器、视频加速协处理器、存储器、I/O带宽、平衡的内部互连以及专用外设组合,使硬件材料清单成本降低了50%。

集成代码的数字视频子系统的 硬件和软件

为了真正意义上地让开发人员克服最初的障碍并且加快产品上市进程,完整的达芬奇软件架构涵盖低级的OS驱动程序乃至应用API,使开发人员无需投入过多力量编写及优化编解码器或进行DSP编程,即能够实现数字视频功能,从而使开发人员能够将精力集中到开发可最大化附加值的产品上来。例如,在过去开发电子器件时,即使是最基本的功能,工程师们也需要进行栅极布局;而现在开发人员不再需要了解其视频应用中实施具体CODEC引擎(如:MPEG-2、H.263、WMA9)的细节,开发人员无需修改上层应用代码即可以使用理想CODEC的API,显著简化视频CODEC处理的具体低层次细节,使开发人员可以立足于开发的功能性。

通过提供可随时投产的软件,如硬件驱动器、人工优化的CODEC、以及用于管理网络中音频/视频同步和数据流的应用代码的整体组合,达芬奇技术使开发人员无需了解如何编程DSP即可实现一流的视频功能。

开放式的平台开发

数字视频系统的复杂性主要归因于开发人员必须创建和管理的众多组件。达芬奇技术通过提供开放式平台来降低系统复杂性-在该平台之上,TI及其第三方合作伙伴已经开发和集成了构成数字视频系统所需要的各种组件。 达芬奇技术提供的开放式开发平台同时也扩展到了应用程序。达芬奇软件初始将支持Linux,将来会陆续支持其他操作系统。Linux支持的内容包括外设驱动器、实时应用管理、应用级API以及可随时投产的代码。

二、 Davinci调试环境搭建的几大步

1、Davinci调试环境搭建所需软件

Davinci的程序分DSP程序及ARM程序,DSP程序我们在CCS中编辑和编译,ARM程序在Source Insight中编辑,在Linux中的dvsdk1.3工具链下编译。

以下是我们在开发过程中所使用的软件:

Windows:

CCS 3.3 DSP程序编译环境

TDS560USB 仿真器驱动

VMWare5.0 虚拟机软件

Source Insight 3.5 软件工程编辑工具

Tera Term 串口控制软件

DVFlasher 串口flash烧写工具

UltraEdit-32 文本编辑工具

Linux:

dvsdk1.3 ARM交叉编译工具链

GCC3.2.2 编译器

VI 文本编辑工具

同时,在linux下需要启动如下服务:

samba 通过网络提供与windows共享文件功能

nfs 通过网络给Davinci板卡提供根文件系统

tftp 通过网络下载文件至Davinci板卡

dhcp 动态分配IP

2、Davinci调试环境搭建及使用总体步骤

Davinci调试环境搭建及使用可以分成5大步:

1, 搭建linux环境

2, 安装arm编译环境

3, 搭建CCS环境

4, 编译库,生成x64P,由ARM端可执行程序调用运行

5, 编译uboot并烧写进flash,烧写内核及根文件系统