Nand Flash驱动程序编写指南-2

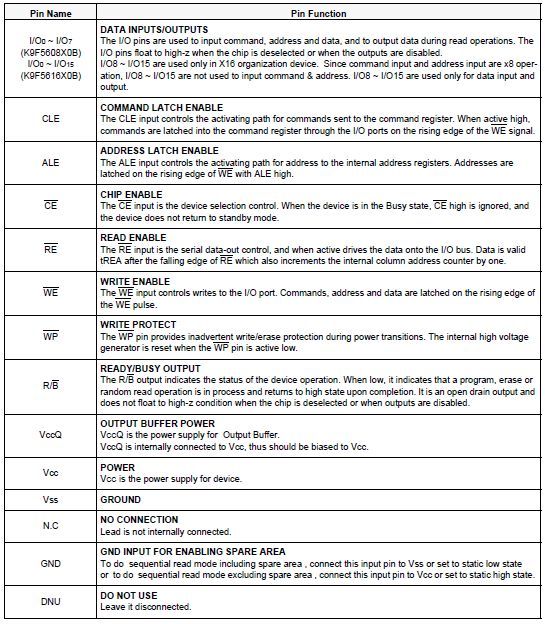

接下来看一下Nand Flash的引脚(Pin)定义,数据手册截图如下:

上图是常见的Nand Flash所拥有的引脚(Pin)所对应的功能,简单翻译如下:

I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据;

CLE:Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能;

ALE:Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能;

CE#:Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作;

RE#:Read Enable,读使能,在读取数据之前,要先使CE#有效;

WE#:Write Enable,写使能, 在写取数据之前,要先使WE#有效;

WP#:Write Protect,写保护;

R/B#:Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成;

Vcc:Power,电源;

Vss:Ground,接地;

N.C:Non-Connection,未定义,未连接。

注意:在数据手册中,对于一个引脚定义,有些字母上面带一横杠的,那是说明此引脚/信号是低电平有效,如上面的RE头上有个横线,就是说明,此RE是低电平有效,此外,为了书写方便,在字母后面加“#”,也是表示低电平有效,比如我上面写的CE#;如果字母头上什么都没有,就是默认的高电平有效,比如上面的CLE,就是高电平有效。上面的锁存指令,如命令锁存使能(Command Latch Enable,CLE) 地址锁存使能(Address Latch Enable,ALE),是用于指定Nand Flash处理的指令类型,是数据、地址还是命令等,因为Nand Flash只有8个I/O,而且是复用的,可以传数据、地址或是命令,此处加上锁存就可以实现通道复用了。

那么,为什么Nand Flash只有8个引脚呢?好处如下:

1、减少外围引脚:相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2、提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nand flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

接下来列举下Nand Flash的一些典型特性:1、页擦除时间是200us,有些慢的有800us;2、块擦除时间是1.5ms;3、页数据读取到数据寄存器的时间一般是20us;4、串行访问(Serial access)读取一个数据的时间是25ns,而一些旧的nand flash是30ns,甚至是50ns;5、输入输出端口是地址和数据以及命令一起multiplex复用的。了解了这些后,可以在读写时有目的的加上一定的时延后再去读状态,效果更佳。

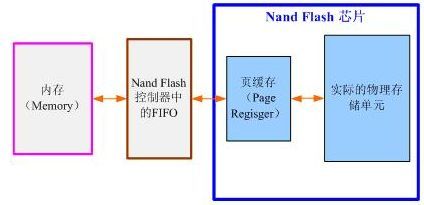

另外,Nand Flash中还有一个比较特殊的设计就是页缓存的概念,在数据手册上,其描述为Page Register,由于Nand Flash读取和编程操作来说,一般最小单位是页,所以nand flash在硬件设计时就考虑到这一特性,对于每一片,都有一个对应的区域,专门用于存放将要写入到物理存储单元中去的或者刚从存储单元中读取出来的整页的数据,这个数据缓存区,本质上就是一个buffer。正是因为有些人不了解其内部结构,才容易产生这样的误解,以为内存里面的数据,通过Nand Flash的FIFO,写入到Nand Flash里面去,就以为立刻实现了实际数据写入到物理存储单元中了。而实际上,只是写到了这个页缓存中,只有等你发了对应的编程第二阶段的确认命令0x10之后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理存储单元中去。下图为Nand Flash数据流向:

Nand Flash中一个块Nand Flash中,一个块中含有1个或多个位是坏的,就成为其为坏块。坏块的稳定性是无法保证的,也就是说,不能保证你写入的数据是对的,或者写入对了,读出来也不一定对的。而正常的块,肯定是写入读出都是正常的。

坏块有两种:一种是出厂的时候,也就是,你买到的新的,还没用过的Nand Flash,就可以包含了坏块。此类出厂时就有的坏块,被称作factory (masked)bad block或initial bad/invalid block,在出厂之前,就会做对应的标记,标为坏块。具体标记的地方是,对于K9F5608,是块中第一个页的Spare区中的第6个字节,如果不是0xFF,就说明是坏块。相对应的是,所有正常的块,好的块,里面所有数据都是0xFF的。

第二种是在使用过程中产生的,由于使用过程时间长了,在擦块除的时候,出错了,说明此块坏了,也要在程序运行过程中,发现,并且标记成坏块的。具体标记的位置,和上面一样。这类块叫做worn-out bad block。

对于坏块的管理,YAFFS就是通过一个叫做blockinfo的结构体记录在要挂载的设备描述结构体中的,对应的会有一个字节记录好块,坏块的信息,以及坏块是出厂就有的,还是后来使用产生的,在加载完驱动之后,如果你没有加入参数主动要求跳过坏块扫描的话,那么都会去主动扫描坏块,建立必要的blockinfo,以备后面坏块管理所使用。

对于坏块的标记,本质上,也只是对应的flash上的某些字节的数据是非0xFF而已,所以,只要是数据,就是可以读取和写入的。也就意味着,可以写入其他值,也就把这个坏块标记信息破坏了。对于出厂时的坏块,一般是不建议将标记好的信息擦除掉的。

下面是几个常见的Nand Flash相关的重要技术:

【片选无关(CE don’t-care)技术】

很多Nand flash支持一个叫做CE don’t-care的技术,字面意思是不关心是否片选,即在如果不片选的情况下,仍能对flash进行操作,这个技术主要用在不需要选中芯片却还可以继续操作的这些情况:在某些应用,如录音,音频播放等,中、外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对Nand Flash操作,这样的串行(Serial Access)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要Nand Flash内部去自己操作,将数据读取除了或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总结起来简单解释就是:由于某些外部应用的频率比较低,而Nand Flash内部操作速度比较快,所以具体读写操作的大部分时间里面,都是在等待外部命令的输入,同时却选中芯片,产生了多余的功耗,此“不关心片选”技术,就是在Nand Flash的内部的相对快速的操作(读或写)完成之后,就取消片选,以节省系统功耗。待下次外部命令/数据/地址输入来的时候,再选中芯片,即可正常继续操作了。这样,整体上,就可以大大降低系统功耗了。

【带EDC的拷回操作以及Sector的定义(Copy-Back Operation with EDC & Sector Definition for EDC)】

Copy-Back功能,简单的说就是,将一个页的数据,拷贝到另一个页。如果没有Copy-Back功能,那么正常的做法就是先要将那个页的数据拷贝出来放到内存的数据buffer中,读出来之后,再用写命令将这页的数据,写到新的页里面。

而Copy-Back功能的好处在于,不需要用到外部的存储空间,不需要读出来放到外部的buffer里面,而是可以直接读取数据到内部的页寄存器(page register)然后写到新的页里面去。而且,为了保证数据的正确,要硬件支持EDC(Error Detection Code)的,否则,在数据的拷贝过程中,可能会出现错误,并且拷贝次数多了,可能会累积更多错误。对于错误检测来说,硬件一般支持的是512字节数据,对应有16字节用来存放校验产生的ECC数值,而这512字节一般叫做一个扇区。对于2K+64字节大小的页来说,按照512字节分,分别叫做A,B,C,D区,而后面的64字节的oob区域,按照16字节一个区,分别叫做E,F,G,H区,对应存放A,B,C,D数据区的ECC的值。

Copy-Back编程的主要作用在于去掉了数据串行读取出来,再串行写入进去的时间,所以,而这部分操作,是比较耗时的,所以此技术可以提高编程效率,提高系统整体性能。

【多片同时编程(Simultaneously Program Multi Plane)】

对于有些新出的Nand Flash,支持同时对多个片进行编程,比如上面提到的三星的K9K8G08U0A,内部包含4片(Plane),分别叫做Plane0,Plane1,Plane2,Plane3。.由于硬件上,对于每一个Plane,都有对应的大小是2048+64=2112字节的页寄存器(Page Register),使得同时支持多个Plane编程成为可能。 K9K8G08U0A支持同时对2个Plane进行编程。不过要注意的是,只能对Plane0和Plane1或者Plane2和Plane3,同时编程,而不支持Plane0和Plane2同时编程。

【交错页编程(Interleave Page Program)】

多片同时编程,是针对一个chip里面的多个Plane来说的,而此处的交错页编程,是指对多个chip而言的。可以先对一个chip,假设叫chip1,里面的一页进行编程,然后此时,chip1内部就开始将数据一点点写到页里面,就出于忙的状态了,而此时可以利用这个时间,对出于就绪状态的chip2,也进行页编程,发送对应的命令后,chip2内部也就开始慢慢的写数据到存储单元里面去了,也出于忙的状态了。此时,再去检查chip1,如果编程完成了,就可以开始下一页的编程了,然后发完命令后,就让其内部慢慢的编程吧,再去检查chip2,如果也是编程完了,也就可以进行接下来的其他页的编程了。如此,交互操作chip1和chip2,就可以有效地利用时间,使得整体编程效率提高近2倍,大大提高nand flash的编程/擦写速度了。

【随机输出页内数据(Random Data Output In a Page)】

在介绍此特性之前,先要说说,与Random Data Output In a Page相对应的是,普通的,正常的,sequential data output in a page。

正常情况下,我们读取数据,都是先发读命令,然后等待数据从存储单元到内部的页数据寄存器中后,我们通过不断地将RE#(Read Enale,低电平有效)置低,然后从我们开始传入的列的起始地址,一点点读出我们要的数据,直到页的末尾,当然有可能还没到页地址的末尾,就不再读了。所谓的顺序(sequential)读取也就是,根据你之前发送的列地址的起始地址开始,每读一个字节的数据出来,内部的数据指针就加1,移到下个字节的地址,然后你再读下一个字节数据,就可以读出来你要的数据了,直到读取全部的数据出来为止。

此处的随机(random)读取,就是在你正常的顺序读取的过程中,先发一个随机读取的开始命令0x05命令,再传入你要将内部那个数据指针定位到具体什么地址,也就是2个cycle的列地址,然后再发随机读取结束命令0xE0,然后,内部那个数据地址指针,就会移动到你所制定的位置了,你接下来再读取的数据,就是从那个制定地址开始的数据了。nand flash数据手册里面也说了,这样的随机读取,你可以多次操作,没限制的。

请注意,上面所传入的地址,都是列地址,也就是页内地址,也就是说,对于页大小为512Byte的nand flash来说,所传入的地址,应该是小于512+16=528的。

不过,实际在nand flash的使用中,好像这种用法很少的。绝大多数,都是顺序读取数据。

【页编程】

Nand flash的写操作叫做编程Program,编程,一般情况下,是以页为单位的。有的Nand Flash,比如K9K8G08U0A,支持部分页编程,但是有一些限制:在同一个页内的,连续的部分页的编程,不能超过4此。一般情况下,很少使用到部分页编程,都是以页为单位进行编程操作的。一个操作,用两个命令去实现,看起来是多余,效率不高,但是实际上,有其特殊考虑,至少对于块擦除来说,开始的命令0x60是擦除设置命令(erase setup comman),然后传入要擦除的块地址,然后再传入擦除确认命令(erase confirm command)0xD0,以开始擦除的操作。

这种分两步:开始设置,最后确认的命令方式,是为了避免由于外部由于无意的/未预料而产生的噪音,比如,由于某种噪音,而产生了0x60命令,此时,即使被nand flash误认为是擦除操作,但是没有之后的确认操作0xD0,nand flash就不会去擦除数据,这样使得数据更安全,不会由于噪音而误操作。