【转】s3c44b0x开发板之SDRAM配置

最近几个月忙着达芬奇的项目,一个人边学边做赶进度,从底层驱动,再到上层应用,再到DSP优化,天昏地暗,好在自己对这些东西很感兴趣,并不觉得苦。直到项目快要完结,觉得必须得回过头去再把以前的东西系统地看一下了。于是乎就把4年前的ARM7板子翻出来了,抛开操作系统,好好研究一下底层的东西,让自己心里也踏实一些。下面这篇日志的内容刚好和我的开发板的一模一样,索性留下来,作为参考。

上一篇日志都是9月份找工作的时候的了,差不多4个月没写过了,坚持是一种品质,不能懈怠啊~~

原文地址 http://www.cnblogs.com/arci/archive/2011/04/21/2024150.html

----------------------------------以下内容为转载----------------------------------

参考:

高手进阶,终极内存技术指南——完整/进阶版

简单的S3C44B0X Bootloader

1、硬件连接

s3c44b0x开发板上使用的SDRAM芯片为:HY57V641620HGT-HI(4 Banks x 1M x 16Bit Synchronous DRAM)

表1.1、Bank 6/7 地址

NOTE: Bank 6 and 7 must have the same memory size.

注意: Bank 6和Bank 7内存大小必须相同.

表1.2、SDRAM Bank地址配置

HY57V641620HGT-HI(4 Banks x 1M x 16Bit Synchronous DRAM)对应配置为表1.1、1.2高亮部分

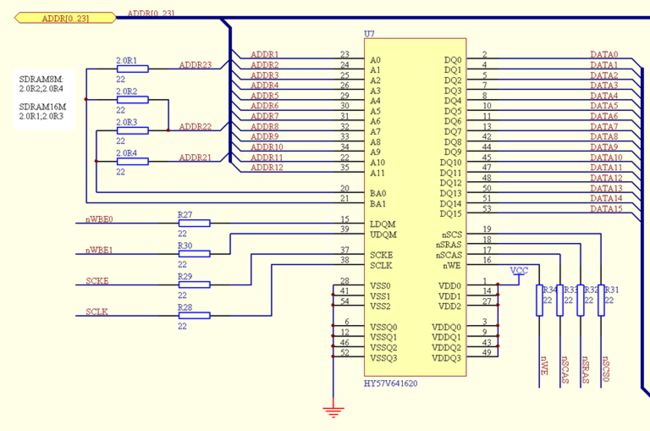

图1.1、Half-word SDRAM Design with Half-word Component

图1.2、s3c44b0x开发板HY57V641620HGT-HI实际电路

2、软件初始化

参考s3c44b0x用户指南可知, 与SDRAM相关的寄存器有:

(1)、总线宽度与等待控制寄存器(BWSCON)

(2)、BANK控制寄存器(BANKCON6: nGCS6)

BANK控制寄存器(BANKCON7: nGCS7)

(3)、刷新控制寄存器(REFRESH)

(4)、BANK大小寄存器(BANKSIZE)

(5)、SDRAM模式寄存器设置寄存器(MRSRB6)

SDRAM模式寄存器设置寄存器(MRSRB7)

2.1、总线宽度与等待控制寄存器(BWSCON)

其中BWSCON与Bank 6和Bank 7相关的位如下:

| BWSCON | Bit | 描述 | 起始状态 |

| ST7 | [31] | 此位决定SRAM映射在bank 7时是否使用UB/LB 0 = 不使用UB/LB ( 引脚[14:11]作为nWBE[3:0] ) 1 = 使用UB/LB ( 引脚[14:11]作为nBE[3:0] ) 由于s3c44b0x开发板上使用的是SDRAM, 所以此位设置为0 |

0 |

| WS7 | [30] | 此位决定bank 7上的等待状态 |

0 |

| DW7 | [29:28] | 这两位决定bank 7的总线宽度 00 = 8-bit, 01 = 16-bit, 10 = 32-bit HY57V641620HGT-HI为16-bit, 所以此为设置为01 |

0 |

| ST6 | [27] | 此位决定SRAM映射在bank 6时是否使用UB/LB 0 = 不使用UB/LB ( 引脚[14:11]作为nWBE[3:0] ) 1 = 使用UB/LB ( 引脚[14:11]作为nBE[3:0] ) 由于s3c44b0x开发板上使用的是SDRAM, 所以此位设置为0 |

0 |

| WS6 | [26] | 此位决定bank 6上的等待状态 |

0 |

| DW6 | [25:24] | 这两位决定bank 6的总线宽度 00 = 8-bit, 01 = 16-bit, 10 = 32-bit HY57V641620HGT-HI为16-bit, 所以此为设置为01 |

0 |

注: All types of master clock in this memory controller correspond to the bus clock.

所有此存储器控制器主机时钟的类型与总线时钟相符.

For example, MCLK in DRAM and SRAM is same as the bus clock, and SCLK in SDRAM is also the same as the bus

clock. In this chapter (Memory Controller), one clock means one bus clock.

例如, DRAM和SRAM中的MCLK与总线时钟相同, 并且SDRAM的SCLK也与总线时钟相同, 在这章中(存储器控制器), 1个时钟是指一个总线时钟.

对于Bank 1 ~ Bank 5先不予设置, Bank 0为只读选项, 因此:

BWSCON = 0b 0001 0001 0000 0000 0000 0000 0000 0000 = 0x1100 0000

BANKCON6 - 7与SDRAM相关的寄存器位如下:

| BANKCON6 - 7 | Bit | 描述 | 起始状态 |

| MT | [16:15] | 这两位决定bank 6、bank 7的内存类型 00 = ROM or SRAM, 01 = FP DRAM 10 = EDO DRAM, 11 = Sync. DRAM |

11 |

| Trcd | [3:2] | RAS to CAS delay 00 = 2 clocks, 01 = 3 clocks, 10 = 4 clocks |

10 |

| SCAN | [1:0] | Column address number 列地址数 00 = 8-bit, 01 = 9-bit, 10= 10-bit |

00 |

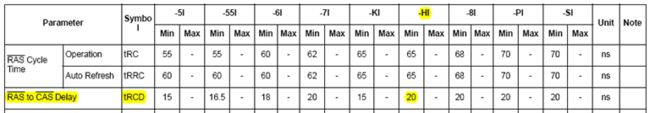

通过查看HY57V641620HGT-HI数据手册可知Trcd = 20ns, 假设系统总线时钟为60MHz, one clock = 1 / (60MHz) = (50 / 3)ns

Trcd = 20ns = 20 / (50 / 3) clock = 1.2 clock = 2 clocks

对于SCAN也可以查看HY57V641620HGT-HI数据手册, 应此SCAN = 00 = 8 - bit

因此, BANKCON6 = BANKCON7 = 0b 1 1000 0000 0000 0000 = 0x00018000

2.3、刷新控制寄存器(REFRESH)

| REFRESH | Bit | 描述 | 起始状态 |

| REFEN | [23] | DRAM/SDRAM刷新使能 0 = 禁止, 1 = 使能(self or CBR/auto refresh) |

1 |

| TREFMD | [22] | DRAM/SDRAM刷新模式 0 = CBR/Auto Refresh, 1 = Self Refresh In self-refresh time, the DRAM/SDRAM control signals are driven to the appropriate level. |

0 |

| Trp | [21:20] | DRAM/SDRAM RAS pre-charge Time(预充电时间) DRAM : 00 = 1.5 clocks, 01 = 2.5 clocks, 10 = 3.5 clocks, 11 = 4.5 clocks SDRAM : 00 = 2 clocks, 01 = 3 clocks, 10 = 4 clocks, 11 = Not support |

10 |

| Trc | [19:18] | SDRAM RC minimum Time 00 = 4 clocks, 01 = 5 clocks, 10 = 6 clocks, 11 = 7 clocks |

11 |

| Tchr | [17:16] | CAS Hold Time(DRAM) 00 = 1 clock, 01 = 2 clocks, 10 = 3 clocks, 11 = 4 clocks 此位为针对DRAM, 对于SDRAM无需设置 |

00 |

| Reserved | [15:11] | 未使用 | 0000 |

| Refresh Counter |

[10:0] | DRAM/SDRAM刷新计数值. 请参考第六章DRAM刷新控制器总线优先级部分. Refresh period = (211-refresh_count+1)/MCLK 例如: 如果刷新周期是15.6us, 系统总线时钟MCLK为60MHz, 那么刷新计数值计算如下: refresh count = 2^11 + 1 - 60x15.6 = 1113 |

0 |

关于刷新:

之所以称为DRAM, 就是因为它要不断进行刷新(Refresh)才能保留住数据, 因此它是DRAM最重要的操作.

刷新操作分为两种: 自动刷新(Auto Refresh, 简称AR)与自刷新(Self Refresh,简称SR).

不论是何种刷新方式, 都不需要外部提供行地址信息,因为这是一个内部的自动操作.

对于AR, SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址.

由于刷新是针对一行中的所有存储体进行, 所以无需列寻址, 或者说CAS在RAS之前有效.

所以, AR又称CBR(CAS Before RAS, 列提前于行定位)式刷新.

由于刷新涉及到所有L-Bank, 因此在刷新过程中, 所有L-Bank都停止工作, 而每次刷新所占用的时间为9个时钟周期(PC133标准),

之后就可进入正常的工作状态, 也就是说在这9个时钟期间内, 所有工作指令只能等待而无法执行.

64ms之后则再次对同一行进行刷新, 如此周而复始进行循环刷新. 显然, 刷新操作肯定会对SDRAM的性能造成影响,

但这是没办法的事情, 也是DRAM相对于SRAM(静态内存, 无需刷新仍能保留数据)取得成本优势的同时所付出的代价.

SR则主要用于休眠模式低功耗状态下的数据保存, 这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存).

在发出AR命令时, 将CKE置于无效状态, 就进入了SR模式, 此时不再依靠系统时钟工作, 而是根据内部的时钟进行刷新操作.

在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令), 只有重新使CKE有效才能退出自刷新模式并进入正常操作状态.

因此DRAM/SDRAM刷新设置为使能, DRAM/SDRAM刷新模式为CBR/Auto Refresh

DRAM/SDRAM RAS pre-charge Time(Trp)可通过查看HY57V641620HGT-HI数据手册, 可知Trp= 20ns, 假设系统总线时钟为60MHz,

one clock = 1 / (60MHz) = (50 / 3)ns, Trp = 20ns = 20 / (50 / 3) clock = 1.2 clock = 2 clocks

one clock = 1 / (60MHz) = (50 / 3)ns, Trp = 65ns = 65 / (50 / 3) clock = 3.9 clock = 4 clocks

关于刷新周期:

那么要隔多长时间重复一次刷新呢? 目前公认的标准是, 存储体中电容的数据有效保存期上限是64ms, 也就是说每一行刷新的循环周期是64ms.

这样刷新速度就是: 行数量/64ms. 我们在看内存规格时, 经常会看到4096 Refresh Cycles/64ms或8192 Refresh Cycles/64ms的标识,

这里的4096与8192就代表这个芯片中每个L-Bank的行数. 刷新命令一次对一行有效, 发送间隔也是随总行数而变化, 4096行时为15.625μs,

8192行时就为7.8125μs.

通过查看HY57V641620HGT-HI数据手册可知: 4096 refresh cycles / 64ms, 1 refresh cycles = 64ms / 4096 = 15.625us

Refresh period = (2^11-refresh_count+1)/MCLK, refresh_count = 2^11 + 1 - Refresh period * MCLK

假设系统总线时钟为MCLK = 60MHz, 那么refresh_count = 2^11 + 1 – 15.625us * 60MHz = 2048 + 1 - 937.5 = 1111.5 = 1112

Refresh Counter = 1112 = 0b 100 0101 1000

因此, REFRESH = 0b 1000 0000 0000 0100 0101 1000= 0x00800458

| BANKSIZE | Bit | 描述 | 初始状态 |

| SCLKEN | [4] | SCLK will be generated only during SDRAM access cycle. SCLK将只在SDRAM存取周期的时候产生. This feature will reduce the power consumption. 此功能将降低功耗. 1 is recommended. 推荐设置为1. 0 = 标准SCLK, 1 = 为了降低功耗的SCLK |

0 |

| Reserved | [3] | 未使用 | 0 |

| BK76MAP | [2:0] | BANK6/7内存映射 000 = 32M/32M, 100 = 2M/2M, 101 = 4M/4M 110 = 8M/8M, 111 = 16M/16M |

000 |

BANKSIZE = 0b 1 0 101 = 0x15

2.5、SDRAM模式寄存器设置寄存器(MRSRB6 - 7)

通过查看s3c44b0x数据手册可知, MRSR6 - 7中只有CAS latency需要设置, 其他位可以采用推荐值

通过查看HY57V641620HGT-HI数据手册可知:

假设系统总线时钟为MCLK = 60MHz < 100MHz, 因此可以选择CAS latency为2CLKs

因此, MRSRB6 = MRSRB7 = 0b 00 0 00 010 0 000 = 0x20

到此s3c44b0x SDRAM配置完成, 各寄存器值如下:

BWSCON = 0b 0001 0001 0000 0000 0000 0000 0000 0000 = 0x11000000

BANKCON6 = BANKCON7 = 0b 1 1000 0000 0000 0000 = 0x00018000

REFRESH = 0b 1000 0000 0000 0100 0101 1000= 0x00800458

BANKSIZE = 0b 1 0 101 = 0x15

MRSRB6 = MRSRB7 = 0b 00 0 00 010 0 000 = 0x20