s3c2440 地址分配硬件连接及其启动原理分析

s3c2440 地址分配硬件连接及其启动原理分析

一.CPU 地址分配:

1. s3c2440A 的存储器控制器有以下特性:

l 大小端(通过软件选择)

l 地址空间:每个bank有128M 的字节(总共1G字节/8个banks)

l 可编程的访问位宽,bank0(16/32 位),其他bank(8/16/32 位)

l 共8个存储器banks

l 6 个是ROM,SRAM 等类型存储器bank (bank0 ---- bank5)

l 2 个是可以作为ROM、SRAM、SDRAM 等存储器bank (bank6 ---- bank7)

l 7 个固定的存储器bank起始地址 (bank0 ---- bank6)

l 最后一个bank 的起始地址可调整 (bank7, 接两片sdram时.接在bank7上的sdram会根据bank6上的结束地址而调整)

l 最后两个bank 大小可编程

l 所有存储器bank的访问周期可编程

l 总线访问周期可通过插入外部wait来延长

l 支持SDRAM 的自刷新和掉电模式

理论上,cpu是32位的.可以寻址的空间为2的32次方,也就是4GB的地址空间.但我们cpu只用了其中一1GB多一点的空间,其它的空间都是未到到.且看下图,我们作一个感性认识:

图1

(1) S3C2440A的存储器管理器提供访问外部存储器的所有控制信号,27位地址信号(ADDR[26:0])、32位数据信号(DATA[31:0])、8个片选信号(nGCS[7:0])、以及读/写控制信号等.

看图1,我们知道.从0x4000 0000 地址开始,有片内SRAM,片内寄存器,还有未使用的空间.这是都是固定的,不能动的.留给我们用户的只有0x0000 0000 到 0x3FFF FFFF这1GB的地址空间给我们用. 1GB的地址空间我们需要30根地址线才能完全寻址完毕,2 的 30次方 刚好等于1GB,但是,芯片引脚上只给出了27根地址()ADDR[26:0]),单靠芯片上的27根引脚,它只能控制128M的空间,那3根线去哪里.其实这3根线用在了3-8译码器(如:000表示00000001,001表示00000010,010表示00000100,011表示00001000等等)的输入端去了,而这个3-8译码器的输出端,就是对应这nGCS0~7,对应着8个bank,用于选择当前处于哪个bank,这样做的好处在于很模块化结构化了,便于管理.不会造成一片和手动去分割地址.

(2) bank0---bank5为固定128MB,bank6和bank7的容量可编程改变,可以是2、4、8、16、32、64、128MB

请看图2

图2

所以.7个固定存储器bank(bank0-bank6)起始地址。bank7的开始地址与bank6的结束地址相连接,但是二者的容量必须相等,s3c2440最小可以支支持2MB(2MB一片,只接bank6) 最大支持是256MB(bank6接128MB,bank7接128MB),另需注意一点就是如果,需要接两片sdram的话,两片的容量大小必须是一样的.看图2就清楚了.

(3) bank0可以作为引导ROM。其数据线宽只能是16位和32位,其它存储器的数据线宽可以是8位、16位和32位

(4) 地址:

0x0000 0000 ----- 0x3FFF FFFF : 分配了8个bank ,每个bank 有128MB寻址空间, 每个bank也都会有片选信号,这8个bank 的地址提供给nandflash ,norflash,sdram使用(下面sdram的接入我们会祥细讲解)

0x4000 0000 ----- 0x47FF FFFF : 其中的前4KB空间,也就是0x4000 0000 到 0x4000 1000 为片内SRAM地址空间,这就是所谓的steppingstone(下面s3c2440启动时会再讨论steppingstone的作用),其它的空间未使用.

0x4800 0000 ----- 0x5FFF FFFF : 特殊功能寄存器,CPU的寄存器都在这时定义和配置.

0x6000 0000 ----- 0xFFFF FFFF : 这大概3G的空间是没有使用的.

二.s3c2440接线规则:

图3

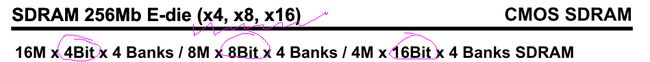

1) SDRAM接法规则,分三步(以K4S561632E为例):

1-1).需得到逻辑bank的选择IO:

图4-1

图4-2

Bank Size: 外接内存容量大小(K4S561632E是4M*16bit*4Bank*2Chips/8=64MB)

Bus Width: 总线宽度 (两片16位K4S561632E,并联成32位)

Base Component:单个芯片容量(bit)(256Mb)

Memory Configration:内存配置 ((4M*16*4banks)*2Chips )

根据K4S561632E的规格书(如图4-1,图4-2)得到一些信息.再结合图3 ,我们可以得到逻辑bank的选择I/O A[25:24]

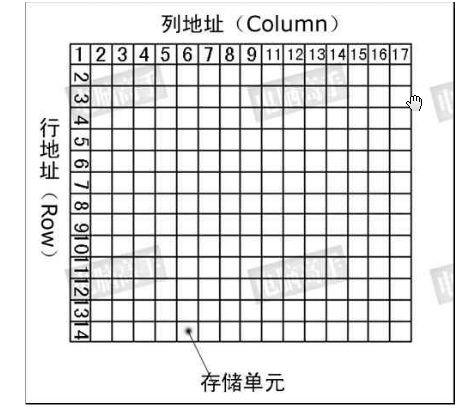

1-2).需要得到芯片的开始pin 号:

图5

我们选择了两片的K4S561632E sdram,所以是32位的.从A2 开始,

s3c2440的ADDR2 ------------- K4S561632E 的A0

s3c2440的ADDR3 ------------- K4S561632E 的A1

如此类推...

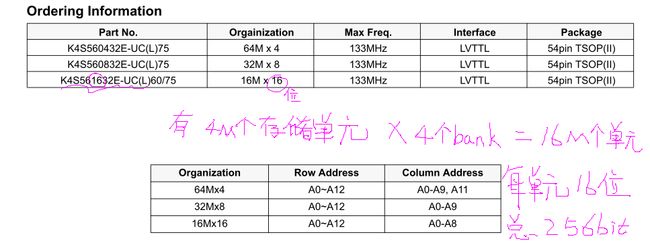

为什么要从ADD2开始了.我们知道SDRAM的寻址原理是一个存储阵列,如图6:

图6

每一片的K4S561632E 有4个逻辑bank,每个bank有4M个存储单元,每个存储单元有16位.这就是规格书所说的 4M*16bit*4Bank = 256Mbit.

而2片K4S561632E就有4M*4Bank*32bit = 512Mbit = 64MB,(市面上很少有32位宽的单片SDRAM,一般选择2片16位SDRAM扩展到32位宽)

内存寻址一次,就是行(ROW)列(Column)交叉一次,得到一个存储单元,也就是说内存是以"存储单元(本例为4个字节,低16位与高16位合成一个存储单元)"为单位的,而不是以"字节"为单位的.但是,cpu寻址是以字节为单位的.也就是说,cpu移动到下一个才一个字节,而本例内存移动到下一个就是4个字节.所以我们写程序时常常说要字节对齐就是这个原因.下面我举例子具体说明一下:

cpu 寻址内存 内存返回给cpu

0000 0000 第0个单元(其实包含0000 0000 至 0000 0011 这4个字节)

0000 0100 第1个单元(其实包含0000 0100 至 0000 0111 这4个字节)

0000 0101 第1个单元(其实包含0000 0100 至 0000 0111 这4个字节) 因为s3c2440没接A1和A0,所以相于逻辑与0xFFFF FF00,取到内存的4个字节后再用低两位去选择

0000 1100 第3个单元(其实包含0000 1100 至 0000 1111 这4个字节)

如此类推.....

cpu 的第2位对应了内存的第0位.也就是说cpu的4,而内存看成是1,他们的单位不同而已,一个是字节,一个是存储单位,也就是位宽.

同理,16位的位宽SDRAM的A0应该接到s3c2440的ADDR1上.

结论:SDRAM的A0接到s3c2440的那一个引脚上是根据整个SDRAM的位宽决定的.

1-3).开始连接SDRAM到s3c2440:

图7

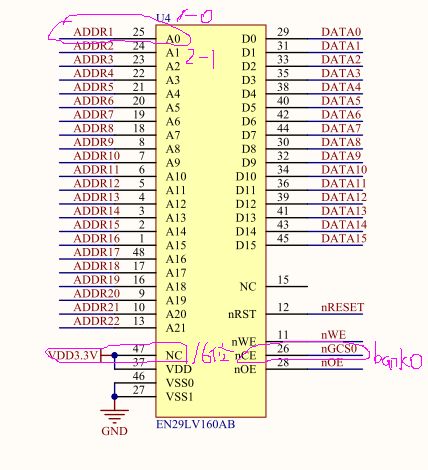

2) norflash接法规则,以EN29LV160A为例.

这个IC 位宽是通过引脚号为47的高低电平来选择BYTE/WORD,也就是有8位,16位两种模式.

图8

图9

规则大同小异,我这里就不多说了.

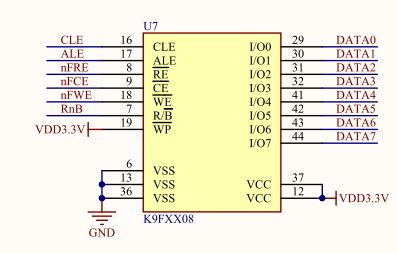

3.NANDFLASH接法规则,以K9FXX08为例:

三.s3c2440系统启动:

s3c2440支持两种启动模式:NAND和非NAND(这里是nor flash)。

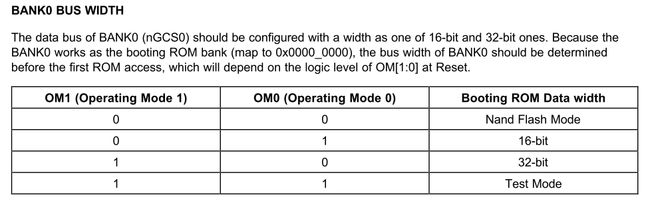

具体采用的方式取决于OM0、OM1两个引脚

OM[1:0所决定的启动方式

OM[1:0]=00时,处理器从NAND Flash启动

OM[1:0]=01时,处理器从16位宽度的ROM启动

OM[1:0]=10时,处理器从32位宽度的ROM启动。

OM[1:0]=11时,处理器从Test Mode启动。

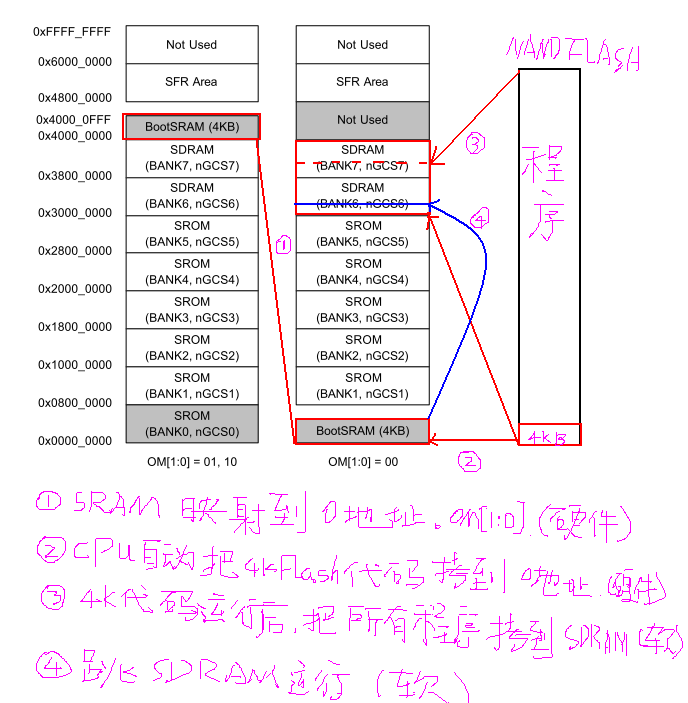

1当引脚OM0跟OM1有一个是高电平时,这时地址0会映射到外部nGCS0片选的空间,也就是Norflash,程序就会从Norflash中启动,arm直接取Norflash中的指令运行。

2当OM0跟OM1都为低电平,则0地址内部bootbuf(一段4k的SRAM)开始。系统上电,arm会自动把NANDflash中的前4K内容考到bootbuf(也就是0地址),然后从0地址运行。

Arm的启动都是从0地址开始,所不同的是地址的映射不一样。在arm开电的时候,要想让arm知道以某种方式(地址映射方式)运行,不可能通过你写的某段程序控制,因为这时候你的程序还没启动,这时候arm会通过引脚的电平来判断。

1) 从NorFlash启动时,与nGCS0相连的NorFlash就被映射到nGCS0片选的Bank0空间,其地址被映射为0x0000 0000;

2) 从NandFlash启动时,S3C2440芯片内部自带的一块容量为4K的被称为“Steppingstone”(起步石)的BootRAM被映射到nGCS0片选的Bank0空间,其地址被映射为0x0000 0000。当系统上电或复位时,程序会从0x0地址处开始执行,因此我们编写的启动代码要确保存储在0地址处。如果系统的所有程序在编译链接后的大小小于4K,那在系统的启动代码中无需考虑将程序从NandFlash搬运到SDRAM这个问题,因为所有的程序在启动时即全部由NandFlash拷贝至BootSRAM,程序在BootSRAM中运行即可;如果系统的所有程序在编译链接后的大小大于4K,那在系统的启动代码中就需要包含一段将系统的全部程序从NandFlash搬运到SDRAM的代码,因为系统启动时只将NandFlash的前4K拷贝到了BootSRAM中,还有部分程序在NandFlash中,而程序在NandFlash中是无法运行的,需要将所有程序拷贝至SDRAM并在其中运行,所以系统的启动代码中要包含这段有关程序拷贝的代码,并在所有程序拷贝完成后使程序跳转到SDRAM中运行。也就是说NandFlash启动时需要考虑到涉及的两次搬移,第一次搬运是S3C2440硬件机制自动实现的,无需干预,第二次搬运需要程序员来实现,搬运程序量大小是系统的所有程序。

NANDFLASH启动流程如图所示: