LPC177x/8x勘误手册

0.前言

初始版本:根据官方V3.3版本(2013.2.14)翻译而来,如有疑问,参考官方原版文件

更新1:根据官方V4.0版本(20140.6.03)翻译而来,如有疑问,参考官方原版文件

更新ETHERNE.1应急措施。

更新2:根据官方V4.1版本(2015.02.17)翻译而来,如有疑问,参考官方原版文件

纠正IBAT.1的简要描述,将VDDBAT改为VDDREG

只要我还使用LPC177x/8x,本勘误手册就会不断更新

(恳请各位路过的同仁推荐个编辑功能强大的博客平台,CSDN的这种图片插入方式,排版方式,以及对word的近乎零支持深感厌倦.)

1. CPU版本识别

LPC177x/8x系列CPU的上表面通常印有如下所示的标识:

LPC17xxXXX

xxxxxxx

xxYYWWR[x]

最后一行的最后一个字符(‘R’所在域)标识了CPU的版本号。注:量产前(前期的小批量试制)的部分芯片的标识跟正式生产的不同,并且这里所描述的版本识别方法也不适用于它们。本勘误是手册涉及LPC177x/8x的以下版本:

表1:CPU版本列表

| ’版本标识(R) |

版本描述 |

| ‘-’ |

初始版本 |

| ‘A’ |

第二版 |

| ‘E’ |

第三版 |

| ‘F’ |

第四版 |

‘YY’域表示制造CPU所在的年份,‘WW’域表示制造CPU所在当年的第几周。

2. 勘误概述

表2:功能问题列表

| 功能问题 |

简短描述 |

版本标识 [注1] |

详细描述 |

| ADC.1 |

外部同步输入信号不能操作ADC |

'-', 'A', 'E' |

见章节3.1 |

| ADC.2 |

在突发模式或者硬件触发模式时,不应该使用A/D全局数据寄存器 |

'-', 'A', 'E' |

见章节3.2 |

| APB.1 |

当APB总线的PCLK除数值设置成大于等于5时,访问APB外设 操作可能得到不正确的结果 |

'-', 'A', 'E', 'F' |

见章节3.3 |

| ETHERENT.1 |

使用以太网MII模式,在数据发送时,数据发送引脚TXD3:0和发送使能引脚TX_EN错误的参考了RX_CLK。 |

'-', 'A', 'E' |

见章节3.4 |

| I2C.1 |

为从机发送模式时,设置设备进入监听模式必须向DAT寄存器虚写一个0xFF。 |

'-', 'A', 'E', 'F' |

见章节3.5 |

| IAP.1 |

在120MHZ运行下,IAP功能可能失效,这个出现的概率约5% |

'-', 'A', 'E', 'F' |

|

| IBAT.1 |

仅使用VBAT供电时(VDDREG接地),IBAT电流会比正常情况下更高,这个出现的概率约5% |

'-', 'A', 'E', 'F' |

|

| ISP.1 |

ISP下载时,最大UART波特率限制到57600bps |

'-', 'A', 'E' |

见章节3.6 |

| PBOOST.1 |

当复位后就先执行用户代码时,功率提升控制位PBOOST[0:1]不能设置成‘11’。 |

'-', 'A', 'E' |

见章节3.7 |

| RTC.1 |

当RESET引脚存在复位信号时,RTC可能丢失时间 |

'-', 'A', 'E', 'F' |

见章节3.8 |

| USART.1 |

智能卡TX重试错误中断不能工作 |

'-', 'A', 'E' |

见章节3.9 |

| USART.2 |

终止中断“误报”事件可能会发生 |

'-', 'A', 'E' |

见章节3.10 |

| USB.1 |

USB主控制器遇到dribble位会暂停 |

'-', 'A', 'E' |

见章节3.11 |

| WDT.1 |

WDT超时不会将处理器从深度睡眠唤醒 |

'-', 'A', 'E' |

见章节3.12 |

注1:版本‘F’仅适用于LPC1774FBD

表3:AC/DC误差列表

| AC/DC误差 |

简短描述 |

版本标识 |

详细描述 |

| DPD.1 |

处于深度掉电模式时,随着时间的推移,泄露电流会增加 |

'-' |

见章节4.1 |

表4:勘误说明列表

| 勘误说明 |

简短描述 |

版本标识 [注1] |

详细描述 |

| Note.1 |

上电期间,出现在GPIO引脚上的意外脉冲(低电平)干扰会引起VDD供电增加 |

'-', 'A', 'E', 'F' |

见章节5.1 |

注1:版本‘F’仅适用于LPC1774FBD

3.功能问题详述

3.1 ADC.1:外部同步输入信号不能操作ADC

介绍:

软件控制模式下(BURST位为0),可以通过如下所示的ADC控制寄存器选项启动10位ADC转换:

表.: A/D控制寄存器位描述(AD0CR—地址0x4003 4000)

| 位 |

符号 |

描述 |

复位值 |

| 7:0 |

SEL |

从AD0[7:0]中选择采样和转换的输入脚。对于ADO,位0选择管脚AD0[0],位7选择管脚AD0[7]。在软件控制模式下,只有一位可被置位为1。在硬件扫描模式下,任何包含1-8的值都是可以被写进该位的。全零等效于0x01。 |

0x01 |

| 15:8 |

CLKDIV |

将APB时钟(PCLK)进行分频(CLKDIV值+1)得到A/D转换器的时钟。该 |

0 |

| 16 |

BURST |

1:A/D转换器以高达400kHz的速率重复执行转换,并且(如果必要)扫描SEL |

0 |

| 20:17 |

- |

保留。读取值未定义,只写入0 |

无 |

| 21 |

PDN |

1:A/D转换器处于正常工作模式。 |

0 |

| 23:22 |

- |

保留。读取值未定义,只写入0。 |

无 |

| 26:24 |

START |

当BURST=0时,这些位控制着A/D转换是否启动以及何时启动: 000 :不启动(当PDN清零时使用该值)。 |

0 |

| 27 |

EDGE |

该位只有在START字段为010-111时有效,在这种情况下: |

0 |

| 31:28 |

- |

保留。读取值未定义,只写入0。 |

无 |

问题描述:

ADC的外部启动转换特性中,如果AD0CR:START = 0x2或者0x3时,ADC可能不能可靠的工作,加在P2.10或P2.17引脚上的外部触发信号也会丢失掉。发生这个问题跟外设时钟(PCLK)有关。出现这个问题(GPIO上的ADC触发信号丢失)的概率如下所示:

· PCLK=100MHz,出现概率=12%

· PCLK=50MHz,出现概率=6%

· PCLK=12MHz,出现概率=1.5%

错误概率不受ADC启动转换边沿的频率影响。

应急措施:

使用软件控制模式时(BURST位为0),START位(位[26:24])设置成0x1或0x4或0x5或0x6或0x7时是可以使用的。用户也可以通过连接一个外部触发信号到捕获输入引脚(CAPx)来间接启动ADC转换:捕获定时器产生中断,在中断程序中设置START位为0x1.也可以通过定时器的匹配寄存器产生触发信号。(意思就是GPIO触发ADC转换只能看不能用,你们就当没有这个功能好了)

3.2 ADC.2:在突发模式或者硬件触发模式时,A/D全局数据寄存器可能不能使用

简介:

A/D控制寄存器的START域和BURST位指定是否通过软件命令启动A/D转换、是否响应某些硬件触发或者是否使用连续突发(硬件扫描)模式。ADC转换的结果可以通过两种方法的任一种读出:一种是A/D全局数据寄存器;另一种是使用各自的A/D通道数据寄存器。

问题描述:

如果突发模式使能(BURST位置一)或者指定了硬件触发,从A/D全局数据寄存器中读取的A/D转换结果可能是不正确的。如果A/D转换仅由软件命令(BURST位=‘0’并且START=‘001’)直接启动,则在新的转换启动前读A/D全局数据寄存器数据都是正确的。

应急措施:

当使用突发或者硬件触发模式时,使用各自的A/D通道数据寄存器来获取A/D转换结果,不要使用A/D全局数据寄存器。

3.3 APB.1 :当APB总线的PCLK除数值设置成大于等于5时,访问APB外设操作可能得到不正确的结果

描述:

外设时钟选择寄存器PCLKSEL控制用于所有APB外设的基础时钟。一个5bit的除数值位域用来设置要使用的频率范围。

问题描述:

在LPC177x/8x中,当外设时钟选择寄存器PCLK除数值设置成大于等于5时,访问APB外设可能得到不正确的结果。两个APB总线都有这样的问题。(NXP你NN个腿。)

应急措施:

PCLK除数值仅使用1,2,3,4。 。

3.4 ETHERNET.1:使用以太网MII模式,在数据发送时,数据发送引脚TXD3:0和发送使能引脚TX_EN错误的参考了RX_CLK

描述:

以太网模块包含一个全功能的10Mbps或100Mbps以太网MAC(媒体访问控制器),并且可以使用DMA硬件加速来获取最优性能。以太网模块接口使用MII(媒体独立接口)或RMII(精简的MII接口)协议以及片上的MIIM(媒体独立管理接口)串行总线与片外PHY通讯。

问题描述:

使用MII模式时,发送数据时,引脚TXD3:0和发送使能引脚TX_EN应该参考以太网PHY的TX_CLK。但是,芯片中存在一个配置错误,在数据发送时,数据发送引脚TXD3:0和发送使能引脚TX_EN错误的参考了RX_CLK。这个错误导致的结果是数据包的一小部分数据不能被PHY接收。

应急措施:

这将在下一版本中解决。(意思就是没改正之前,都不要使用MII接口了,已经用的,谁让你不看勘误手册。)

注:在RMII模式下,不会出现此问题。

3.5 I2C.1:为从发送模式时,设置设备进入监控模式必须向DAT寄存器虚写一个0xFF数据。

简介:

I2C的监控模式允许I2C模块监控I2C总线上的数据通信量,并且不会影响实际的I2C总线通信量。

问题描述:

在从发送模式下,设置设备进入监控模式必须向DAT寄存器虚写一个0xFF数据。如果不这样做,从从设备接收的数据可能被破坏。为了允许监控模式有充分的时间处理I2C总线上的数据,可能需要设备具有扩展I2C时钟的能力,根据这个条件,I2C监控模式并不能100%不影响总线。

应急措施:

当设置设备进入监控模式时,使能MMCTRL寄存器的ENA_SCL位,以允许扩展I2C时钟。

使能ENA_CLK位的软件代码举例:

1:LPC_I2C_MMCTRL |= (1<<1); /*使能ENA_SCL*/

在I2C ISR程序中,为了与从发送的状态码,写0xFF到DAT寄存器以预防数据失效。为了避免扩展SCL时钟,可以将数据字节保存到缓冲区中,在主循环中处理这些数据。这样可以确保SI标识尽可能快的被清除。

用于从发送模式的软件代码举例:

1: case 0xA8: // Own SLA + R has beenreceived, ACK returned

2: case0xB0:

3: case0xB8: // databyte in DAT transmitted, ACK received

4: case0xC0: //(last) data byte transmitted, NACK received

5: case0xC8: // lastdata byte in DAT transmitted, ACK received

6: DataByte = LPC_I2C->DATA_BUFFER;//Savedata. Data can be processed in Main loop

7: LPC_I2C->DAT = 0xFF; // Pretend to shift out 0xFF

8: LPC_I2C->CONCLR = 0x08; // clear flag SI

9: break;

3.6 IAP:在120MHZ运行下,IAP功能可能失效

简介:

复位后,BootLoader控制芯片的初始化操作,也提供编程Flash的功能。在应用编程(IAP)允许在用户代码的控制下擦除、编程片上Flash。当运行在120MHz时,用户应该设置电源升压控制寄存器(PBOOST)的BOOST[1:0]位为11并且矩阵仲裁寄存器(MATRIX_ARB)的ROM_LAT位1,以可靠地使用IAP编程。

问题描述:

在运行在120MHz时,即使BOOST位和ROM_LAT位正确置位,仍有大约5%的可能出现IAP调用失败。当出现调用失败,会使设备产生一个硬Fault。这个问题主要是因为对IAP调用以及Flash访问时序敏感造成的。

应急措施:

调用IAP时,运行速度低于120MHz。

3.7 IBAT.1:仅使用VBAT供电时,IBAT电流会比正常情况下更高

简介:

实时时钟(RTC)的供电可以由两个独立的电源提供:VDDREG和VBAT。两者中电压更高的为RTC供电,当VDDREG不再提供电源时,RTC可以通过外部电池由VBAT供电,此时供电电流典型值为1uA。

问题描述:

仅由VBAT供电时,电流可能会达到10uA,这种出现的概率约为5%。这是因为电源域电平位移而产生了漏电流。

应急措施:

出现问题的芯片进入深度睡眠模式后,漏电流能被消除。如果应用程序允许,在VDDREG电压跌落到零前,设计者应该让设备进入深度睡眠模式;BOD ISR可用于这个目的。

3.8 ISP.1:ISP下载时,最大UART波特率限制到57600bps

简介:

在系统编程(ISP)可以使用boot loader软件和UART0串行端口,编程或者重编程片上Flash存储器。这可以在终端用户板上完成Flash烧写。

问题描述:

ISP下载时,最大UART波特率不能超过57600bps

应急措施:

使用ISP时,确保UART的波特率为57600bps或者更低。(这...这也算是措施吗??)

3.9 PBOOST.1:当复位后立即执行用户代码时,升压控制位PBOOST[0:1]不能设置成‘11’

简介:

升压控制寄存器通过控制片内主稳压器的输出,允许用户使用高于100MHz(PBOOST[0:1]设置成11)高速高功耗操作,或者使用100MHz或更低频率(PBOOST[0:1]设置成00)的较低功耗操作。当复位后用户代码开始执行时,升压器默认启动(PBOOST[0:1]设置成11)。

问题描述:

日期标识码(印刷在CPU上表面的第三行字符)是wk1238(12年第38周生产)或者更早的某些产品,当复位后立即执行用户代码时,升压控制位PBOOST[0:1]不能设置成‘11’。这些产品用在100MHz以上时,可能不能有效的工作。

应急措施:

在用户代码中设置PBOOST[0:1]为11.

3.10 RTC.1:当RESET引脚存在复位信号时,RTC可能丢失时间

简介:

实时时钟(RTC)是一组用于测量时间的计数器,在系统掉电时也可以继续运行。RTC在掉电模式下消耗的功率极低。

问题描述:

在RESET引脚上的上升沿或者下降沿会使RTC暂时停顿并丢失一些时间。这个问题仅发生在LQFP封装中。当温度较低时,此问题会更加严重。减小复位脉冲的电压震荡且/或减少复位脉冲的上升下降时间可以减小时间计数损失。当这个问题发生,会影响RTC的预期精度,数千次复位可丢失1秒的时间。

应急措施:

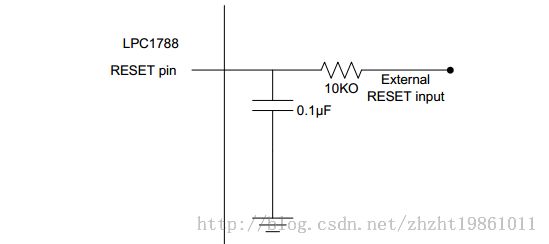

在复位引脚和外部复位信号电路之间增加RC滤波器,以控制复位信号电压的振荡速率。见图1所示。(注:CSDN怪异的图片插入方式,从Writer中复制的图片总是不给显示,吐槽了无数次,编写博客程序的程序员们就不考虑下细节吗)

图1:RTC.1应急措施

3.11 USART.1:智能卡TX重试错误中断不能工作

简介:

USART4包含一个同步模块和一个符合ISO7816-3的智能卡模式。这允许设计一个高安全性的智能卡应用。

问题描述:

USART4在重发失败(基于NACK)后会进入发送中断,但此时触发中断的错误源却没有写入IIR或者LSR寄存器。这样的错误发生在TX FIFO中有一个或多个项仍将发送时。当TX FIFO没有没有其它发送项,并且FIFO头项发送失败重传,此时中断可以正确工作并将8位错误源写入LSR寄存器。

应急措施:

一个应急措施是在智能卡模式下避免使用FIFO(FIFO重蹈A/D全局数据寄存器的覆辙,NXP门口抗议的增加到俩)。使用软件队列来解决。另一个应急措施在TX中断例程中检查所有的中断源,如果没有检查到中断源,就假定接收到一个NAK。

3.12 USART.2:“虚假的”终止中断事件可能会发生

简介:

LPC177x/8x系列微处理器的USART4具有一个可选的同步模式.

问题描述:

当在下列条件下使用的同步模式时:

· CSCEN =0 (SCK active only during transmission)

· CSRC = 0(Synchronous Slave Mode)

· FES = 1(Falling Edge Sampling)

· SSDIS =0 (Use Start and Stop Bit)

· 外部发送设备(主机) 发送起始和停止位

· 外部设备发送0x00

终止中断(BI)标志有效,尽管实际总线上并没有发生终止条件。当外部主机设备发送两个停止位时,该问题不会出现。

应急措施:

没有。(居然还说得理直气壮!!)

3.13 USB.1:USB主控制器遇到dribble位会暂停

简介:

全速/低速信令使用整帧位填充,没有例外的情况。如果接收的数据中有连续的7个1,则位填充错误发生,并且将这包数据忽略。

此处保留一段没看懂的。占位

问题描述:

如果在USB总线上遇到dribble位,USB主控制器从遇到第一个dribble位开始就会无限期暂停。并且在没有硬件复位的情况下,会一直维持这个暂停状态。这个问题不会影响从设备控制器。

应急措施:

没有。

3.14 WDT.1:WDT超时不会将处理器从深度睡眠唤醒

简介:

当程序进入错误状态而不能够喂狗时,一定时间后看门狗定时器溢出事件发生,如果使能了看门狗,则看门狗溢出事件会复位微控制器。

问题描述:

在正常运行和睡眠模式下看门狗超时事件可以生生,但是却不能将处理器从深度睡眠模式唤醒。

应急措施:

没有。

4. AC/DC误差详述

4.1 DPD.1: 处于深度掉电模式时,随着时间的推移,泄露电流会增加

因为这个问题只是出现在初始版本中,现在市场上的最差也是‘E’版本了吧,所以这个问题就不详细描述了。

5. 勘误说明详述

5.1 Note.1:在上电期间,一个未知的低电平干扰脉冲会引起IO端口引脚的Vdd供给增加

通用I/O(GPIO)引脚内部具有可配置的上拉/下拉电阻,默认设置下,引脚电平被上拉到Vdd.在上电期间,一个意想不到的低电平干扰脉冲会引起IO端口引脚的Vdd供给增加。