基于FPGA的图像处理(五)--状态机

使用FPGA实现各种算法时,状态机是很常用的方法,在SysGen中有两种非常简便的方法构建状态机,一是使用Mcode,以switch-case语句轻松实现,二是使用SysGen自带状态机模块。

状态机

假设我们要从01序列中检测出1011序列,则状态机模型如下

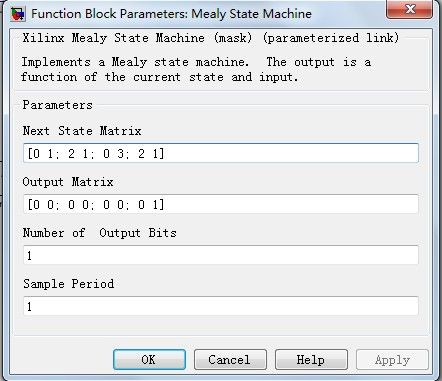

Next State Matrix:[0 1; 2 1; 0 3; 2 1]

Output Matrix : [0 0; 0 0; 0 0; 0 1]

一、使用Mcode实现

上一篇博客讲解了在Sysgen中Mcode的限制能力,这里直接使用

构建模型如下:

Singal From Workspace用于产生一个01序列,作为输入信号。

gatwayIn将数据类型转化为UFix_1_0

添加Mcode函数stateMcode.m

function [nextState, matched] = stateMcode(currentState, din)

% This is the update function for detecting a pattern of 1011

% This function represents a stateless and combination logic block.

% The output nextState should be to a register, and the output

% of the register should be fed back to the input currentState.

% Because the state register block has a feed back connection, in

% order to propagate the port prototypes automatically, the prototype

% of nextState should be determined only by constants or through

% an explicity xfix() call.

seen_none = 0; % initial state, if input is 1, switch to seen_1

seen_1 = 1; % first 1 has been seen, if input is 0, switch

% seen_10

seen_10 = 2; % 10 has been detected, if input is 1, switch to

% seen_1011

seen_101 = 3; % now 101 is detected, is input is 1, 1011 is

% detected and the FSM switches to seen_1

% the default value of matched is false

matched = false;

switch currentState

case seen_none

if din==1

nextState = seen_1;

else

nextState = seen_10;

end

case seen_1 % seen first 1

if din==1

nextState = seen_1;

else

nextState = seen_10;

end

case seen_10 % seen 10

if din==1

nextState = seen_101;

else

% no part of sequence seen, go to seen_none

nextState = seen_none;

end

case seen_101

if din==1

nextState = seen_1;

matched = true;

else

nextState = seen_10;

matched = false;

end

otherwise

% if nextState is not assigned outside the switch statement,

% an otherwise statment is required

nextState = seen_none;

end

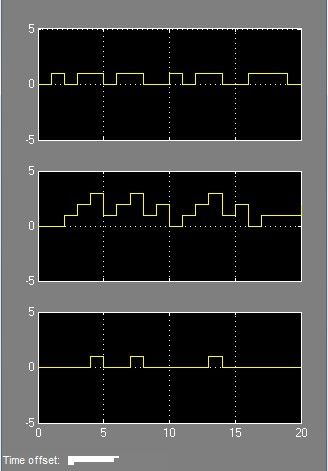

Scope效果如图:

二、使用Mealy State Machine模块实现

构建模型:

设置Mealy State Machine参数,就是状态机的参数

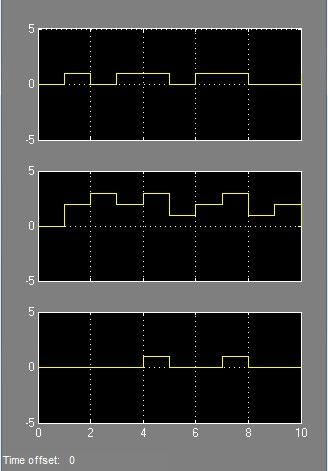

仿真结果如下:

在进行FPGA图像处理时,经常会用到状态机,这几天刚学习过,记录一下,其实使用Verilog直接实现也不是很难,只是会比SysGen稍微麻烦一些,修改起来也会花费更多的时间。

Model Based Design 在Xilinx 的工具中逐渐得到加强,相信以后会更加的方便。