s3c6410uboot源码分析之cup_init.S(一)

1、

#include <s3c6410.h>

.globl mem_ctrl_asm_init

mem_ctrl_asm_init:

ldr r0, =ELFIN_MEM_SYS_CFG@Memory sussystem address 0x7e00f120

mov r1, #0xd@ Xm0CSn2 = NFCON CS0, Xm0CSn3 = NFCON CS1

strr1, [r0]

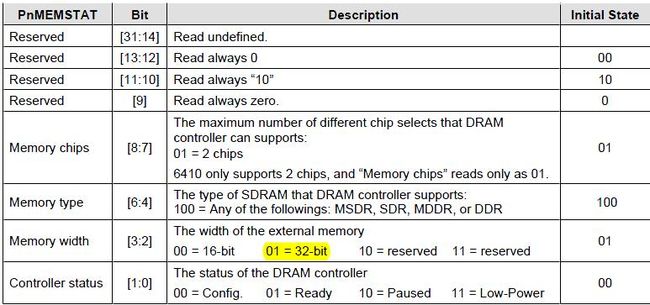

下图的黄色部分表明这出设置的作用,但我不明白,为何要设为0xd,要实现这个目标

@ Xm0CSn2 = NFCON CS0, Xm0CSn3 = NFCON CS1,好像与此处设计无关?

注:

• Memory port 0 is shared by using EBI (External Bus Interface).

• Memory port 1 is used only by DMC1.

• EBI module supports the share of pad interface used by 5 memory controllers (SROMC, two OneNANDCs,

CFCON, and NFCON).

SHARING CHIP SELECT FOR MEMORYPORT 0

The decision of which memory controller owns specific memory bank is decided both by following three

factors.

• Booting mode

• MP0_CS_CFG regsiter residing in System Controller

• XSELNAND input port value

2、

ldrr0, =ELFIN_DMC1_BASE@DMC1 base address 0x7e001000

只读寄存器。

3、

ldr r1, =0x04

str r1, [r0, #INDEX_DMC_MEMC_CMD]

#define INDEX_DMC_MEMC_CMD (0x04)

看到下面的图,应该知道为什么了吧?

配置为:Configure模式

4、

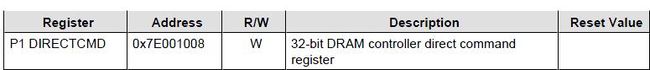

其中有两个寄存器没赋值,如下所示:

下面那个可能采用的是默认值。而上面的是只写寄存器,可能不需要赋值。

5、下面这些都是与具体的芯片相关的设置如刷新周期、CAS等待时间、T_DQSS等等。可以参考对应的芯片。

ldrr1, =DMC_DDR_REFRESH_PRD

str r1, [r0, #INDEX_DMC_REFRESH_PRD] 刷新周期寄存器

ldr r1, =DMC_DDR_CAS_LATENCY

str r1, [r0, #INDEX_DMC_CAS_LATENCY]

ldr r1, =DMC_DDR_t_DQSS

str r1, [r0, #INDEX_DMC_T_DQSS]

ldr r1, =DMC_DDR_t_MRD

str r1, [r0, #INDEX_DMC_T_MRD]

ldr r1, =DMC_DDR_t_RAS

str r1, [r0, #INDEX_DMC_T_RAS]

ldr r1, =DMC_DDR_t_RC

str r1, [r0, #INDEX_DMC_T_RC]

ldr r1, =DMC_DDR_t_RCD

ldr r2, =DMC_DDR_schedule_RCD

orr r1, r1, r2

str r1, [r0, #INDEX_DMC_T_RCD]

ldr r1, =DMC_DDR_t_RFC

ldr r2, =DMC_DDR_schedule_RFC

orr r1, r1, r2

str r1, [r0, #INDEX_DMC_T_RFC]

ldr r1, =DMC_DDR_t_RP

ldr r2, =DMC_DDR_schedule_RP

orr r1, r1, r2

str r1, [r0, #INDEX_DMC_T_RP]

ldr r1, =DMC_DDR_t_RRD

str r1, [r0, #INDEX_DMC_T_RRD]

ldr r1, =DMC_DDR_t_WR

str r1, [r0, #INDEX_DMC_T_WR]

ldr r1, =DMC_DDR_t_WTR

str r1, [r0, #INDEX_DMC_T_WTR]

ldr r1, =DMC_DDR_t_XP

str r1, [r0, #INDEX_DMC_T_XP]

ldr r1, =DMC_DDR_t_XSR

str r1, [r0, #INDEX_DMC_T_XSR]

ldr r1, =DMC_DDR_t_ESR

str r1, [r0, #INDEX_DMC_T_ESR]

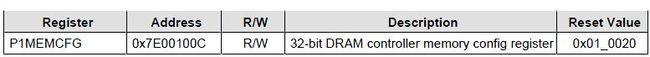

6、刚才说的有两个寄存器没赋值,现在出现了一个,

ldrr1, =DMC1_MEM_CFG

str r1, [r0, #INDEX_DMC_MEMORY_CFG]

#define DMC1_MEM_CFG0x0001001a

/* Supports one CKE control, Chip1, Burst4, Row/Column bit */

看注释应该明白个大概了,如下所示:

虽然没多少源码,可是内容还挺多,下一篇再接着说。