Cadence网络表总结

用Capture CIS画原理图后结果发现工程文件丢失。不知道是我误删除了还是由于Capture CIS的bug问题。但此时我已将网络表导入了Allegro,并摆放了一部分元件。如果重新画原理图重新布局PCB比较麻烦,于是就按照以前打印的PDF原理图布线。

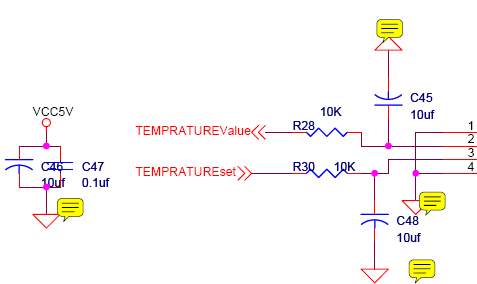

可是当布到最后却发现了问题,我想修改原理图的设计时却没有办法了。比如像下面这图里我想把接地引脚换成数字地(Dgnd),以前接的是模拟地(Agnd)

平时更改一下原理图就可以了,但原理图丢失,这时候就只能去修改cadence网络表来实现目标。

cadence网络表包括三个文件:pstchip.dat,pstxprt.dat,pstxnet.dat

打开之后就知道pstchip.dat是描述元件的引脚等信息的。pstxprt.dat是描述封装信息的,就是指该封装长什么样。pstxnet.dat就是描述各个元件之间的网络联系,即把所有的网络表和元件都给列了出来。

想将上面的元件地从Agnd改到Dgnd,需要将pstxnet.dat打开,在里面的

NET_NAME

'AGND'

'@ODDETECT.ODDETECT(SCH_1):AGND':

C_SIGNAL='@oddetect.oddetect(sch_1):agnd';

..................................

里找到对应的C46,C47,C45,C48的

NODE_NAME C47 2

'@ODDETECT.ODDETECT(SCH_1):INS229657@DISCRETE.CAP NP.NORMAL(CHIPS)':

'2':;

NODE_NAME C46 2

'@ODDETECT.ODDETECT(SCH_1):INS229641@DISCRETE.CAP.NORMAL(CHIPS)':

'2':;

NODE_NAME C48 2

'@ODDETECT.ODDETECT(SCH_1):INS546266@DISCRETE.CAP.NORMAL(CHIPS)':

'2':;

NODE_NAME C45 2

'@ODDETECT.ODDETECT(SCH_1):INS551150@DISCRETE.CAP.NORMAL(CHIPS)':

'2':;

剪切至

'DGND'

'@ODDETECT.ODDETECT(SCH_1):DGND':

C_SIGNAL='@oddetect.oddetect(sch_1):dgnd';

........................................

这时再重新导入网络表,就就会发现在PCB里已经更改过了电气的连接关系。

2

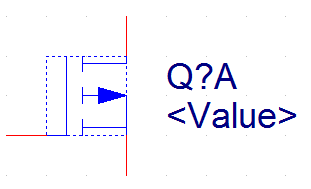

在画原理图封装时也遇到了问题,需要画的原理图是这样的:

我想画成这种形式

那么在Cadence中我分成了两部分。

对另外两个D一开始我是这样处理的:

为了在原理图时隐藏引脚我将第七号引脚变成了Power,认为这样就可以隐藏了(PART B部分一样的处理)。

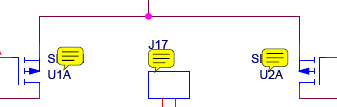

在画原理图的时候我需要这样接:

本来以为没有问题,结果在画PCB的时候发现问题了,在生成网络表的时候自动将U1的7,8号管脚和U2的7,8号管脚接在了一起(因为都是POWER属性)但实际原理图里U2和U1的D引脚是没有接在一起的。所以把属性改为POWER不可取。

后来我尝试了另外一种方案:

将第5号管脚D和第7号管脚D放在了一起,这样一来在原理图里也就不会看见多余的管脚了。这样一来在原理图连接时在源极连线其实一接就连了两个引脚:5和7(同理partB的6,8)

现在重新画原理图生成PCB或在原理图上修改后重新生成网络表就可以讲PCB中提示的将U1的7,8号管脚和U2的7,8号管脚接一起的提示去掉,但是我画的原理图丢失了,这样一来还是只能去修改网络表。

这时的修改会复杂一些。pstchip.dat是描述元件引脚信息的,这就需要首先修改。

修改该元件的描述:

在没修改的时候会将 PIN_NUMBER='(7,8)'定义为POWER,删除,修改为(这里是因为我又重新画了原理图,生成了网络表,在新的pstchip.dat中找到对该元件的描述后粘贴至老的pstchip.dat中):

pin

'G2':

PIN_NUMBER='(4,0)';

PINUSE='UNSPEC';

'D':

PIN_NUMBER='(5,6)';

PINUSE='UNSPEC';

'S2':

PIN_NUMBER='(3,0)';

PINUSE='UNSPEC';

'D1':

PIN_NUMBER='(7,8)';

PINUSE='UNSPEC';

'G1':

PIN_NUMBER='(0,2)';

PINUSE='UNSPEC';

'S1':

PIN_NUMBER='(0,1)';

PINUSE='UNSPEC';

end_pin;

修改过元件引脚描述后再来修改pstxnet.dat文件。

本来以为原来的pstxnet.dat文件中会将U1的7,8号管脚和U2的7,8号管脚接一起的情况定义成一个新的net,但后来发现没有这个net。表明这是软件默认连接的,并没有对应的net表。

原先是想把U1的7,8号管脚和5,6号管脚接起来,U2的7,8号管脚和5,6号管脚接起来.但在修改的时候发现不好添加,于是就没管它。这时再导入网络表后就会发现cadence不会提示说将U1的7,8号管脚和U2的7,8号管脚接一起了。

(但也没实现7,8号管脚和5,6号管脚接起来的目标,本来直接把新的pstxnet.dat文件中的连接关系复制到旧的pstxnet.dat中,但导入时发现了错误)原因如下如果想实现7,8号管脚和5,6号管脚接起来需要把7,8号管脚的INS号修改掉,在复制后两个pstxnet.dat对元件连接中的INS描述不同,相同的管脚也是如此[红色部分是软件给的标号]

旧的是

NODE_NAME U1 5

'@ODDETECT.ODDETECT(SCH_1):INS284662............................

新的是

NODE_NAME U1 5

'@ODDETECT.ODDETECT(SCH_1):INS172511@...........................

在新的pstxnet.dat中还多出来了对7,8号管脚的连接描述(在原理图中连线会使5和7引脚自动连在一起,这就会在pstxnet.dat文件里同一个NET_NAME里)

NODE_NAME U1 7

'@ODDETECT.ODDETECT(SCH_1):INS172511@......................................

'D1':;

NODE_NAME U1 8

'@ODDETECT.ODDETECT(SCH_1):INS172630@.......................................

'D1':;

目前不知道如何处理成对应的号。所以后来就对旧的pstxnet.dat文件没做修改。

其实做工程中出现了问题才好,只有出现了问题去解决它才能获得认识,一帆风顺往往学到的东西不多。如果不是因为原理图丢失我也不会去研究网络表文件。这也是收获,现在应该遇到问题了兴奋才对:终于又有问题出现了!