Ram简介

前言

因为ddr布线有点问题导致系统跑到1.6G的时,系统不稳定。遇到这种问题时,根据自己以往的经验一般都是先降低工作频率和稍稍提高DDR的工作电压,但是那小伙很是固执硬是让我改版pcb给他。为了走好DDR走线,了解DDR的工作原理和控制方式还是很有必要的。很久没有做硬件了,最近刚好一个朋友让我帮忙帮他捣鼓一个板子。他客户的板子,

RAM的分类

1) 静态RAM(Static RAM / SRAM),SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。2) 动态RAM(Dynamic RAM / DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

DRAM分为很多种,常见的主要有FPRAM / FastPage、EDORAM、SDRAM、DDR RAM、RDRAM、SGRAM以及WRAM等。 SDRAM(Synchronous Dynamic Random Access Memory):为同步动态随机存取内存。1996年底,SDRAM开始在系统中出现,不同于早期的技术,SDRAM是为了与中央处理器的计时同步化所设计,这使得内存控制器能够掌握准备所要求的数据所需的准确时钟周期,因此中央处理器从此不需要延后下一次的数据存取。举例而言,PC66 SDRAM以66MHz的速度运作;PC100 SDRAM以100MHz的速度运作;PC133 SDRAM以133MHz的速度运作,以此类推。所以SDRAM也可以称之为Single Data Rate(单倍数据传输率)RAM。

DDR SDRAM(Double Data Rate SDRAM):为双信道同步动态随机存取内存,是新一代的SDRAM技术。DDR内存芯片的数据预取宽度(Prefetch)为2 bit(SDRAM的两倍)。举例而言,使用DDR SDRAM时,一个100MHZ或 133MHz内存总线clock rate能够达到200MHz或266MHz的实际数据传输速率。

DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。DDR2内存Prefetch又再度提升至4 bit(DDR的两倍),即每次会存取4 bits为一组的数据,以两倍的频率输出至Data Bus以核心速度200MHz为例,数据传输速度DDR可达400MT/s,DDR2则可达800MT/s,数据存取效率倍增。

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。DDR3内存Prefetch提升至8 bit,即每次会存取8 bits为一组的数据。运算频率介于 800MHz -1600MHz之间。此外,DDR3 的规格要求将电压控制在1.5V,较 DDR2的1.8V更为省电。DDR3并新增 thermal sensor 的功能,为了要确保所存贮的数据不遗失,因此必须要定期 self-refresh ,不过为了节省电力,DDR3采用 ASR(Automatic self-refresh) 的设计,以确保在数据不遗失情况下,尽量减少更新频率来降低温度。

DDR2 SDRAM(Double Data Rate Two SDRAM):为双信道两次同步动态随机存取内存。DDR2内存Prefetch又再度提升至4 bit(DDR的两倍),即每次会存取4 bits为一组的数据,以两倍的频率输出至Data Bus以核心速度200MHz为例,数据传输速度DDR可达400MT/s,DDR2则可达800MT/s,数据存取效率倍增。

DDR3 SDRAM(Double Data Rate Three SDRAM):为双信道三次同步动态随机存取内存。DDR3内存Prefetch提升至8 bit,即每次会存取8 bits为一组的数据。运算频率介于 800MHz -1600MHz之间。此外,DDR3 的规格要求将电压控制在1.5V,较 DDR2的1.8V更为省电。DDR3并新增 thermal sensor 的功能,为了要确保所存贮的数据不遗失,因此必须要定期 self-refresh ,不过为了节省电力,DDR3采用 ASR(Automatic self-refresh) 的设计,以确保在数据不遗失情况下,尽量减少更新频率来降低温度。

物理Bank

传统内存系统为了保证CPU的正常工作,必须一次传输完CPU在一个传输周期内所需要的数据。而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。

当时控制内存与CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,而这个位宽就称之为物理Bank(Physical Bank,下文简称P-Bank)的位宽。所以,那时的内存必须要组织成P-Bank来与CPU打交道。

资格稍老的玩家应该还记得Pentium刚上市时,需要两条72pin的SIMM才能启动,因为一条72pin -SIMM只能提供32bit的位宽,不能满足Pentium的64bit数据总线的需要。直到168pin-SDRAM DIMM上市后,才可以使用一条内存开机。

要强调一点,P-Bank是SDRAM及以前传统内存家族的特有概念,在RDRAM中将以通道(Channel)取代,而对于像Intel E7500那样的并发式多通道DDR系统,传统的P-Bank概念也不适用。

芯片位宽

每个内存芯片也有自己的位宽,即每个传输周期能提供的数据量。理论上,完全可以做出一个位宽为64bit的芯片来满足P-Bank的需要,但这对技术的要求很高,在成本和实用性方面也都处于劣势。所以芯片的位宽一般都较小。

台式机市场所用的SDRAM芯片位宽最高也就是16bit,常见的则是8bit。这样,为了组成P-Bank所需的位宽,就需要多颗芯片并联工作。对于16bit芯片,需要4颗(4×16bit=64bit)。对于8bit芯片,则就需要8颗了。

逻辑Bank与芯片位宽

SDRAM的内部是一个存储阵列,因为如果是管道式存储(就如排队买票),就很难做到随机访问了。

阵列就如同表格一样,将数据“填”进去,你可以把它想象成一张表格。和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

对于内存,这个单元格可称为

存储单元

,那么这个表格(

存储阵列

)叫什么呢?它就是

逻辑Bank(Logical Bank,下文简称L-Bank)

。

由于技术、成本等原因,不可能只做一个全容量的L-Bank,而且最重要的是,由于SDRAM的工作原理限制,单一的L-Bank将会造成非常严重的寻址冲突,大幅降低内存效率。

所以人们在SDRAM内部分割成多个L-Bank,较早以前是两个,目前基本都是4个,这也是SDRAM规范中的最高L-Bank数量。到了RDRAM则最多达到了32个,在最新DDR-Ⅱ的标准中,L-Bank的数量也提高到了8个。

这样,在进行寻址时就要先确定是哪个L-Bank,然后再在这个选定的L-Bank中选择相应的行与列进行寻址。

可见对内存的访问,一次只能是一个L-Bank工作,而每次与北桥交换的数据就是L-Bank存储阵列中一个“存储单元”的容量。那么这个存储单元的容量就是芯片的位宽(也是L-Bank的位宽)

内存芯片的容量

存储单元数量 = 行数 × 列数(得到一个L-Bank的存储单元数量)× L-Bank的数量

SDRAM芯片的操作

1.寻址

1、首先,我们知道内存控制器要先确定一个P-Bank的芯片集合,然后才对这集合中的芯片进行寻址操作。因此要有一个片选的信号,它一次选择一个P-Bank的芯片集(根据位宽的不同,数量也不同)。被选中的芯片将同时接收或读取数据,所以要有一个片选信号。

2、接下来是对所有被选中的芯片进行

统一的L-Bank的寻址

,

目前SDRAM中L-Bank的数量最高为4个

,所以需要两个

L-Bank地址信号

(

2的2次方=4

)。

3、最后就是对被选中的芯片进行统一的

行/列(存储单元)寻址

。地址线数量要根据芯片的组织结构分别设计了。但在相同容量下,行数不变,只有列数会根据位宽的而变化,位宽越大,列数越少,因为所需的存储单元减少了。

4、找到了存储单元后,被选中的芯片就要进行统一的数据传输,那么肯定要有与位宽相同数量的数据I/O通道才行,所以肯定要有相应数量的

数据线引脚

。SDRAM的基本信号线如下图所示:

在介绍其他过程之前先认识一下SDRAM的内部结构:

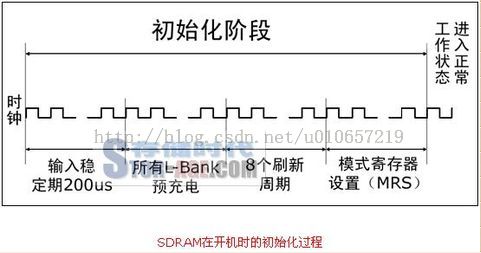

芯片初始化

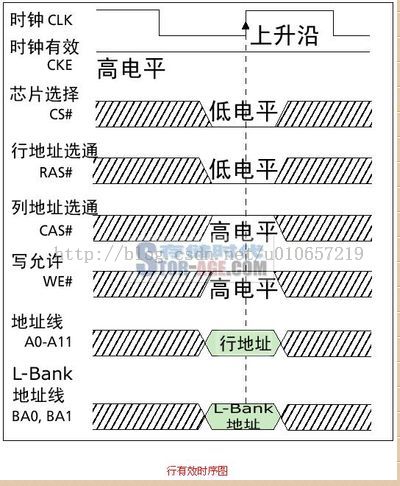

行有效时序图

初始化完成后,要想对一个L-Bank中的阵列进行寻址,首先就要确定行(Row),使之处于活动状态(Active),然后再确定列。虽然之前要进行片选和L-Bank的定址,但它们与行有效可以同时进行。

从图中可以看出,在CS#、L-Bank定址的同时,RAS(Row Address Strobe,行地址选通脉冲)也处于有效状态。此时An地址线则发送具体的行地址。如图中是A0-A11,共有12个地址线,由于是二进制表示法,所以共有4096个行(2的12次方=4096),A0-A11的不同数值就确定了具体的行地址。

由于行有效的同时也是相应L-Bank有效,所以

行有效也可称为L-Bank有效

。

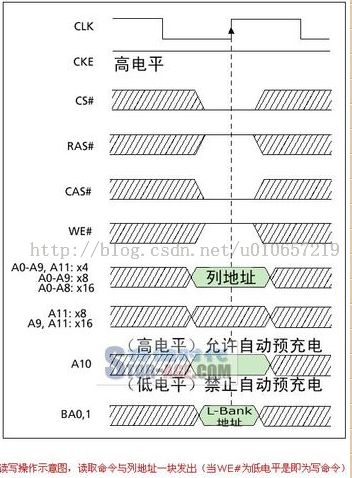

列读写

行地址确定之后,就要对列地址进行寻址了。但是,地址线仍然是行地址所用的A0-A11(本例)。没错,在SDRAM中,行地址与列地址线是共用的。

不过,读/写的命令是怎么发出的呢?其实没有一个信号是发送读或写的明确命令的,而是通过芯片的可写状态的控制来达到读/写的目的。显然WE#信号就是一个关键。

WE#无效时,当然就是读取命令

。

列寻址信号与读写命令是同时发出的。虽然地址线与行寻址共用,但CAS(Column Address Strobe,列地址选通脉冲)信号则可以区分开行与列寻址的不同,配合A0-A9,A11(本例)来确定具体的列地址。

数据输出(读)

在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据I/O通道(DQ)输出到内存总线上了。

但是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期)。

由于CL只在读取时出现,所以CL又被称为读取潜伏期(RL,Read Latency)。

CL的单位与tRCD一样,为时钟周期数,具体耗时由时钟频率决定。

数据输入(写)

数据写入的操作也是在tRCD之后进行,但此时没有了CL(记住,CL只出现在读取操作中),行寻址与列寻址的时序图和上文一样,只是在列寻址时,WE#为有效状态。

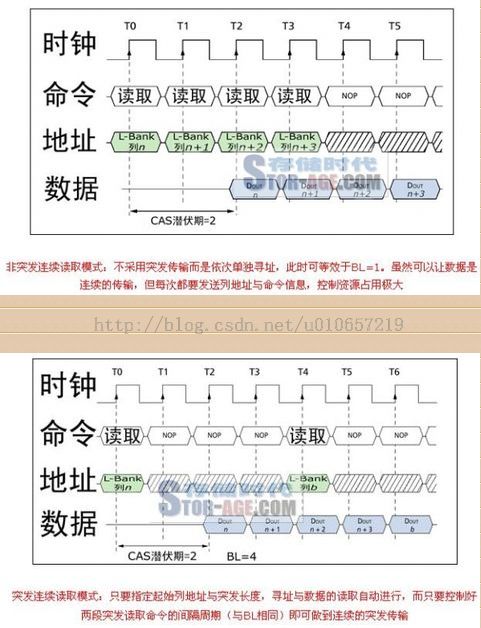

突发长度

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(Burst Lengths,简称BL)。

在目前,由于内存控制器一次读/写P-Bank位宽的数据,也就是8个字节,但是在现实中小于8个字节的数据很少见,所以一般都要经过多个周期进行数据的传输。

上文讲到的读/写操作,都是一次对一个存储单元进行寻址,

如果要连续读/写就还要对当前存储单元的下一个单元进行寻址

,也就是要不断的发送

列地址

与

读/写命令

(行地址不变,所以不用再对行寻址)。

虽然由于读/写延迟相同可以让数据的传输在I/O端是连续的,但它占用了大量的内存控制资源,

在数据进行连续传输时无法输入新的命令

,效率很低(早期的FPE/EDO内存就是以这种方式进行连续的数据传输)。

为此,人们开发了

突发传输技术

,只要指定

起始列地址

与

突发长度

,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。

这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是

tRCD+CL

)外,其后每个数据只需一个周期的即可获得。

在很多北桥芯片的介绍中都有类似于

X-1-1-1的字样,就是指这个意思,其中的X代表就代表第一笔数据所用的周期数

。

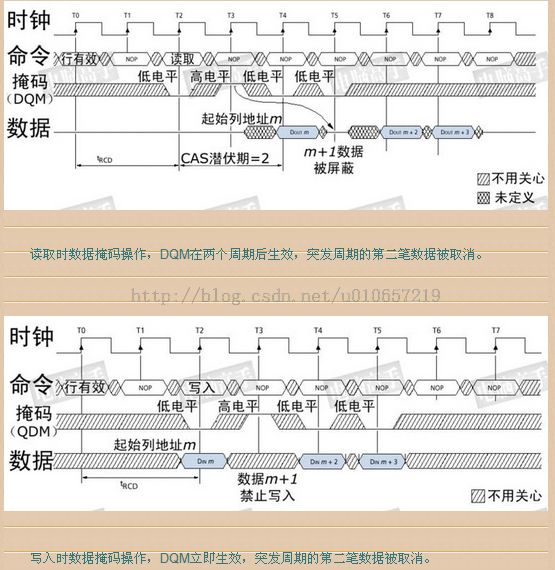

数据掩码

在讲述读/写操作时,我们谈到了突发长度。如果BL=4,那么也就是说一次就传送4×64bit的数据。但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?

为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术

。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,

在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽

。

DQM由北桥控制

,为了精确屏蔽一个P-Bank位宽中的每个字节,每个DIMM有8个DQM信号线,每个信号针对一个字节。这样,对于4bit位宽芯片,两个芯片共用一个DQM信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。

SDRAM官方规定,

在读取时DQM发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即成效

。

参考文章:http://blog.163.com/hanozi@126/blog/static/1865756200897105453/

http://www.virtium.com/resources/quick-reference-topics/ddr123/http://blog.csdn.net/njuitjf/article/details/18360741