MMU管理

ARM 架构处理器中的存储粒度(memory granularity)根据不同的应用方式,可有大页

(64K 字节)、小页(4K字节)和微小页(TinyPages, 1K 字节)和段(Sections,1M字节)。 常用的是 4K 字节小页面。至于大页和段则用于大数据领域,64K 字节的大页可以分成 4 个

16K 子页。

一、CP15 MMU 寄存器

ARM 的存储器管理通过系统控制协处理器 CP15 来实现。协处理器 CP15的各寄存器作用 如下。

1. R0:ID 寄存器(只读)

![]()

31 24 23 16 15 4 3 0 implementer 000000A Part number(BCD) revision

位[31:24]:实现者标记。ASCII 码,A:ARM 公司;D:Digital 公司 位[23:16]:体系架构版本号。‘A’=0,V3 版;‘A’=1,V4 版 位[15:4]:3 位 BCD 码的部分号

位[3:0]:版本号

2. R1: 控制寄存器(V3 版:只写;V4 版可读/写)

31 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

![]()

00000000000000000 RR V I Z F R S B L D P W C A M M(位 0):允许 MMU

A(位 1):允许定位故障检验

C(位 2):允许数据 Cache 或统一 Cache

W(位 3):允许写缓冲

P(位 4):从 26 至 32 位异常处理 D(位 5):从 26 至 32 位地址区域 L(位 6):至上一次中止时序 B(位 7):从小端到大端

S(位 8):修改 MMU 系统 R(位 9):ROM 保护状态

F(位 10):控制外协处理器通信速度 Z(位 11):允许分支预测

I(位 12):允许指令 Cache

V(位 13):异常向量基址从 0×00000000 至 0×ffff0000

RR(位 14):控制 Cache 置换算法(随机法和循环法) 位[31:15]作为保留位,如位[31:30]用作为 ARM920/ARM940 的时钟控制。

![]()

3. R2:地址变换表基址(V3 版,只写;V4 版,可读/写) 位[31:14]提供了 18 位地址变换表的基址,基定位界限为 16K 字节。

31 30 29 28 27 26 25 24 23 22 21 2019 1817 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2

1 0

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 该寄存器包含了 16 个域(domain),每个 2 位来说明访问权限 AP(Access Permission)。 其中,01:客户(client)使用域,根据段或页描述符的访问权限来检验;

11:管理员控制域的操作,无访问权限检验;

00:不允许访问,任何访问都会产生域故障;

10:保留。

5. R5:故障状态寄存器(V3 版,只读;V4 版,可读/写)

![]()

3

该寄存器用来指出故障类型和上一次数据存取中止时的域, D(位 9):设置数据断点

6. R6:故障地址寄存器(V3 版,只读;V4 版,可读/写) 该 32 位寄存器为上一次数据存取中止的地址。

7. R7:快存 Cache 操作(V3 版,只读;V4 版,可读/写)

该寄存器用来执行快存 Cache,写缓冲,预取缓冲和转移目标 Cache 清除以及排空

(flush)等操作。该寄存器值为零或相关的虚拟地址。

8. R8:变换后备缓冲器 TLB 操作(V4 版有效)

该寄存器用来执行变换后备缓冲器 TLB 的操作,单路或整个 TLB,由统一的或分离的指 令和数据 TLB 来支持。

9. R9:读缓冲操作

该寄存器用来控制读缓冲器。在一些处理器中,它用来控制 Cache 的锁住(lockdown) 功能。

10. R10:变换后备缓冲器 TLB 锁住 该寄存器用于控制 TLB 锁住功能。

![]()

11.R13:进程 ID 映像

| 31 |

25 24 |

0 |

| Process ID |

0000000000000000000000000 |

该寄存器通过进程 ID 寄存器来再映像虚拟存储器的虚拟地址。该机制是用来支持 Window CE,包括了快速文本处理与跟踪进程 ID。Intel 公司的 SA-1110 处理器及 ARM720T 与 ARM920T 处理器核都有此功能。若虚拟地址的位[31:25]为零,则用该寄存器的位[31:

25]来替代。

虚拟 Cache(Virtual Cache)是为了提高 Cache 效率,减少命中时间。由于虚拟存储 器,每次访问主存贮器都需把虚拟地址变成物理地址。若 Cache 使用虚拟地址(传统用的是 物理地址)访问,那么,可通过虚拟 Cache 的命中来减少地址转换时间。

但是,当进程切换时,由于新进程的虚拟地址(有可能与原进程的相同),所指向物理 空间与原进程不同,就需要排空 Cache,这种排空会影响 Cache 失效率。因此,在地址标志 中增加了进程标识符字段 ProcessID(PID),这样多个进程的数据可以混放在一个 Cache 中, 由 PID 指出Cache 中各行的数据是属于哪个程序的。为了减少 PID 位数,PID 通常是由操作 系统指定的。

不过,虚拟 Cache 会引起同义(Synonym)问题。由于操作系统和用户程序对于同一物 理地址可能会有两个以上的虚拟地址来访问,这些地址称为同义或别名(alias)。它们可能 会导致同一数据在虚拟 Cache 中存在两个副本。若其中一个被修改,那么使用另一个数据就 会产生错误。这种情况在常规(物理)Cache 是不会发生的,因为这些访问首先会把虚拟地 址转换到同一物理地址,从而找到同一物理 Cache 行。虚拟 Cache 通过反别名法

(Anti-aliasing)的硬件来解决该问题,它保证每一 Cache 行对应于唯一的物理地址。

12. R14:调试支持 该寄存器用来调试支持

13. R15:测试和时钟控制 该寄存器用于测试,以及部分处理器的时钟控制。

CP15 的 MMU 寄存器中 R4、R11 和 R12 保留。

二、第一级描述符

存储器管理的段/页寻址中的段表/页表都放在存储器中。表的基址、域、访问权限以及 有关特性都放在第一级描述符中。第一级描述符也放在存储器中,该变换表由 CP15 协处理 器的寄存器给出,而表格索引则由虚拟地址[31:20]给出,如图 2-28

virtual address

CP15

re giste r 2

31 20 19 0

table index

31 14 1 3 0

tra nslation table ba se address

31 14 1 3 2 1 0

me mory acce ss

tra nslation table ba se address

ta ble index 0 0

31 20 19 12 11 10 9 8 5 4 3 2 1 0

coarse pa ge table base address

0 domain 1 0 0 0 1

section base address

0 0 0 0 0 0 0 0

AP 0 domain

1 C B 1 0

fine page ta ble ba se a ddre ss

0 0 0

doma in

1 0 0 1 1

图 2-28 第一级描述符

第一级描述符按位[1:0]可以有 4 种情况:

00:无效

01:粗调页的描述符

10:段的描述符

11:细调页的描述符(支持某些 ARM 处理器核)

三、段式寻址

如图2-29 所示,32位虚拟地址(即逻辑地址)分成高 12 位段表项索引(tableindex) 和 20 位段索引(Section index)。12 位段表索引与 CP15 的 R2 中的 18 位变换表基址

(translation table base address)合并成存储器存取地址(最后 2位为 00)。查段表找 出相应的段描述符,位[31:20]为段基址(section bass address),位[19:12]为零,位 [11:10]为 AP 存储器存取权限,位[9]为 0,位[8:5]为域,位[4]不确定,位[3]为 C:Cache 允许,位[2]为 B:缓冲器允许,最低 2 位为10 表示段描述符。然后,段基址与段索引(32 位虚拟地址中提供)合并成真正的存储器存取地址(物理地址),读出相应的数据。

virtual

31 20 19 0

address

table index

section index

CP15 register 2

31 14 13 0

translation table base address

31 14 13 2 1 0

memory access

translation table base address

table index 0 0

31 20 19 12 11 10 9 8 5 4 3 2 1 0

section base address

0 0 0 0 0 0 0 0

AP 0 domain

? C B 1 0

31 20 19 0

memory access

section base address

section index

31 0

data

图 2-29 段式寻址示意图

四、二级页式寻址

图2-30是二级页式寻址示意图。32 位虚拟地址分成为位[31:20]:12 位为第一级表索 引(有的称目录项索引),位[19:12]:8 位页表索引(page table index),位[11:0]:

12 位页偏移值(page offset)。12 位第一级表索引与 CP15 的R2 中的 18 位变换表基址合并 成存储器存取地址(最后 2 位为00)。查第一级表,取出相应第一级描述符,位[31:10]为 页表的基址(page table base address),位[8:5]为域,最后 2 位为 01 表示第二级粗调 页表指针(10 为段指针,11 为第二级细调指针)。22 位的页表基址与页表索引(32 位虚拟 地址提供)再次形成存储取地址(最后 2 位为 00),查第二级表(页表),找出相应表描述 符,位[31:12]为该页基址,AP3、AP2、AP1、AP0为 4 个子页(16K 字节)的存取权限,描 述符中 C 和B 定义同段描述符中的 C和 B 定义,后 2 位10 表示为小页(01 为大页,11 为微 小页,00 变换故障),20 位页基址与页偏移值(32 位虚拟地址提供)形成真正存储器存取 地址(物理地址),读出相应数据。

virtual address

31 20 19 12 11 0

first level table index

page table index

page offset

CP15 register 2

31 1413 0

translation table base address

31 1413 2 1 0

translation table base address

table index 0 0

31 10 9 8 5 4 2 1 0

memory access

page table base address 0 domain

??? 0 1

31 10 9 2 1 0

page table base address

page table index 0 0

31 12 11 10 9 8 7 6 5 4 3 2 1 0

memory access

page base address

AP3 AP2 AP1 AP0 C B 1 0

31 12 11 0

page base address

page offset

31 0

data

Memory amcess

图 2-30 二级页式寻址示意图

五、存取权限

每个段和子页的存取权限 AP 位与域信息一起用于第一级描述符中,域控制信息在 CP15 的 R3 寄存器中,CP15 的R1 寄存器中的 S 和R 位与处理器的用户/管理者状态来决定是否允 许对所寻址单元进行读/写。允许检验过程如下:

1.若CP15 的R1 中位[1]置“1”,允许定位检验;则检验地址定位,以及若定位失效(如 字没定位于 4 字节界限,半字没定位于 2 字节界限),则产生故障。

2.认证第一级描述符中的寻址单元域位[8:5](该描述符无效,取第一级描述符出错故 障)。

3.检验CP15 中的R3域存取控制寄存器,当前处理是用户(Client)?还是管理者?若 二者都不是,则出错。

4.若该域是管理者,则省去存取权限处理;若是用户,则按表 2-5检验其存取权限。如 果存取没被允许,则出错,否则继续存取数据。

表 2-5 存取权限

| AP |

S |

R |

管理者 |

用户 |

| 00 |

0 |

0 |

无存取 |

无存取 |

| 00 |

1 |

0 |

只读 |

无存取 |

| 00 |

0 |

1 |

只读 |

只读 |

| 00 |

1 |

1 |

没用 |

|

| 01 |

- |

- |

读/写 |

无存取 |

| 10 |

- |

- |

读/写 |

只读 |

| 11 |

- |

- |

读/写 |

读/写 |

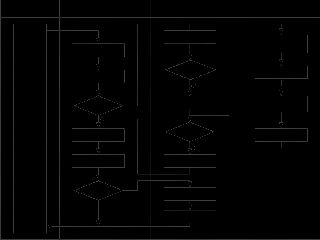

相应的流程图如图 2-31 所示,图中 PTE(Pag Table Entry)为页表项。

virtual address

alignment fault

section translation fault

get level 1 descriptor

section

page

page translation fault

section domain fault

check domain status

page domain fault

section permission fault

client

manager

client

subpage permission fault

physical address

图 2-31 访问权限检验过程

数据访问故障所产生的故障状态寄存器(CP15 中的R5)和故障地址寄存器(CP15 中的 R6)将不断更新,提供出错的原因和故障单元。在指令执行时,指令访问的故障将只产生一 个异常,它并不更新故障状态及地址寄存器。故障地址可以从链寄存器的返回地址来推演。

若产生缓冲写的外部故障,由于此时处理器已执行了若干条指令,故不能恢复该故障的 状态,在一般的 ARM 架构的应用中,不会有这样潜在现象出现,故也不作这方面考虑。

段描述符和第二级页描述符中的C和B位用来控制段或页中数据是否可以复制至Cache

以及通过写缓冲写回主存储器。

六、虚拟 Cache

一般的 Cache 采用物理地址(实地址),即 Cache 的标志(tag)是物理地址的高位部分, 访问 Cache 块的地址索引也是物理地址。故需先访问地址变换后备缓冲器 TLB,得到物理 地址后再访问 Cache,如图 2-32 所示。

虚页号 页内偏移量

来自处理机的虚地址

TLB项

虚页号 有效位 实页号

Cache

虚页号 有效位 实页号

比较 比较

多路选择器

TLB命中

Cache命中 字

实地址

TAG 块 字 字节 实页号 页内偏移量

图 2-32 物理地址 Cache 与 TLB

虚拟地址由处理器给出,并由 TLB 变换为物理地址。若 TLB 命中,则由物理地址访问 Cache;若 TLB 未命中,则查段表或页表找出相应的物理地址,并修改 TLB;如果在段表或 页表中仍找不到,则不得不去访问后备存储器,找出相应的物理地址,并修改页表或段表。

TLB 命中后,取得物理地址来访问 Cache。若 Cache 命中,则可快速访问;若 Cache

未命中,则只能直接访问存储。 上述的工作过程如图 2-33 所示:

处理机 Cache 主存 后备存储器

地址

虚地址

查页目录

从后备存储器 读页表

查TLB

页表 N 命中?

Y

修改页目录

TLB N 命中?

Y

查页表

N

从后备存储器 读页

产生实地址

Cache

命中?

Y

修改页

查Cache

修改TLB

Cache N 命中?

读存储器

Y

修改Cache

数据

图 2-33 物理地址 Cache 的工作流程

上述的过程,需先把虚拟地址变换成物理地址,然后才能访问 Cache。这样要增加一个 查 TLB 的时间,必然会增加访问 Cache 所花费时间。因此,在 ARM 架构中,有许多处理 机采取直接用虚拟地址访问 Cache,即采用虚拟 Cache(Virtual Cache)方式。

虚拟 Cache 中,处理机所给出的虚拟地址,既作为 TLB 的虚拟地址转换成物理地址变 换的虚拟地址,也直接 Cache 访问的地址。这样 Cache 的访问可以省去了 TLB 的变换,可 以提高执行的速度;若 Cache 访问未命中,那么,仍需象物理 Cache 那样,进行 TLB 变换

(访问快表),以及段/页访问(访问慢表)找出相应的物理地址。图 2-34 给出了虚拟 Cache

的示意图。

虚页号 页内偏移量

TAG 块 字 字节

来自处理机的虚地址

TLB项

虚页号 有效位 实页号

Cache

虚页号 有效位 实页号

比较 比较

多路选择器

TLB命中

Cache命中 字

实地址

实页号 页内偏移量

图 2-34 虚拟 Cache 示意图

但是,当进程切换时,由于新进程的虚拟地址(有可能与原进程的相同),所指向物理 空间与原进程不同,就需要排空 Cache,这种排空会影响 Cache 失效率。因此,在地址标志 中增加了进程标识符字段 ProcessID(PID),这样多个进程的数据可以混放在一个 Cache 中, 由 PID 指出Cache 中各行的数据是属于哪个程序的。为了减少 PID 位数,PID 通常是由操作 系统指定的。

不过,虚拟 Cache 会引起同义(Synonym)问题。由于操作系统和用户程序对于同一物 理地址可能会有两个以上的虚拟地址来访问,这些地址称为同义或别名(alias)。它们可能 会导致同一数据在虚拟 Cache 中存在两个副本。若其中一个被修改,那么使用另一个数据就 会产生错误。这种情况在常规(物理)Cache 是不会发生的,因为这些访问首先会把虚拟地 址转换到同一物理地址,从而找到同一物理 Cache 行。虚拟 Cache 通过反别名法

(Anti-aliasing)的硬件来解决该问题,它保证每一 Cache 行对应于唯一的物理地址。