MSI (Message Signaled Interrupts)

MSI (Message Signaled Interrupts)

1. Introduction

之前有提到因功能需求的增加,越来越多的PCI/PCIE设备被加入进来,导致中断资源的缺失。后来就出现了IRQ Routing以及MSI等技术手段用于解决这些问题。看上去MSI较通常使用Interrupt Pin的方式比较起来似乎有优势,MSI是通过向Host发MSG的方式产生IRQ request,再送达Host/PCI Bridge之前它和普通的Memory Write并没有什么区别,Host收到以后再将该Memory Write转化成Interrupt送抵各个CPU,传统使用Interrupt Pin的方式通常需要专门的Interrupt Trace而且还要和其它的PCI device分享PIC/APIC Interrupt Controller等。当然MSI也不是没有缺点,它有一个比较严重的问题就是没法保证Interrupt Latency,因为它的产生方式和Memory Write一样,所以MSG可能会被Host/Loading Cache这样就可能会出现Latency,另外当Loading重的时候也可能会出现比较大的Latency。

2. How to Use

1. MSI New Capabilities Type

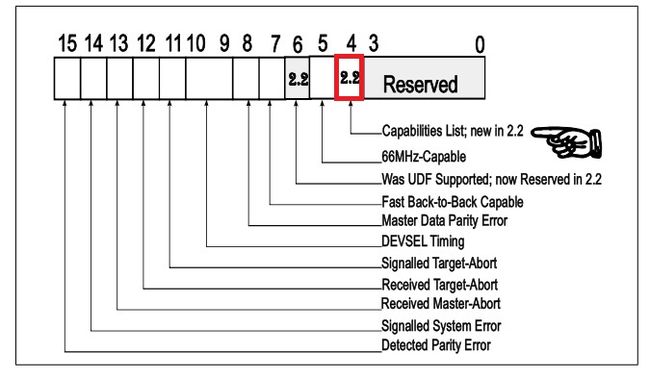

并不是每个PCI Function都支持MSI,只有支持Capability Type 05的 PCI Function才可以支持MSI,那么何谓Capabilities呢?它是PCI 2.2新加入的一个特性,之所以加入 是因为当初规定所有PCI SPEC相关的配置寄存器都要放在最前面的16dwords 范围内的Configuration Header Space,可是到PCI2.2以后 发现新加入的register 在Configuration Header Space空间放不下了,然后才搞出来这样一个New Capabilities List而且允许该功能能够扩展到64dwords的范围内。确认一个PCI Function是否支持Capability Type 05,首先要先看它是否支持Capability,可以通过检查PCI Status Register Bit4如下图1所示:

图1

如果该Bit是1,接下来需要Check Capabilities Pointer(0x34),使用该Pointer的值继续索引出整个Capabilities Lists,下图2是一个支持MSI Capability的PCI device,如绿色连线所示通过New Capabilities List Entry中的Pointer to Next Capability以及Capability ID我们就可以遍历整个Capabilities Lists并找出MSI Capability。

图2

New Capabilities List Entry Register的格式如下图3所示:

图3

2. MSI Register Format & MSI Trigger Mechanism

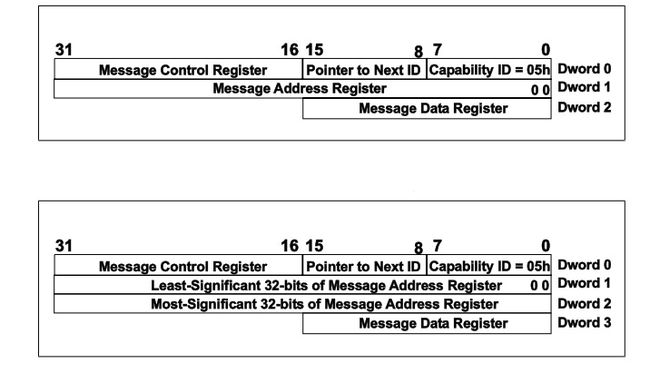

MSI Register 存在于MSI Capability Entry中,它的格式有两种如下图4所示,其中使用64位地址格式的register是为PCI64Bit Extension以及native PCI Express devices使用的。

图4

其中Message Control Register用于控制MSI Enable/Disable 以及可以产生的MSG的数量等。Message Address Register是分配成PCI device的一个地址,一旦有MSI需要产生Device要将相应的MSG ID写入到该地址中。Message Data Register是用于提供Base Message Data Pattern的register。

如果Message Address Register = 0A000000h ; Message Data Register = 0500h;我们向0A000000h 写一个0501的值 就会产生一个ID为01的MSI。

另外关于配置PCI Device MSI Function的部分,我在SBIOS中并没有找到相关去配置以及产生MSI的code,可能关于MSI部分的Function是由 Driver去做的。

Refer:

《PCI System Architecture》

Peter

2010-11-02