DDR2 仿真说明

本文大部分是基于 DDR2 Spec 的理解并进行解释,包括很多时序图,因而

很多细节问题需要参考 DDR2 spec。DDR2 的 spec 在目前最新版本是 jesd79-2c

可在 www.jedec.org/download/search/JESD79-2C.pdf 下载到,做仿真仿真,我觉得首

先要把仿真时序部分先弄清楚,那么仿真的事情已经完成一半。讨论几个概念

仿真工具的使用

Cadence pcb si: 板级仿真软件,时序计算比较方便

Synopsys Hspice: 晶体管级仿真软件,差分线仿真感觉精确度比 pcb si 好点

Ansoft HFSS: 三维电磁场仿真软件,提取过孔模型等

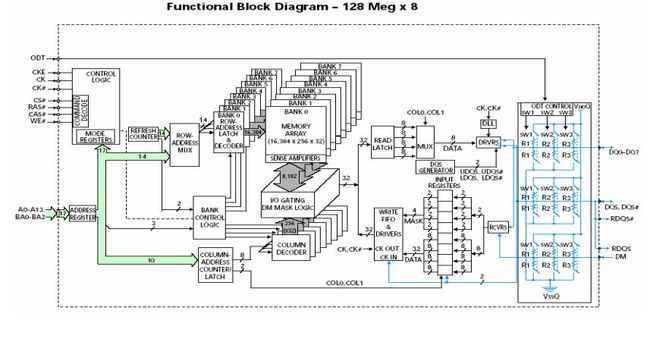

DDR2 工作方框图

在子卡定义的时候经常有 single rank 以及 dual rank 的区分,从仿真角度来看,

如果一个数据线带 2 个 SDRAM,那么认为是 double rank

不妨来看下 DDR2 sodimm 的 Raw card A 定义,它是 dual rank,原因在于,Raw

card A 采用的 SDRAM 是 X16,而且 Raw card A 上面有 8 个 SDRAM,而 sodimm

的架构是 X64,因而每根数据线连到 16X8/64=2 SDRAM

仿真频率(Switching frequency)的选择

通常大家对于仿真频率选择有点迷糊,特别是 DDR2 产品,比如说定义 DDR2

的数据传输为 667 MT/s,那么 Clock/data/cmd/ctl 的仿真频率如何选择,不妨看

下面的时序图

考虑 Clock 时钟,他一个周期比如说 T0 它包含 2 个 bit01 信息,对于 DDR2 667

来说 bit 数据流 667Mbit/s,实际仿真的频率为 333MHz

考虑 Address/CMD,在此是 1T,通过时序图可以看到,它是 clock 时钟的一半,

仿真的频率为 167MHz,因而可以得到下面的仿真频率 Clock 333MHz、Data

333MHz、Control 167MHz、Address/Cmd 167MHz(1T) 83(2T)。同理对于 pcie 类

似的 2.5Gbit/s,他们仿真频率为 1.25GHz

仿真 DDR2 的类型

通常在主板设计中可能用到如下的 DDR2 类型:直接在板上用 SDRAM 芯片;

使用 dimm(DIMM 大部分用在台式机上面);使用 sodimm(sodimm 大部分用在

笔记本电脑等上面)。实际上 DIMM/SODIMM 只是种规格,相当于插卡,插卡

板上采用 DRAM 芯片,对于仿真来说,它们只不过是多板仿真,接口不同而已。以下几点特别提出来,因为在仿真的时候,有可能碰到,虽然大同小异

a. 带 ECC 功能的 DDR2 以及不带 ECC 功能的 DDR2,相当于多出来一组数据线,

不过他不是用来传输数据,而是用来检测数据的有效性

b. 带 Register 功能的 DDR2 以及不带 Register 功能的 DDR2,由于 ADDR 带的

负载比较重,所以在插卡上加个 register(buffer)来重新驱动 addr,因而计算公式

有些差异,但是仿真方法思路一致,在此不对于其进行赘述

具体大家可以去 www.micron.com 查询,还有可去下载 JEDEC 给出 board file,

大家可以进行对比。

ODT(on die termination)的概念

大家如果用过 DDR 会记得板上数据线后经常有个尾巴(56Ohm 上拉到电源

2.5V),在 DDR2 把这个尾巴集成到 SDRAM 中所谓 ODT 并提供几种终端方式

(比如可以在寄存器设置开启 150/75/50 Ohm 等等)

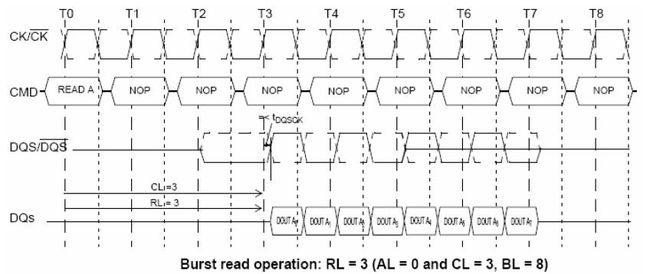

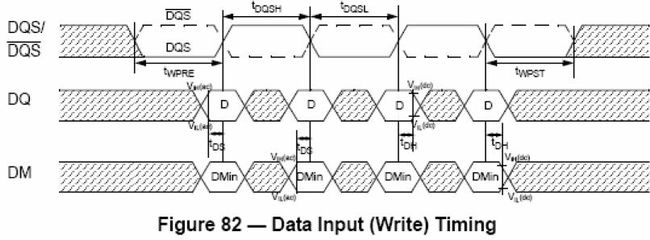

时序图的概念

在 DDR2 中有 2 时序,读时序以及写时序,他们的时序图如下图所示

这儿列出的是 Memory 的时序,实际上 Memory controller 也有此类似的时序。由

于定义的不同,在这会产生两种不同的时序计算方法,一个以有效窗口概念来计

算,一个以具体的 setup time 以及 hold time 来计算。

有效窗口概念:发送端产生的 skew+Interconnect 产生的 skew《接受端能容许的

skew(Freescale 芯片 MPC 系列经常是这么定义的)

setup time 以及 holde time 概念:发送端的有效 setup time》nterconnect 产生的 skew

+接受端需要的 setup time 以及发送端的有效 hold time》nterconnect 产生的 skew

+接受端需要的 hold time(Intel 芯片系列经常是这么定义的)

下述以前仿真的步骤来列出时序计算中必须考虑这几个事情

a 叠层结构的设计(涉及全局,包括 pi/emc 问题等,其计算说明已经贴出,在以

后版本会讨论如何设计);b 走线拓扑的选择;c 串扰的考虑;d 时序计算;e 制

订 design guide(规则)

考虑前 3 步骤是为 4 服务的,用来计算它对于时序的影响,第 4 步是用来计算最

终时序并推出第 5 步给 layout 规则

叠层结构的设计

通常坏的叠层会产生所谓阻抗不连续性,例如反射问题,串扰问题,EMI 问题,

PI 问题,因而在设计中应遵循如下原则:a 对称性;b 高速信号走线具有完整参

考平面,电源平面与地平面的耦合。

设计方法可以考虑如下

输入:总层数,走线层数,总厚度,阻抗要求

输出:叠层结构,单端信号的走线宽度与差分信号走线宽度以及间距

由于叠层结构设计和厂家制程能力息息相关,在设计的时候一定要和厂家协商。

下面列出在正常单端阻抗 55Ohm 范围变化下所带来的 skew

如上图所示,阻抗越高,Slew rate 越快,幅度越大,但是 aperture 越小, jitter 越

大,当在阻抗范围内变化时,有 5ps 的 skew 产生

拓扑结构的类型

目前的拓扑结构通常有:点到点(基本上目前高速信号所用的拓扑结构);多点

(菊花链型,树型,星型等等,多用于低速多负载)

在 DDR2 仿真中,如果采用插卡方式,拓扑结构可选择余地不多,通常需要做

的事情如下:确定驱动能力;确定 ODT 开启选项(和波形/时序设计相关)

通过调整驱动能力和开启 ODT 选项,产生如下波形

如上图所示,ODT 阻抗越高,Slew rate 越快,幅度越大,但是 aperture 越小, jitter

越大,在此做个平衡,选择 1.75XODT150(选择强驱动通常是带 2 个负载等)

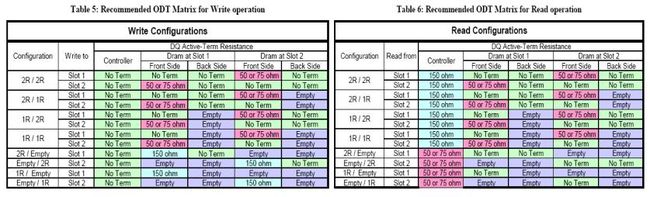

在 micron 的 appnote 给出如下的 odt 配置

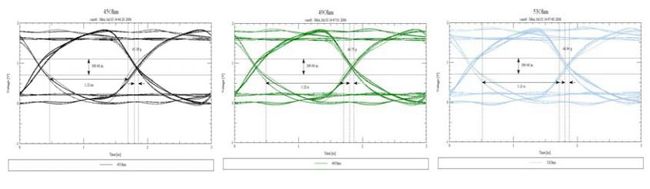

串扰的分析

通常串扰分为电感性以及电容性,他们在传输线上叠加就生成前向串扰和后向串

扰,其对于波形的影响表现在幅度以及 slew rate 上面,如果叠加成眼图来看,在

时序上表现为 jitter(负载加载效应)。相邻走线层要按照垂直方向走线也就是因为

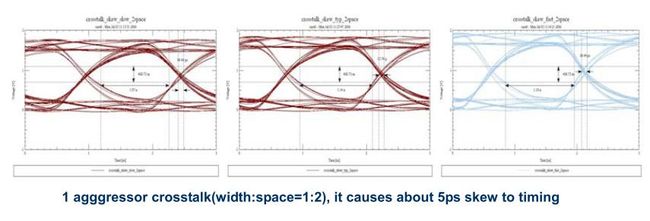

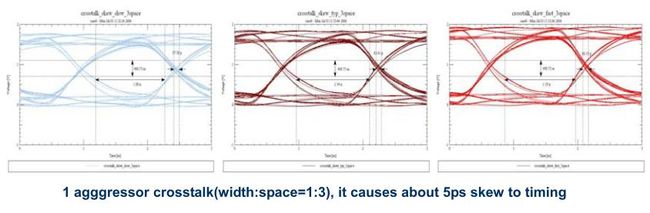

考虑宽边耦合 crosstalk。下图是不同的干扰眼图

从上图可以看出,采用 1:2 的 wdith:space 以及 1:3 的 wdith:space 波形差异不

大,因而设计的时候可以走 1:2 的 wdith:space(更短的线可以采用 1:1 等等)。

注意大家经常看到说 DDR2 走线要按照 1:2 的 wdith:space,实际上他们是根据

crosstalk 大小而确定,比如受驱动能力的影响,比如受线长的影响等

时序分析

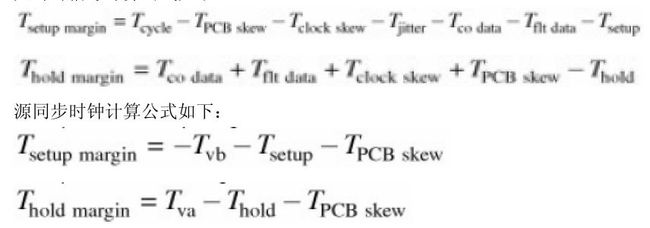

目前时序分析基本上分为共时钟信号时序以及源同步时钟时序类型,无论类型怎

么分,他们都表现为要满足 setup time 以及 hold time 要求。

共时钟信号计算公式如下:

具体计算公式的意义大家可以去查 high speed digital system design,在此有个很

重要问题,怎么在 spec 里面找时序参数?通常来说在 datasheet 里面有 electrical

characteristic,里面包含 AC/DC 参数,比如在 JESD79-2C.pdf P75 里面你可以找

到以下一些参数,对照时序图你可以找到你所需要的值

常来说 Tco 起基准作用,相当于基准坐标一样,你要计算时序的时候必须有个坐

标。对于共时钟信号的时序来说,由于他们基准坐标不一致(不同的 driver),

为了统一,需要测量不同 driver Tco,而对源同步信号的时序来(相同的 driver),

由于他们基准坐标一致,你可以不用考虑 Tco。下面给出时序计算的例子

Memory controller spec: tVB=0.6ns, tVA=0.5ns

Memory spec: tDS=0.1ns, tDH=0.175ns(注意有个 derating values table)

Interconnect Setup Margin=tVB-tDS=0.5ns

Interconnect Hold Margin=tVA-tDH=0.325ns

Skew by Crosstalk/Impedance estimation 0.03ns

最终得到结果

Formula1: Max (settle delay DQ0-switch delay DQS0)+Skew < Interconnect Setup

Margin

Formula2: Max (settle delay DQS0-switch delay DQ0)+Skew < Interconnect Hold

Margin

通过时序公式计算,我们可以确定大概长度范围(理论上源同步时序对于总长没

有要求,但是由于传输线损耗以及 DDR2 内部有返回时序影响,总长需要设定),

大致确定走线关系

规则制订

走线层:高速线布线的优先顺序:{XXX}, {XXX}, {XXX}…

走线的拓扑结构:Point to point, 1.75XODT150

走线线宽线距:stackup 确立

走线长度:根据时序计算

走线关系:DQ~DQS: 20mil(it will cause skew max about 5ps)

Clock 与 DQS 关系

Clock 与 ADDR/CMD/CTL 关系

小结

在此讨论几个细节问题:

1,DDR connector 的影响,在此只考虑 SLM 模型(可去 tyco 网站下载),更精

确点需要考虑 MLM 模型(tyco 那儿好像需要签 NDA 协议)

2,ISI 影响,由于 data patteren 与 ISI 有关系,在此统统以看眼图的 jiiter 来分析,

由于不是做研究,对于仿真来说粗略估算时序

3,SSN 影响,实际上在 interconnect 设计中,即使发现问题,你所能做的事情也

不多,解决 ssn 问题最关键的还是芯片设计,在此要结合 pi 设计

4,与测量的校准,

A,波形的校准,通常典型情况下,波形的趋势是一致,但是会有差异,表现在

仿真的波形 slew rate 比测量的波形的 slew rate 不一致,通常我对于测量波形

的 slew rate 表示怀疑,因为他们测量的是测试点位置,大家有兴趣可以去搭

建一个 topology 去看看在在 die 上波形和距离 die 上波形 500~1000mil 的波

形差异

B,时序的测量,通常典型情况下,测量的时序肯定要比仿真的时序大,因为他

们反应的是一般情况下的时序,而仿真考虑的是 worse case corner 情况

5,仿真会遇到时序计算出来负值,怎么办?特别是计算 DDR2 时序,在此有个

冗余问题,这儿需要经验,确定什么情况下能容许。A,需要查看下 spec,那些时序参数定义在什么情况,有些时候 spec 定义在 die

上,有时候定义在 pin 上,有时候时序定义测量在 Vref 上面等等都会影响你

时序的计算值

B,检查下你的时序计算公式,比如 DDR2 spec 定义 setup time 等用到 vih(ac)

vih(dc)值等等

参考文献

1. JESD79-2c (from www.jedec.org)

2. High-speed Digital Design

3. High-Speed Digital System Design

4. TN47-02 (from www.micron.com)

5. 1G DDR2 SDRAM (from www.micron.com)

6. Cadence SQ foundation 15.2