嵌入式 I2C总线协议

I2C总线详细介绍

2010-10-30 18:26:44| 分类: 面试总结 | 标签: |字号大中小 订阅

由于I2C只有一根数据线,因此其发送信息和接收信息不能同时进行。信息的发送和接收只能分时进行。I2C串行总线工作时传输速率最高可达400K bit/s。

I2C总线上的所有器件的SDA线并接在一起,所有器件的SCL线并接在一起,且SDA线和SCL线必须通过上拉电阻连接到正电源。

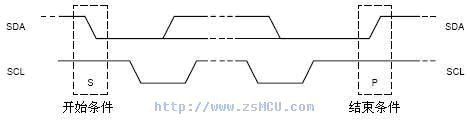

I2C总线的数据传输协议要比SPI总线复杂一些,因为I2C总线器件没有片选控制线,所以I2C总线数据传输的开始必须由主器件产生通信的开始条件(SCL高电平时,SDA产生负跳变);通信结束时,由主器件产生通信的结束条件(SCL高电平时,SDA产生正跳变)。

SDA线上的数据在SCL高电平期间必须保持稳定,否则会被误认为开始条件或结束条件,只有在SCL低电平期间才能改变SDA线上的数据。I2C总线的数据传输波形图如下图所示。

I2C应用实例

AT24C系列为美国ATMEL公司推出的串行COMS型E2PROM,具有功耗小,宽电压范围等优点。下图为AT24C系列E2PROM的引脚图。图中A0、A1、A2为器件地址引脚,Vss为地,Vcc为正电源,WP为写保护,SCL为串行时钟线,SDA为串行数据线。AT24C系列E2PROM采用I2C总线,I2C总线上可挂接多个接口器件,在I2C总线上的每个器件应有唯一的器件地址,按I2C总线规则,器件地址为7位二进制数,它与一位数据方向位构成一个器件寻址字节。器件寻址字节的最低位(D0)为方向位(读/写),最高4位(D7~D4)为器件型号地址(不同的I2C总线接口器件的型号地址由厂家给定,AT24C系列E2PROM的型号地址都为1010);其余3位(D3~D1)与器件引脚地址A2A1A0相对应。器件地址格式:

1010 A2A1A0。

对于E2PROM的片内地址,AT24C01和AT24C02由于芯片容量可用一个字节表示,故读写某个单元前,先向E2PROM写入一个字节的器件地址,再写入一个字节的片内地址。而AT24C04、AT24C08、AT24C16分别需要9位、10位和11位片内地址,所以AT24C04把器件地址中的A0作为片内地址的最高位,AT24C08把器件地址中的A1A0作为片内地址的最高两位,AT24C16把器件地址中的A2A1A0作为片内地址的最高三位。凡在系统中把器件的引脚地址用作片内地址后,该引脚在电路中不得使用,做悬空处理。AT24C32、AT24C64、AT24C128、AT24C256和AT24C512的片内地址采用两个字节。

AT24C系列E2PROM的读写操作原理

下列读写操作中SDA线上数据传送状态标记注释如下:

Start为启动信号(SCL为高电平,SDA产生负跳变),由主机发送。

Stop为结束信号(SCL为高电平,SDA产生正跳变),由主机发送。

AddressByte、AddreeeByte H、AddreeeByte L为地址字节,指定片内某单元地址,由主机发送。

data为数据字节,由数据发送方发送。

0 为肯定应答信号,由数据接收方发送。

1 为否定应答信号,由数据接收方发送。

主机控制数据线SDA时,在SCL高电平期间必须保持SDA线上的数据稳定,否则会被误认为对从机的起始条件或结束条件。主机只能在SCL低电平期间改变SDA线上的数据。主机写操作期间,用SCL的上升沿写入数据;主机读操作期间,用SCL的下降沿读出数据。

从AT24C系列AT24C01~AT24C16中读n个字节的数据格式:

![]()

从AT24C系列AT24C32~AT24C512中读n个字节的数据格式:

向AT24C系列AT24C01~AT24C16中写n个字节的数据格式(n<=页长,且n个字节不能跨页):

![]()

向AT24C系列AT24C32~AT24C512中写n个字节的数据格式(n<=页长,且n个字节不能跨页):

![]()

应答信号

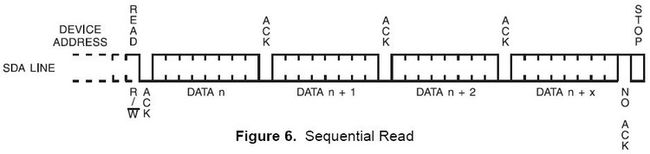

I2C总线数据传送时,每成功地传送一个字节数据后,接收器都必须产生一个应答信号。应答的器件在第9个时钟周期时将SDA线拉低,表示其已经收到一个8位数据。

I2C器件在接收到起始信号和从器件地址之后响应一个应答信号,如果器件已选择了写操作,则在每接收一个8位字节之后响应一个应答信号。

I2C器件工作在读模式时,在发送一个8位数据后释放SDA线(SDA置为高电平)并监视一个应答信号,一旦接收到主器件的应答信号,I2C器件则继续发送数据,如果主器件没有发送应答信号(发送非应答信号,即SDA为高电平),器件停止传送数据且等待一个停止信号。

1.I2C协议

2条双向串行线,一条数据线SDA,一条时钟线SCL。

SDA传输数据是大端传输,每次传输8bit,即一字节。

支持多主控(multimastering),任何时间点只能有一个主控。

总线上每个设备都有自己的一个addr,共7个bit,广播地址全0.

系统中可能有多个同种芯片,为此addr分为固定部分和可编程部份,细节视芯片而定,看datasheet。

1.1 I2C位传输

数据传输:SCL为高电平时,SDA线若保持稳定,那么SDA上是在传输数据bit;

若SDA发生跳变,则用来表示一个会话的开始或结束(后面讲)

数据改变:SCL为低电平时,SDA线才能改变传输的bit

1.2 I2C开始和结束信号

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

1.3 I2C应答信号

Master每发送完8bit数据后等待Slave的ACK。

即在第9个clock,若从IC发ACK,SDA会被拉低。

若没有ACK,SDA会被置高,这会引起Master发生RESTART或STOP流程,如下所示:

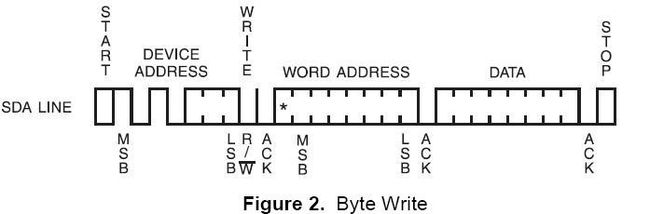

1.4 I2C写流程

写寄存器的标准流程为:

1. Master发起START

2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK

3. Slave发送ACK

4. Master发送reg addr(8bit),等待ACK

5. Slave发送ACK

6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK

7. Slave发送ACK

8. 第6步和第7步可以重复多次,即顺序写多个寄存器

9. Master发起STOP

写一个寄存器

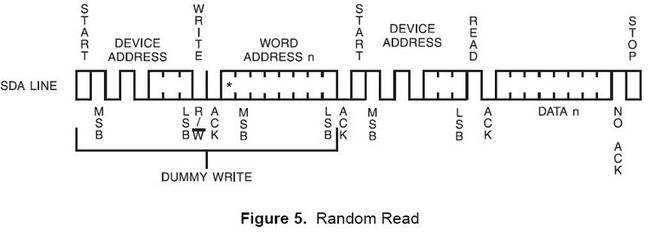

1.5 I2C读流程

读寄存器的标准流程为:

1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK

2. Slave发送ACK

3. Master发送reg addr(8bit),等待ACK

4. Slave发送ACK

5. Master发起START

6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK

7. Slave发送ACK

8. Slave发送data(8bit),即寄存器里的值

9. Master发送ACK

10. 第8步和第9步可以重复多次,即顺序读多个寄存器

读一个寄存器

读多个寄存器

2. PowerPC的I2C实现

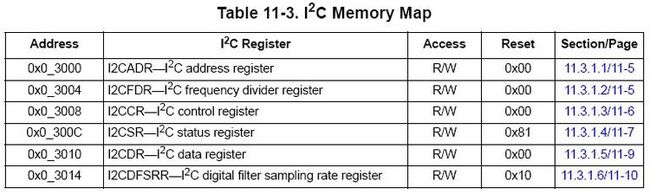

Mpc8560的CCSR中控制I2C的寄存器共有6个。

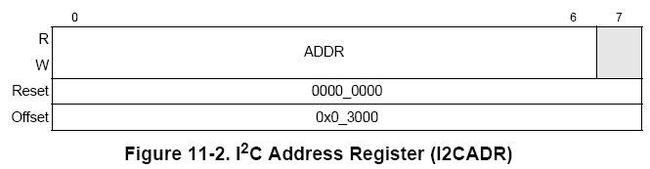

2.1 I2CADR 地址寄存器

CPU也可以是I2C的Slave,CPU的I2C地址有 I2CADR指定

2.2 I2CFDR 频率设置寄存器

The serial bit clock frequency of SCL is equal to the CCB clock divided by the divider.

用来设置I2C总线频率

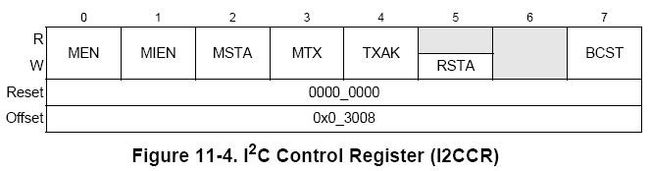

2.3 I2CCR 控制寄存器

MEN: Module Enable. 置1时,I2C模块使能

MIEN:Module Interrupt Enable. 置1时,I2C中断使能。

MSTA:Master/slave mode. 1 Master mode,0 Slave mode.

当1->0时,CPU发起STOP信号

当0->1时,CPU发起START信号

MTX:Transmit/receive mode select.0 Receive mode,1 Transmit mode

TXAK:Transfer acknowledge. 置1时,CPU在9th clock发送ACK拉低SDA

RSTA:Repeat START. 置1时,CPU发送REPEAT START

BCST:置1,CPU接收广播信息(信息的slave addr为7个0)

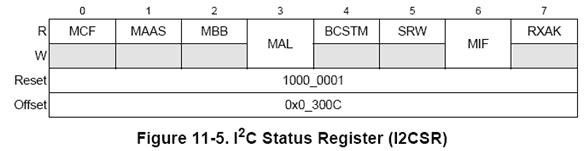

2.4 I2CSR 状态寄存器

MCF:0 Byte transfer is in process

1 Byte transfer is completed

MAAS:当CPU作为Slave时,若I2CDR与会话中Slaveaddr匹配,此bit被置1

MBB:0 I2C bus idle

1 I2C bus busy

MAL:若置1,表示仲裁失败

BCSTM:若置1,表示接收到广播信息

SRW:When MAAS is set, SRW indicates the value of the R/W command bit of the calling address, which is sent from the master.

0 Slave receive, master writing to slave

1 Slave transmit, master reading from slave

MIF:Module interrupt. The MIF bit is set when an interrupt is pending, causing a processor interrupt request(provided I2CCR[MIEN] is set)

RXAK:若置1,表示收到了ACK

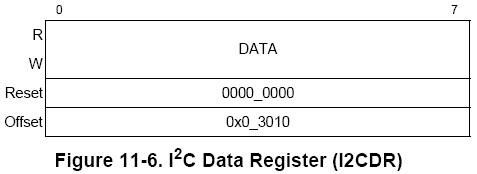

2.5 I2CDR 数据寄存器

这个寄存器储存CPU将要传输的数据。

3. PPC-Linux中I2C的实现

内核代码中,通过I2C总线存取寄存器的函数都在文件drivers/i2c/busses/i2c-mpc.c中

最重要的函数是mpc_xfer.

- static int mpc_xfer(struct i2c_adapter *adap, struct i2c_msg *msgs, int num)

- {

- struct i2c_msg *pmsg;

- int i;

- int ret = 0;

- unsigned long orig_jiffies = jiffies;

- struct mpc_i2c *i2c = i2c_get_adapdata(adap);

- mpc_i2c_start(i2c); // 设置I2CCR[MEN], 使能I2C module

- //一直读I2CSR[MBB],等待I2C总线空闲下来

- while (readb(i2c->base + MPC_I2C_SR) & CSR_MBB) {

- if (signal_pending(current)) {

- pr_debug("I2C: Interrupted\n");

- writeccr(i2c, 0);

- return -EINTR;

- }

- if (time_after(jiffies, orig_jiffies + HZ)) {

- pr_debug("I2C: timeout\n");

- if (readb(i2c->base + MPC_I2C_SR) ==

- (CSR_MCF | CSR_MBB | CSR_RXAK))

- mpc_i2c_fixup(i2c);

- return -EIO;

- }

- schedule();

- }

- for (i = 0; ret >= 0 && i <</FONT> num; i++) {

- pmsg = &msgs[i];

- pr_debug("Doing %s %d bytes to 0xx - %d of %d messages\n",

- pmsg->flags & I2C_M_RD ? "read" : "write",

- pmsg->len, pmsg->addr, i + 1, num);

- //根据消息里的flag进行读操作或写操作

- if (pmsg->flags & I2C_M_RD)

- ret = mpc_read(i2c, pmsg->addr, pmsg->buf, pmsg->len, i);

- else

- ret = mpc_write(i2c, pmsg->addr, pmsg->buf, pmsg->len, i);

- }

- mpc_i2c_stop(i2c); //保证为I2CCSR[MSTA]为0,保证能触发STOP

- return (ret <</FONT> 0) ? ret : num;

- }

- static int mpc_write(struct mpc_i2c *i2c, int target,

- const u8 * data, int length, int restart)

- {

- int i;

- unsigned timeout = i2c->adap.timeout;

- u32 flags = restart ? CCR_RSTA : 0;

- //以防万一,保证I2C模块使能起来

- if (!restart)

- writeccr(i2c, CCR_MEN);

- //写了I2CCR[CCR_MSTA],触发CPU发起START信号

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_MSTA | CCR_MTX | flags);

- //CPU发送一个字节,slave I2C addr和0 (写操作bit)

- writeb((target <</FONT><</FONT> 1), i2c->base + MPC_I2C_DR);

- if (i2c_wait(i2c, timeout, 1) <</FONT> 0) //等待slave 发ACK

- return -1;

- for (i = 0; i <</FONT> length; i++) {

- writeb(data[i], i2c->base + MPC_I2C_DR); //CPU接着发数据,包括reg addr和data

- if (i2c_wait(i2c, timeout, 1) <</FONT> 0) //等待slave 发ACK

- return -1;

- }

- return 0;

- }

- static int i2c_wait(struct mpc_i2c *i2c, unsigned timeout, int writing)

- {

- unsigned long orig_jiffies = jiffies;

- u32 x;

- int result = 0;

- if (i2c->irq == 0)

- { //循环读I2CSR,直到I2CSR[MIF]置1

- while (!(readb(i2c->base + MPC_I2C_SR) & CSR_MIF)) {

- schedule();

- if (time_after(jiffies, orig_jiffies + timeout)) {

- pr_debug("I2C: timeout\n");

- writeccr(i2c, 0);

- result = -EIO;

- break;

- }

- }

- x = readb(i2c->base + MPC_I2C_SR);

- writeb(0, i2c->base + MPC_I2C_SR);

- } else {

- result = wait_event_interruptible_timeout(i2c->queue,

- (i2c->interrupt & CSR_MIF), timeout * HZ);

- if (unlikely(result <</FONT> 0)) {

- pr_debug("I2C: wait interrupted\n");

- writeccr(i2c, 0);

- } else if (unlikely(!(i2c->interrupt & CSR_MIF))) {

- pr_debug("I2C: wait timeout\n");

- writeccr(i2c, 0);

- result = -ETIMEDOUT;

- }

- x = i2c->interrupt;

- i2c->interrupt = 0;

- }

- if (result <</FONT> 0)

- return result;

- if (!(x & CSR_MCF)) {

- pr_debug("I2C: unfinished\n");

- return -EIO;

- }

- if (x & CSR_MAL) { //仲裁失败

- pr_debug("I2C: MAL\n");

- return -EIO;

- }

- if (writing && (x & CSR_RXAK)) {//写后没收到ACK

- pr_debug("I2C: No RXAK\n");

- writeccr(i2c, CCR_MEN);

- return -EIO;

- }

- return 0;

- }

- static int mpc_read(struct mpc_i2c *i2c, int target,

- u8 * data, int length, int restart)

- {

- unsigned timeout = i2c->adap.timeout;

- int i;

- u32 flags = restart ? CCR_RSTA : 0;

- //以防万一,保证I2C模块使能

- if (!restart)

- writeccr(i2c, CCR_MEN);

- //注意这里,再次把CCR_MSTA置1,再触发 START

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_MSTA | CCR_MTX | flags);

- //CPU发送slave I2C addr和读操作1

- writeb((target <</FONT><</FONT> 1) | 1, i2c->base + MPC_I2C_DR);

//等待Slave发ACK

- if (i2c_wait(i2c, timeout, 1) <</FONT> 0)

- return -1;

- if (length) {

- if (length == 1)

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_MSTA | CCR_TXAK);

- else //为什么不置 TXAK

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_MSTA);

- readb(i2c->base + MPC_I2C_DR);

- }

- for (i = 0; i <</FONT> length; i++) {

- if (i2c_wait(i2c, timeout, 0) <</FONT> 0)

- return -1;

- //注意这里TXAK置1,表示CPU每收到1byte数据后,会发送ACK

- if (i == length - 2)

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_MSTA | CCR_TXAK);

- //注意这里CCR_MSTA [1->0] CPU会触发STOP

- if (i == length - 1)

- writeccr(i2c, CCR_MIEN | CCR_MEN | CCR_TXAK);

- data[i] = readb(i2c->base + MPC_I2C_DR);

- }

- return length;

- }

引言

I2S(InterIC Sound Bus)是飞利浦公司针对数字音频设备之间的音频数据传输而制定的一种总线标准,采用沿独立的导线传输时钟与数据信号的设计,通过分离数据和时钟信号,避免了时差诱发的失真。I2S总线简单有效,可以有效提升输出数据的质量,在各种嵌入式音频系统中有广泛应用。但是在嵌入式音频系统设计中,并不是所有的MCU都支持I2S总线格式,再加上I2S还没有统一的接口标准,不同的厂家生产的设备接口也是五花八门,采用软件模拟实现I2S总线可有效解决在不支持其的MCU和设备之间通过I2S总线实现数据传输时出现的问题。

本文通过在以太网数字语音广播系统中软件模拟I2S总线实现语音数据传输,给出了软件模拟实现I2S总线的方法。

1 I2S总线规范

I2S为三线总线,3个信号分别为:

① 串行时钟SCK,也叫位时钟(BCK)。即每发送1位数字音频数据,SCK上都有1个脉冲。SCK的频率=2×采样频率×采样位数。在数据传输过程中,I2S总线的发送器和接收器都可以作为系统的主机来提供系统的时钟频率。

② 帧时钟WS,即命令(声道)选择,用于切换左右声道的数据。WS的频率等于采样频率,由系统主机提供。WS为“1”表示传输的是左声道的数据,WS为“0”表示传输的是右声道的数据。

③ 串行数据信号SD,用于传输二进制补码表示的音频数据。

I2S格式的信号无论有多少位有效数据,数据位的最高位(MSB)总是被最先传输,1次能够发送的数据决定于I2S格式的有效位数。

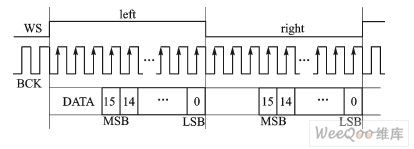

1个典型的I2S信号时序如图1所示

图1 I2S总线典型时序图

随着技术的发展,在统一的I2S接口下出现了多种不同的数据格式。根据SD信号相对于SCK和WS位置的不同,分为左对齐和右对齐2种格式,如图2和图3所示。

图2 16位有效位数的左对齐格式

图3 16位有效位数的右对齐格式

在上面2种数据传输格式中,当WS为“1”时传输的是左声道的数据,当WS为“0”时传输的是右声道的数据。为了保证数字音频信号的正确传输,发送端和接收端必须采用相同的数据格式。

2 软件模拟I2S

以太网数字语音广播系统主要是指以以太网为传播介质提供音频服务的广播系统,将语音信号以标准IP包的形式在以太网上进行传送,以实现语音广播功能。该系统在PC机端通过麦克风采集语音数据,然后将采集到的语音数据通过以太网发送给嵌入式终端,嵌入式终端将接收到的语音数据进行数/模转换后进行播放。系统实现框图如图4所示[5]。

图4 以太网数字语音广播系统框图

图5 LM3S8962与MS6336的连接图

广播系统终端的MCU LM3S8962将接收到的语音数据通过I2S总线发送给语音解码芯片MS6336进行数/模转换并播放,

LM3S8962和MS6336的连接如图5所示。为了完整还原出语音信号,需要保证软件模拟I2S信号时序严格精确,高低电平的转换采用延时程序实现。MS6336为16位D/A芯片,其I2S时序如图6所示。

图6 MS6336的典型I2S时序图

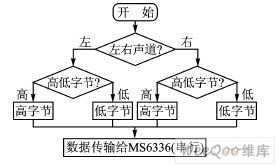

该系统中的语音数据双声道,16位采样,1个采样点的数据为4字节,1个采样点数据通过MCU发送给MS6336,数据发送流程如图7所示。

图7 1个采样点数据发送流程

软件模拟I2S引脚的定义如下:

#define I2S_WS GPIO_PIN_5//模拟I2S声道选择时钟控制位

#define I2S_BCK GPIO_PIN_6//模拟I2S位时钟控制位

#define I2S_DATA GPIO_PIN_7//模拟I2S数据传送位

根据MS6336的I2S总线格式以及数据发送流程,软件模拟I2S总线的步骤如下:

① 根据语音数据采样率及采样位数计算得到SCK的值和WS的值(WS的值等于采样频率)。

系统采样率为44.1 kHz,则SCK=2×44.1 kHz×103×16=1 411 200 Hz,WS=44 100 Hz。1个SCK时钟周期T=1/SCK=07 μs。采用延时程序模拟SCK时钟周期需要应用示波器来精确延时时间。本系统中一个SCK周期的延时为delayI2S(2)。

② 将WS、BCK和DATA均置为高电平。

③ 选择左右声道。首先发送左声道数据,将WS置低(若发送右声道数据则将WS置高)。

for(ChannelCnt=0;ChannelCnt<2;ChannelCnt++){//双声道选择播放

if(ChannelCnt==0){//右声道选择信号为高电平

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_WS << 2))) = ~I2S_WS;

}

else{//左声道选择信号为低电平

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_WS << 2))) = I2S_WS;

}

……

}

④ 选择高低字节。将左声道数据以高低字节的顺序发送,在发送高字节第1位数据之前先发送1个周期的串行时钟。

for(HorLCnt=0;HorLCnt<2;HorLCnt++){//声道数据高低字节选择

if(ChannelCnt==1){//左声道

if(HorLCnt==0){//低字节

c=*(SampleData+1);//SampleData指向音频数据缓冲区首地址,即左声道低字节

delayI2S(2);//发送第一个数据位之前需要延迟一个位时钟周期

}

else{//低字节

c=*SampleData;

}

}

……

}

⑤ 开始传输音频数据(音频数据的传输在SCK下降沿准备数据,在SCK的上升沿发

送给数据接收端)。将采样点左声道数据的高字节最高位送给SD,设置SCK为低电平,此时为SCK的下降沿,数据准备好。延时半个SCK周期以后将SCK置为高电平,此时SD线上的数据发送给数据接收端,延时半个SCK周期。依次将左声道剩余位数据按照最高位的方式发送出去。

for(BitCnt=0;BitCnt<8;BitCnt++){//1次传送的数据长度为8位,先传送高字节再传送低字节置时钟线SCK为低,开始准备数据位

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_BCK << 2))) = ~I2S_BCK;

if((c<<BitCnt)&0x80) {

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_DATA << 2))) = I2S_DATA;

}

else{

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_DATA << 2))) = ~I2S_DATA;

}

delayI2S(1); //延时半个SCK时钟周期置时钟线为高,开始传输数据位

HWREG(GPIO_PORTA_BASE + (GPIO_O_DATA + (I2S_BCK << 2))) = I2S_BCK;

delayI2S(1);//延时半个时钟周期

}

⑥ 当将1个采样点的左声道的数据发送完以后,延时2个SCK周期,然后发送右声道的数据(同左声道数据的发送过程)。

根据以上的过程对每个采样点的数据进行处理,就可以实现通过软件模拟I2S总线传输音频数据了。以上实现的是典型I2S时序模拟,而左对齐和右对齐2种格式只是时序稍有差异,模拟实现过程同典型I2S总线模拟实现过程基本相同。

结语

在以太网数字语音广播系统中应用软件模拟实现I2S总线时序,能够成功地实现语音信号的数据传输,实现语音信号的实时广播,表明了软件模拟实现I2S总线的可行性,为解决不支持I2S总线的MCU和各种I2S总线设备间的通信提供了一种可行的方法。但是,在应用软件模拟实现I2S的以太网数字语音广播系统实时播放语音信号时,存在一些噪声,表明在采用软件模拟实现I2S的时序精确性上存在一些欠缺。