S3C2440时钟详细描述

S3C2440 CPU默认的工作主频为12MHz或16.9344MHz,这里使用最多的是12M。使用PLL电路可以产生更高的主频供CPU及外围器件使用。

S3C2440有两个PLL:MPLL和UPLL,UPLL专用与USB设备。MPLL用于CPU及其他外围器件。

通过MPLL会产生三个部分的时钟频率:FCLK、HCLK、PLCK。FCLK用于CPU核,HCLK用于AHB总线的设备(比如SDRAM),PCLK用于APB总线的设备(比如UART)。从时钟结构图中可以查看到使用不同时钟频率的硬件。

(注:这里要注意从图中看出,Uart使用的是PCLK,后面Uart实验会用到)

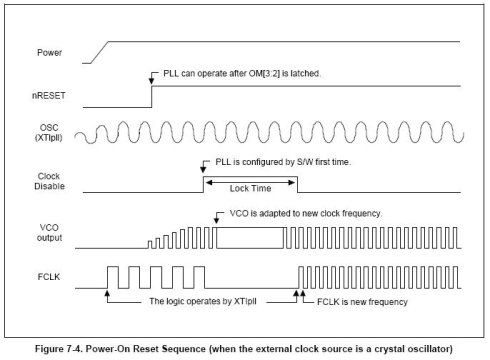

下面介绍MPLL的启动流程:

请跟随FCLK的图像了解启动过程:

1、上电几毫秒后,晶振输出稳定,FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

2、我们可以在程序开头启动MPLL,在设置MPLL的几个寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

3、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

设置S3c2440的时钟频率就是设置MPLL的几个寄存器:

1、LOCKTIME:设为0x00ffffff

前面说过,MPLL启动后需要等待一段时间(Lock Time),使得其输出稳定。位[23:12]用于UPLL,位[11:0]用于MPLL。使用确省值0x00ffffff即可。

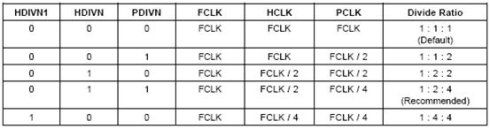

2、CLKDIVN:用来设置FCLK:HCLK:PCLK的比例关系,默认为1:1:1

这里值设为0x03,即FCLK:HCLK:PCLK=1:2:4

CLKDIVN不同的设置及对应的时钟比例关系如下图:

3、MPLLCON:设为(0x5c << 12)|(0x04 << 4)|(0x00),即0x5c0040

对于MPLLCON寄存器,[19:12]为MDIV,[9:4]为PDIV,[1:0]为SDIV。有如下计算公式:

MPLL(FCLK) = (m * Fin)/(p * 2^s)

其中: m = MDIV + 8, p = PDIV + 2

Fin 即默认输入的时钟频率12MHz。MPLLCON设为0x5c0040,可以计算出FCLK=200MHz,再由CLKDIVN的设置可知:HCLK=100MHz,PCLK=50MHz。

到这里我们应该彻底弄清楚了程序中经常出现的几个CLK:

Fin,MPLL,UPLL,FCLK,HCLK,PCLK.

Fin指CPU外围接的晶振本身的频率,通常为12MHz。

MPLL和UPLL分别指的是用于供整机系统的PLL和专用于USB的UPLL。

FCLK = MPLL = (m * Fin)/(p + 2^s);

HCLK,PCLK受CLKDIVN寄存器的影响,即当FCLK确定后,CLKDIVN决定了HCLK和PCLK,具体如上表。

这里UART使用PCLK,要想串口打印信息正常显示,这里是关键!

通常我们将如上时钟初始化的过程写成clock_init函数供其他函数调用,代码如下:

void clock_init(void)

{

rLOCKTIME = 0xFFFFFF;

rCLKDIVN = 0x3;

rMPLLCON = 0x5c0040;

}