《视频解密》中文版(第四版) 第六章 数字视频接口(第三部分)

视频模块接口(VMI)开发用于不同多媒体IC生产商的互联。它的目标是如MPGE解码器,NTSC/PAL解码器和图像芯片的视频接口标准化。

图6.39 VMI 8比特 4:2:2 YCbCr扫描行数据

视频数据格式

VMI标准的8比特4:2:2 YCbCr视频数据标准的格式如图6.39所示。许多器件也支持其他在BT.601视频接口章节讨论的YCbCr和R’G’B’格式。

控制信号

除了视频数据之外,还有4个控制信号:

HREF 水平消影

VREF 垂直同步

VACTIVE 有效视频

PIXCLK 2×采样时钟

对于8比特和10比特4:2:2YCbCr数据格式,PIXCLK是2×采样时钟。对于其他格式数据PIXCLK是1×采样时钟。对于视频源,控制信号和视频数据的输出跟随在PIXCLK的上升沿。对于接收端,控制信号和视频数据的采样在PIXCLK的上升沿。

当VACTIVE有效时,有效R’G’B’或YCbCr视频数据存在。虽然VACTIVE有效发送被允许,但是它是扩展让硬件拷贝视频数据。对于不支持VACTIVE信号的系统,HREF一般可以连接到VACTIVE信号以实现最小损失。

为了支持不产生行锁时钟的源。一个数据有效信号(DVALID#)被使用。当DVALID#有效时,存在有效数据。

HREF有效时,每一扫描行的视频数据有效,包括垂直消影周期。

VREF有效时长是6个扫描行,在垂直同步开始后的半扫描行后开始有效。

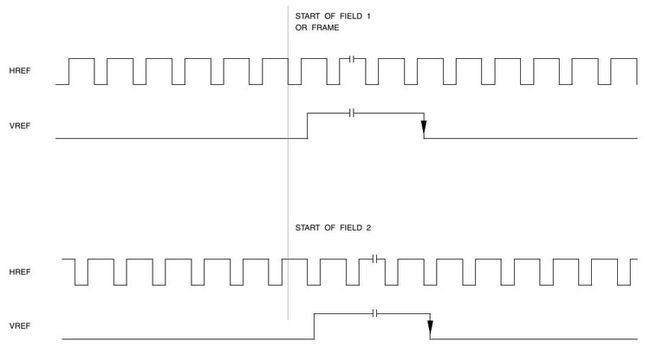

对于隔行扫描视频,VREF的后沿被用于采样HREF信号。如果HREF有效,该场是场1.如果HREF为低,该场是场2.对于非隔行扫描视频,VREF的前沿指示新的一帧的开始。图6.40指示了典型的HREF和VREF的关系。

图6.40 VMI接口的典型HREF和VREF关系

接收端考虑

假设每行和场消影期的采样点数不定,否则这个应用可能不适合所有的发送源。

视频数据的输入建立和保持时间分别为5和0ns,它们和PIXCLK的上升沿有关。

VACTIVE的输入建立和保持时间分别为5和0ns,它们和PIXCLK的上升沿有关。

HREF和VREF的输入建立和保持时间分别为5和5ns,它们和PIXCLK的上升沿有关。

“BT.656”接口

对于ICs的BT.656接口是基于专业视频的BT.656并行接口,在本章的前面部分已经讨论了(图6.1~6.9)。使用EAV和SAV序列来指示视频的定时信息,以减少所需要的引脚。定时信号H,V和F的普通视频格式在第四章中已介绍过。

标准IC信号电平和时序被使用,任何分辨率都可以被支持。

视频数据格式

使用8比特4:2:2 YCbCr视频数据,如图6.1~6.9所示。虽然视频源应该在EAV和SAV序列标产生4比特保护数据,但是由于接收端现实使用芯片之间点对点的传输而可以忽略它们。

控制信号

CLK是2×采样时钟。对于视频源,控制信号和视频数据的输出跟随在CLK的上升沿。对于接收端,控制信号和视频数据的采样在PIXCLK的上升沿。

这个接口典型应用于SDTV分辨率的限制。为了支持HDTV分辨率,一些设计使用时钟的双沿传输数据。

视频缩放端口(ZV端口)

应用于笔记本电脑,ZV端口是一个单向的PC卡之间的主机适配器和图形控制器点到点总线。它支持将视频数据从PC卡到图形缓冲区的实时传输。

PC卡的主适配器有一个多媒体模式配置。如果一个非ZV PC卡插入插槽,主适配器不切换到多媒体模式,PC卡就是默认模式。一旦ZV卡插入,主适配器就转换到多媒体模式,管脚分配改变。如表6.33所示,PC卡的A6~A25引脚,SPKR#,INPACK#和IOIS16#被ZC端口的视频信号(Y0~Y3,CbCr0~CbCr7,HREF,VREF和PCLK)和4通道音频信号(MCLK,SCLK,LRCK和SDATA)代替。

| PC卡信号 |

ZV端口信号 |

PC卡信号 |

ZV端口信号 |

PC卡信号 |

ZV端口信号 |

| A25 |

CbCr7 |

A17 |

Y1 |

A9 |

Y0 |

| A24 |

CbCr5 |

A16 |

CbCr2 |

A8 |

Y2 |

| A23 |

CbCr3 |

A15 |

CbCr4 |

A7 |

SCLK |

| A22 |

CbCr1 |

A14 |

Y6 |

A6 |

MCLK |

| A21 |

CbCr0 |

A13 |

Y4 |

SPKR# |

SDATA |

| A20 |

Y7 |

A12 |

CbCr6 |

IOIS16# |

PCLK |

| A19 |

Y5 |

A11 |

VREF |

INPACK# |

LRCK |

| A18 |

Y3 |

A10 |

HREF |

|

|

表6.33 PC卡和ZV端口信号分布对比

视频数据格式

如图6.36所示,使用16比特的4:2:2YCbCr数据格式。

控制信号

除了视频数据之外,还有4个控制信号:

HREF 水平参考

VREF 垂直同步

PCLK 1×采样时钟

HREF,VREF和PCLK的时序和前面VMI接口讨论的一样。

视频接口端口(VIP)

VESA视频接口(VESA VIP)规范了ICs的BT.656增强接口,前面已经讨论过。它的基本应用是一个器件连接超过4个的图像控制芯片,这一概念很容易地应用于其他应用。

它的接口有3部分:

主控接口

VIPCLK 主时钟

HAD0~HAD7 主地址/数据总线

HCTL 主控制信号

视频接口:

PIXCLK 视频采样时钟

VID0~VID7 低视频数据总线

VID1,VIDB 10比特数据扩展

XPIXCLK 视频采样时钟

XVID0~XVID7 高视频数据总线

XVIDA,XVIDB 10比特数据扩展

系统接口

VRST# 复位

VIRQ# 中断请求

主控接口信号有图像控制器提供。基本上使用2,4,或8比特PCI接口版本。VIPCLK的频率范围是25~33MHz。PIXCLK和XPIXCLK的最大频率分别是75和80MHz。

视频接口

对于BT.656接口4个特殊字序列插入到8比特或10比特4:2:2 YCbCr视频序列中,用于指示有效视频开始(SAV)和有效视频结束(EAV)。这些序列也指示何时出现水平和垂直同步和那一场正在被传送。

VIP修改了BT.656的EAV和SAV序列,如表6.34所示。BT.656设计用于支持设备之间的长电缆互联,所以在状态字中使用了4比特保护为(P0~P3)。对于芯片之间的互联,这些保护可以不需要,所以这些比特位用于其它目的。对于普通视频的定时信号H,V和F如第四章中所示。VIP的状态字定义如下:

T=“0”任务B T=“1”任务A

F=“0”场1 F=“1”场2

V=“1”位于垂直消影期

H=“0”SAV序列 H=“1”EAV序列

|

|

8比特数据 |

|||||||

| D7(MSB) |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| 同步码 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

| 状态字 |

T |

F |

V |

H |

N |

R |

0 |

E |

表6.34 VIP的EAV和SAV序列

任务比特T是可编程的。如果需要兼容BT.656,它就被置为常“1”。否则,它可以用于指示两类数据流中的哪一类存在:流A=“1”和流B=“0”。也可以当T为“0”是,存在2×过采样VBI数据,“1”则相反。

在非隔行扫描中比特N指示源数据是逐行扫描(“1”)或隔行扫描(“0”)。

重复比特位R为“1”时表示当前场是重复场。这种情况只在3:2下拉。重复比特位(R)和非隔行扫描的比特(N)结合使用,能使图像控制器硬件处理Bob和波,就像3:2下拉。

扩展标志位E为“1”时表示另一个字节跟在EAV后面。表6.35所示是扩展字节。这个字节尽在EAV序列有效。如果比特E是“1”,一个扩展字节紧随其后。这允许在需要时任何扩展字节数连接在一起。

|

|

8比特数据 |

|||||||

| D7(MSB) |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| 扩展字节 |

|

用户定义 |

E |

|||||

表6.35 VIP EAV序列的扩展字节

与专业视频接口不同,00H可以用于有效视频阶段用于指示无效视频采样。这被用于容许图像尺度变换和平方像素时序。

视频数据格式

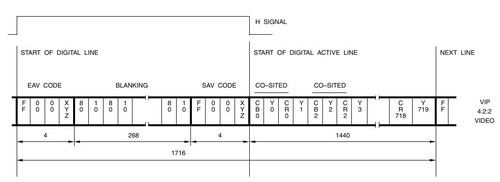

在8比特模式(图6.41),除非提及不同之处,否则视频接口类是于BT.656。XVID0~XVID7没有使用。

16比特模式(图6.42),SAV和EAV序列,Y视频数据,辅助包头和偶数字节辅助数据在低8比特通道(VID0~VID7)传送。CbCr数据和奇数字节的辅助数据在高8比特通道(XVID0~XVID7)传送。注意“跳过数据”(00H)在有效视频期间必须出现于16比特格式,保持16比特数据对齐。

VIDA,VIDB,XVIDA和XVIDB信号支持10比特视频数据。VIDA和XVIDA是最低有效位。

图6.41 8比特VIP一扫描行的视频接口数据。480i;每行720个采样点,27MHz时钟

图6.42 16比特VIP一扫描行的视频接口数据。

1080i;每行1920个采样点,74.176或74.25 MHz时钟

辅助数据

辅助数据在消影期包被用来传送如数字音频,字幕和图文等信息,如表6.36所示。于专业视频接口不同,数据00H和FFH可以用于辅助数据区。注意前面定义的用于专业视频设备的辅助数据格式可能不再适用。

DID中的DID2指示辅助数据是否存在于第一场或第二场:

|

|

8比特数据 |

|||||||

| D7(MSB) |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

| 辅助数据标志(AFD) |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

| 数据ID(DID) |

|

EP |

0 |

1 |

0 |

DID2 |

DID1 |

DID0 |

| SDID |

|

EP |

用户定义值 |

|||||

| 计数器(DC) |

|

EP |

DC5 |

DC4 |

DC3 |

DC2 |

DC1 |

DC0 |

| 内部数据ID0 |

用户定义值 |

|||||||

| 内部数据ID1 |

用户定义值 |

|||||||

| 数据字0 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| … |

… |

|||||||

| 数据字N |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

| 校验 |

|

EP |

CS5 |

CS4 |

CS3 |

CS2 |

CS1 |

CS0 |

| 可选填充数据 |

|

EP |

0 |

0 |

0 |

0 |

0 |

0 |

注:EP = D0~D5的偶校验

表6.36 VIP的一般辅助数据包格式

0 场1

1 场2

DID中的DID1~DID2指示何种辅助数据类型存在

00 场开始

01 VBI分片数据,行1~23

10 场结束VBI数据,行23

11 分片的VBI数据,行24到结束

数据计数器DC的值指示有多少个双字(4字节)辅助数据存在。这样,辅助数据包中DID后的数据必须是4的整数倍。1~3个可选填充字节可能被添加到校验数据之后以符合这个要求。

当DID1~DID0是“00”或“10”时,助数据或校验不存在。数据计数器(DC)的值是“00000”,它是数据包的最后数据域。

消费类分量接口

许多设备之间数字视频的传送解决方案已经被开发了许多年。DVI和HDMI标准是最流行的消费类数字视频接口。

数字虚拟接口(DVI)

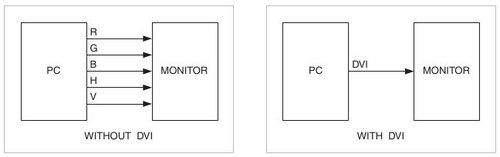

1998年建立了数字显示工作组(DDWG),它的目的是满足PC和VGA监视器数字视频接口的标准化,如图6.43所示。DVI1.0规范发表于1999年4月。

图6.43 使用DVI连接VGA监视器和PC

设计用于实时传送非压缩的数字视频,DVI支持的PC图像分辨率超过1600×1200,并支持HDTV分辨率,包括720p,1080i和1080p。

2003年,消费类电子工业开始使DVD播放器和有线/卫星机顶盒包含DVI输出接口。含有DVI输入接口的数字电视和LCD/等离子显示器也开始出现。

技术

DVI是基于数字平板(DFP)接口,加强它支持更多的格式和时序。它也支持了高带宽数字内容保护(HDCP)规范,以防止未经授权的内容拷贝。

DVI接口还支持VESA的扩展显示识别数据(EDID)标准,显示数据通道(DDC)标准(以前读作EDID)和监视器定时规范(DMT)。

DDC和EDID能支持显示器的自动检测和配置。扩展显示识别数据(EDID)用于支持显示器即插即用的能力。描述显示器支持视频格式的数据存储于显示器。这种数据在视频源请求时通过DVI接口提供给视频源设备。视频源就可以根据源视频的格式和所要支持的视频格式,选择它的视频输出格式,以支持目标显示器。视频源设备负责必要的视频格式转换以使视频格式符合显示器显示。

另外,EIA-861标准规范了强制和可选支持分辨率和时序,以及如何加入如宽高比和格式信息的数据。

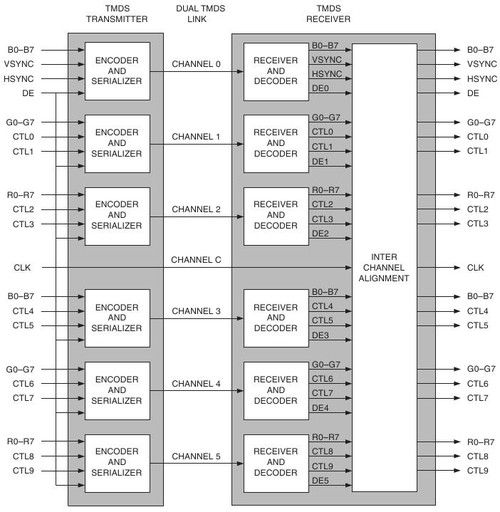

TMDS链路

DVI使用过渡最小差分信号(TMDS)。8比特视频数据转换成10比特过渡最小直流平衡数值,然后串行化。接收端解串数据,并将数据转换成8比特。这样为了传送数字R’G’B’数据,需要3组TMDS信号构成一个TMDS接头。

“TFT数据映射”用于支持最小要求:一个时钟周期一个像素,一条通道8比特,MSB对齐。

一组或两组TMDS连接器都可使用,如图6.44和6.45所示,它依赖于格式和时序要求。一个支持两组TMDS连接的系统必须支持一组连接和两组连接之间的动态切换。一个DVI连接器能支持两组TMDS连接。

图6.44 DVI的单TMDS连接

单个TMDS连接支持采样频率从15~165MHz视频分辨率和时序。分辨率和时序的采样频率165~330MHz视频需要两路TMDS连接,每组TMDS连接工作于半速率模式。因此,两个TMDS连接共享时钟和带宽,使两路达到均衡。

视频数据格式

典型地,24位R’G’B’数据用一个链路传输。对于每个颜色分量超过8比特的应用,第二个TMDS链路可以用于传输额外的地位比特。

对于PC应用,R’G’B’数据的典型范围是00H~FFH。对于消费类应用,R’G’B’数据的典型范围是10H~EBH(数据小于10H或者大于EBH也偶尔用于处理)。

控制信号

除了视频数据之外,DVI发送和接收芯片为连接系统中的其他芯片典型使用可达14个控制信号。

HSYNC 水平同步

VSYNC 垂直同步

DE 数据是能

CTL0~CTL3 保留(链路0)

CTL4~CTL9 保留(链路1)

CLK 1×采样时钟

图6.45 DVI的双TMDS连接

当DE为“1”时,有效视频被传送。当DE为“0”时,HSYNC,VSYNC和CTL0~CTL9信号被传送。HSYNC和VSYNC可以是有极性的。

一个问题是,有些HDTVs水平时序使用YPbPr三电平同步下降沿,而不是上升沿的中心。当显示器连接DVI接口时,将导致图像偏移2.3%。在这种情况下提供调整关于YPbPr三电平同步时序的DVI嵌入同步时序能力是很有用的。许多固定像素的显示器如DLP,LCD和等离子体等使用DE信号取代参考时序来避免这个问题。

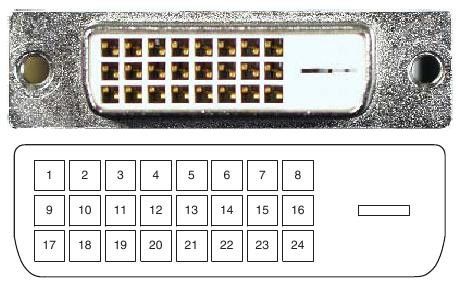

数字DVI(DVI-D)连接器

数字DVI连接器,支持双路操作,包括24个连接引脚,3排8针管脚分布,如图6.46所示。表6.37列举了引脚分配。

图6.46 DVI-D连接器

| 引脚 |

信号 |

引脚 |

信号 |

引脚 |

信号 |

| 1 |

D2- |

9 |

D1- |

17 |

D0- |

| 2 |

D2 |

10 |

D1 |

18 |

D0 |

| 3 |

外壳 |

11 |

外壳 |

19 |

外壳 |

| 4 |

D4- |

12 |

D3- |

20 |

D5- |

| 5 |

D4 |

13 |

D3 |

21 |

D5 |

| 6 |

DDC SCL |

14 |

+5V |

22 |

外壳 |

| 7 |

DDC SDA |

15 |

地 |

23 |

CLK |

| 8 |

保留 |

16 |

热插拔检测 |

24 |

CLK- |

表6.37 DVI-D连接器信号分布

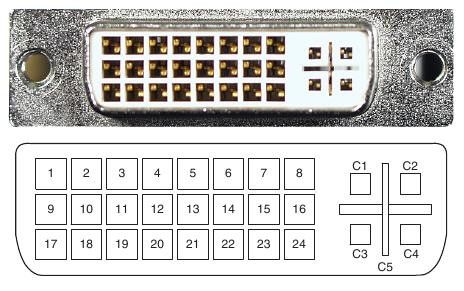

数字-模拟DVI(DVI-I)连接器

除了数字DVI连接器的24连接引脚之外,数字-模拟DVI增加了5个引脚以支持模拟视频,而成为29引脚的连接器,如图6.47所示。表6.38列举了引脚分配。

HSYNC 水平同步信号

VSYNC 垂直同步信号

RED 模拟视频红

GREEN 模拟视频绿

BLUE 模拟视频兰

图6.47 DVI-I连接器

| 引脚 |

信号 |

引脚 |

信号 |

引脚 |

信号 |

| 1 |

D2- |

9 |

D1- |

17 |

D0- |

| 2 |

D2 |

10 |

D1 |

18 |

D0 |

| 3 |

外壳 |

11 |

外壳 |

19 |

外壳 |

| 4 |

D4- |

12 |

D3- |

20 |

D5- |

| 5 |

D4 |

13 |

D3 |

21 |

D5 |

| 6 |

DDC SCL |

14 |

+5V |

22 |

外壳 |

| 7 |

DDC SDA |

15 |

地 |

23 |

CLK |

| 8 |

垂直同步 |

16 |

热插拔检测 |

24 |

CLK- |

| C1 |

红 |

C2 |

绿 |

C3 |

兰 |

| C4 |

水平同步 |

C5 |

地 |

|

|

表6.38 DVI-I连接器信号分布

模拟信号的操作和标准的VGA连接器相同。

DVI-A只能连接于DVI-I的模拟管脚,它是公的插头。DVI-A只能用于线缆端连接,用于转换传统的VGA模拟信号。

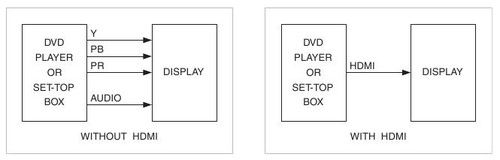

高清多媒体接口(HDMI)

虽然DVI接口传送非压缩实时数字RGB视频到显示器,但是消费电子工业倾向于基于DVI技术一个更小巧,更灵活的解决方案。2002年4月,HDMI小组由日立,松下,飞利浦,晶像,索尼,汤姆逊和东芝公司组建成立。

HDMI接口可以将8声道音频和3路视频用一条信号线传输,如图6.48所示。2004年,消费电子工业开始将HDMI输出接口加入到DVD播放机和有线/卫星机顶盒中。随着广泛的使用,2005年,数字电视和LCD/等离子监视器也加入了HDMI输入接口。

图6.48 使用HDMI连接消费类设备以简化连接电缆

通过使用一个有适配器的电缆,HDMI后向兼容使用DVI和EIA-861数字电视接口的设备。虽然,HDMI有着优良的特性,但是诸如数字视频和消费类电子控制(用于设备之间传输控制命令)则没有提供。

技术

HDMI是基于DVI接口的,它还支持VESA的扩展显示识别数据(EDID)标准,显示数据通道(DDC)标准(以前读作EDID)。

另外,EIA-861标准规范了强制和可选支持分辨率和时序,以及如何加入如宽高比和格式信息的数据。

HDMI也支持了高带宽数字内容保护(HDCP)规范,以防止未经授权的内容拷贝。一个常见问题是,视频源设备不会去频繁查询(一秒两次)TV去确认TV的HDCP电路是否激活。这样如果电视的HDMI接口没选择,然后再选择,就会陷入“冻结”。

“A型”19针连接器使用一通道TMDS连接,所以可以传输视频的采样频率25~165MHz。传送视频采样频率小于25MHz(如13.5MHz480i和576i)的视频,采用像素重传机制。由于它的小尺寸更迎合了消费类设备的小尺寸要求。

为支持视频信号采样频率大于165MHz,使用“B型”29针双路连接器,对于PC应用的设计必须使用它。

视频数据格式

HDMI支持GRB,4:4:4YCbCr和4:2:2YCbCr视频格式,最高支持传送每像素24比特的数据。

对于640×480分辨率,R’G’B’数据的典型范围是00H~FFH。对于其它分辨率的YCbCr和GRG数据,典型范围是10H~EBH(数据小于10H或者大于EBH也偶尔用于处理)。

音频数据格式

支持DVD音频标准驱动,根据视频格式支持包含1~8路非压缩的音频流,最高支持48,96或192kHz的采样频率。它能支持传送最高到192kHz采样频率的压缩多通道交叉音频流。

数字平板(DFP)接口

VESA的数字平板(DFP)接口开发用于传送计算机的非压缩的数字视频信号到数字平板显示器。它支持VESA的插头和显示(P&G)标准,扩展显示识别数据(EDID)标准,显示数据通道(DDC)标准(以前读作EDID)和监视器定时规范(DMT)。DDC和EDID能支持显示器的自动检测和配置。“TFT数据映射”仅支持支持:一个时钟周期一个像素,一条通道8比特,MSB对齐。

如DVI一样,DFP使用过渡最小差分信号(TMDS)。8比特视频数据转换成10比特过渡最小直流平衡数值,然后串行化。接收端解串数据,并将数据转换成8比特。这样为了传送数字R’G’B’数据,需要3组TMDS信号构成一个TMDS接头。电缆长度最长可以支持到5米。

TMDS链路

单个TMDS连接,如图6.49所示,支持采样频率从22.5~160MHz格式和时序。

视频数据格式

24位R’G’B’数据用传输于链路,如图6.49所示。

控制信号

除了视频数据之外,DFP发送和接收芯片为连接系统中的其他芯片典型使用可达8个控制信号。

HSYNC 水平同步

VSYNC 垂直同步

DE 数据是能

CTL0~CTL3 保留(链路0)

CLK 1×采样时钟

当DE为“1”时,有效视频被传送。当DE为“0”时,HSYNC,VSYNC和CTL0~CTL3信号被传送。HSYNC和VSYNC可以是有极性的。

图6.49 DFP的TMDS连接

连接器

20-引脚带状迷你D型(MDR)连接器包含两行每行10针的20引脚,如图6.50所示。表6.39列举了引脚分布。

图6.50 DFP连接器

| 引脚 |

信号 |

引脚 |

信号 |

| 1 |

D1 |

11 |

D2 |

| 2 |

D1- |

12 |

D2- |

| 3 |

外壳 |

13 |

外壳 |

| 4 |

外壳 |

14 |

外壳 |

| 5 |

CLK |

15 |

D0 |

| 6 |

CLK- |

16 |

D0- |

| 7 |

地 |

17 |

悬空 |

| 8 |

+5V |

18 |

热插拔检测 |

| 9 |

悬空 |

19 |

DDC SDA |

| 10 |

悬空 |

20 |

DDC SCL |

表6.39 DFP连接器信号分布

开放式LVDS显示器接口(OpenLDI)

开放式LDI开发被用来传送计算机的非压缩数字视频信号到数字平板显示器。它是FPD连接的增强版,用来驱动笔记本电脑的显示屏,并支持VESA的插头和显示(P&G)标准,扩展显示识别数据(EDID)标准,显示数据通道(DDC)标准(以前读作EDID)和监视器定时规范(DMT)。DDC和EDID能支持显示器的自动检测和配置。

和DVI及DFP接口不同,开放LDI使用低电压差分信号(LVDS)。电缆长度最长可以支持10米。

LVDS连接

LVDS连接,如图6.51所示,支持采样频率从32. 5~160MHz的格式和时序。

8个串行数据线(A0~A7)和两条采样时钟线(CLK1和CLK2)被使用。实际的串行数据线使用条数依赖于像素格式,串行数据频率是7×采样时钟频率。CLK2信号为后向兼容接收端是FPD连接的双像素模式。

视频数据格式

单像素18比特,单像素24比特,双像素18比特或双像素24比特R’G’B’数据被传输于链路。表6.40列举了像素位数据和开放LDI位数据的分布。

单像素18比特R’G’B’格式使用3个6比特R’G’B’值:R0~R5,G0~G5和B0~B5。开放LDI串行数据线A0~A2用于传送这些数据。

单像素24比特R’G’B’格式使用3个8比特R’G’B’值:R0~R7,G0~G7和B0~B7。开放LDI串行数据线A0~A3用于传送这些数据。

双像素18比特R’G’B’格式将两像素表示为3对高/低6比特R’G’B’数值:RU0~RU5,GU0~GU5,BU0~BU5,RL0~RL5,GL0~GL5,BL0~BL5。每对高/低组合表示两个像素。开放LDI串行数据线使用A0~A2和A4~A6发送这些数据。

双像素24比特R’G’B’格式将两像素表示为3对高/低8比特R’G’B’数值:RU0~RU7,GU0~GU7,BU0~BU7,RL0~RL7,GL0~GL7,BL0~BL7。每对高/低组合表示两个像素。开放LDI串行数据线使用A0~A7发送这些数据。

图6.51 开放LDI的LVDS连接

| 每像素18比特数据 |

每像素24比特数据 |

开放LDI比特数据 |

| 5 |

7 |

5 |

| 4 |

6 |

4 |

| 3 |

5 |

3 |

| 2 |

4 |

2 |

| 1 |

3 |

1 |

| 0 |

2 |

0 |

|

|

1 |

7 |

| 0 |

6 |

表6.40 开放LDI比特分布

控制信号

除了视频数据之外,开放式LDI发送和接收芯片为连接系统中的其他芯片典型使用可达7个控制信号。

HSYNC 水平同步

VSYNC 垂直同步

DE 数据是能

CNTLE 保留

CNTLF 保留

CLK1 1×采样时钟

CLK2 1×采样时钟

在非平衡操作中,DE,HSYNC,VSYNC,CNTLE和CNTLF电平以非编码的形式在A2和A6比特流中发送。

在平衡操作中(被用于减少短期和长期直流偏压),一个直流平衡比特在A0~A7比特流中被发送,用于指示数据是原始的或者取反的。由于没有直接发送控制信号的线路,将DE电平在CLK1和CLK2的下降沿略微修改。HSYNC,VSYNC,CNTLE和CNTLF电平在消影期被发送,分别使用A0,A1,A5和A4信号的7比特码字。

连接器

36-引脚带状迷你D型(MDR)连接器被使用,类似于图6.50所示,另外包含两行每行8针的16引脚。表6.41列举了引脚分布。

| 引脚 |

信号 |

引脚 |

信号 |

引脚 |

信号 |

| 1 |

A0- |

13 |

+5V |

25 |

保留 |

| 2 |

A1- |

14 |

A4- |

26 |

保留 |

| 3 |

A2- |

15 |

A5- |

27 |

地 |

| 4 |

CLK1- |

16 |

A6- |

28 |

DDC SDA |

| 5 |

A3- |

17 |

A7- |

29 |

地 |

| 6 |

地 |

18 |

CLK2- |

30 |

USB- |

| 7 |

保留 |

19 |

A0 |

31 |

地 |

| 8 |

保留 |

20 |

A1 |

32 |

A4 |

| 9 |

保留 |

21 |

A2 |

33 |

A5 |

| 10 |

DDC SCL |

22 |

CLK1 |

34 |

A6 |

| 11 |

+5V |

23 |

A3 |

35 |

A7 |

| 12 |

USB |

24 |

保留 |

36 |

CLK2 |

表6.41 开放式LDI连接器信号分布

千兆视频接口(GVIF)

索尼的千兆视频接口(GVIF)开发使用单条差分信号传送非压缩的数字视频,来代替DVI,DFP和开放式LDI使用的多路视频信号。电缆最长支持10米。

GVIF连接

GVIF连接,如图6.52所示,支持采样频率从20~80MHz的格式和时序。对于更高速的时钟频率,使用一条以上的GVIF连接。

对于18比特R’G’B’数据,串行数据采样时钟频率是24×采样时钟频率,24比特R’G’B’数据,串行数据采样时钟频率是30×采样时钟频率。

图6.52 GVIF连接

视频数据格式

链路上传输18比特或24比特R’G’B’数据和定时信息。18比特R’G’B’格式使用3个6比特R’G’B’值:R0~R5,G0~G5和B0~B5。24比特R’G’B’格式使用3个8比特R’G’B’值:R0~R7,G0~G7和B0~B7。

18比特R’G’B’数据转换成24比特数据,是将R’G’B’数据分片成6组3比特数值,然后转换成6组4比特码。这样确保了接收端PLL锁相和好的直流平衡。

24比特R’G’B’数据转换成30比特数据,是将R’G’B’数据分片成6组4比特数值,然后转换成6组5比特码。

控制信号

除了视频数据之外,还包含6个控制信号。

HSYNC 水平同步

VSYNC 垂直同步

DE 数据是能

CTL0 保留

CTL1 保留

CLK 1×采样时钟

如果DE,HSYNC,VSYNC,CTL0和CTL1中的任意信号改变,在下一个CLK周期中一个特殊的30比特格式被使用。第一个6比特的头数据指示DE,HSYNC,VSYNC,CTL0或CTL1的新电平。它跟随在24比特的R’G’B’数据之后(除了奇数比特位的反码之外,未进行编码)。

值得注意的是,在消影周期中,非视频数据如数字音频可以被传送。CTL信号可以被用于指示非视频数据的存在。

消费类传输接口

若干传输接口,如USB2.0,以太网和IEEE1394用于消费类产品。当然,每种标准都有它的优点和不足。

USB2.0

在PC市场众所周知的PC外设连接技术中,在产品之间使用USB(通用串行总线)2.0传送压缩的音频/视频数据得到快速发展。

USB2.0为保证数据交互的时间能支持最高达480Mbps的同步传输模式。这样,它很容易将有线/卫星机顶盒或DVD播放机和数字电视之间实时传输压缩的音频/视频数据。DTCP(数字传送版权保护)可以被用于使用USB传输的音频和视频的加密。

由于USB成本低,并且广泛使用,许多公司用USB2.0代替火线(IEEE1394)用于产品之间传输压缩的音频/视频数据。然而,传输各种类型数据定义的方法要好的多,一些公司仍倾向于使用IEEE1394。

USB On-The-Go

随着便携设备的迅速流行,出现了不需要PC或USB主控器的连接需求。

“On-The-Go”满足了这个需求,它允许USB设备直接连接其他“On-The-Go”产品。它还具备了小的USB连接器特性和低功耗特性,延长了电池使用寿命。

以太网

随着家庭网络广泛使用DSL和光纤到户(FTTH),以太网成为了一个常用的传输数字音频和视频数据的接口。起初只用于传输文件,现在使用有线或无线以太网传输实时压缩视频已经变得平常。

普通以太网支持100Mbps速率,使用1Gbps的以太网现在开始增长。DTCP(数字传送版权保护)可以被用于使用有线或无线以太网传输的音频和视频的加密。

IEEE1394

IEEE1394最初开发用于苹果电脑,当时叫做火线。设计成设备之间通用的接口,1394规定了物理特性;分离特性规范规定了怎样在1394网络之间传输数据。开放电缆?,SCTE DVS-194,EIA-775和ITU-T J.117规定了在数字电视和机顶盒之间兼容支持IEEE1394规范。

1394是一种基于事务包的技术,使用一条双向串行连接,并支持即插即用。这样可以使设备之间的链接和断开不会影响网络中连接的其他设备。

对时间敏感的传输保证的支持,使得可以实时传输数字视频和音频。除此之外,多个独立的数字视频和音频数据可以同时被传送。

规范

最初版本的1394-1995规范支持数据比特率为98.304,196.6.8和393.216Mps。

1394A-2000规范澄清了模糊的和导致系统互操作型的问题。他还减少了总线控制,仲裁,总线复位时间和包级联的开销。1394A-2000还引入了先进的节电特性。电气信号的方式1394-1995和1394A-2000相同,使用数据选通(DS)编码和模拟信号速度。

1394B-2002规范增加了对786.432,1572.864和3145.728Mbps的支持。它还包括

-使用千兆以太网的8B/10B编码技术

-连续简单双工操作

-长距离传输(使用五类双绞线长度超过100米)

-对于许多数字方式,使用可变的信号速率

-三种类型的端口:传统接口(兼容1395A),贝塔和混合(支持传统和贝塔)。连接键控确保不兼容的连接不能在物理上建立。

大小头问题

1394使用大头架构,定义最高比特位是比特0。然而许多处理器是基于小头架构的,它们定义的最高比特为是比特31(假设一个字包含32比特)。

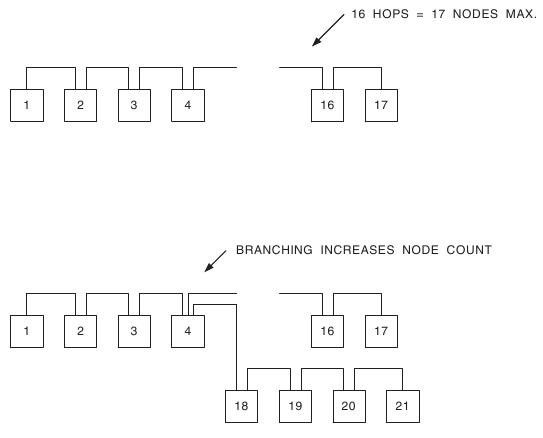

网络拓扑

同许多网络一样,没有设计总线主控器。树形的网络结构有一个根节点,其它设备位于分出去的支路上(图6.53)。在初始化时进行选择根节点,它负责一些控制功能。一旦选择确定,它在上电和联网时实现那些功能。

图6.53 IEEE1394网络拓扑例子

一个网络最多可以包括63个节点,每个节点(即设备)规定了6比特的物理识别码。网络之间可以通过桥相连,系统最多可以包括1024个网络,每个网路有自己的10比特总线ID。综合16比特的地址,一个系统最多可以包含64,449个节点。由于器件地址是64比特的,其中的16比特被用于指示节点和网络,剩下的48比特用于内存地址,它允许每个节点使用最大256TB的存储空间。

节点类型

1394总线上的节点的复杂性和能力多种多样(下面所列是从简单到复杂):

事物节点 的负责异步通信,使用最少的控制状态寄存器(CSR),执行最小的ROM配置。

同步节点 增加24.576MHz时钟,被用于计数器时钟周期,循环开始数据包升级。

循环主节点 增加了产生8kHz循环开始事件的能力,产生循环开始包,执行总线计数器功能。

同步资源管理(IRM)节点 增加了检测自ID包错误功能,确定IRM选择节点ID,使用可用通道,可用带宽和总线管理ID寄存器。一个支持同步通信的节点至少能够有IRM的能力。

总线控制(BM)节点 是最复杂的。这个级别的节点增加了负责拓扑映射中存储每一个自ID包和分析映射以产生整条总线速度的映射。这两个映射图用于管理整条总线。组后BM必须能够激活循环主节点,写配置包优化总线,并充当电源管理者。

节点端口

在网络拓扑总,一个但端口器件由于它位于一条网络支路的终点而被叫做“叶”设备。它们可以连接到网络,但不能扩展网络。

双端口器件可以用于组成菊花链拓扑结构。它们可以连接和级联网络,如图6.53所示。包含3个更多端口的器件可以分支网络直至包含63各节点的能力。

有一点需要说明的是网路中不允许有环路和并行连接。还有没有保留连接器──任何连接器被用来增加新的节点到网络。

由于1394-1995规定两个节点之间的电缆最多包含16“跳”,如果使用双端口外设,网络中最多可以使用17个外设。后来规范使用一个“拼”包来测量任何节点之间的往返延时,取消了16“跳”的限制。

对于1394-1995和1394A-200,使用一个4或6引脚的连接器。6引脚的连接器可以为外围设备提供电源。对于1394B-2002,使用9针的贝塔和混合连接器,包括电源,两个信号完整性引脚和一个将来使用的保留引脚。

图6.54所示是1394-1995和1394A-2000的数据和选通信号时序。选通信号在每个数据比特保持不变信号周期中改变状态。所以让数据和选通信号通过异或门就可以恢复时钟。

图6.54 IEEE1394数据和选通信号时序

物理层

一个典型的1394网络的硬件拓扑结构包括一个物理层(PHY)和一个链路层(LINK),如图6.55所示。1394-1955标准还定义了两个软件层,传输层和总线管理层,它们的部分可以由硬件实现。

图6.55 IEEE1394典型的物理层和链路层模块图

物理层在逻辑物理总线上实现点对点的网络传输。由于数据在每个节点上的始终恢复,所以本质上每个节点是一个数据收发器。物理层也定义了网络连接的电气和结构连接。还包括了物理信令电路和上电初始化,仲裁,总线复位检测和数据信号的逻辑响应。

链路层

链路层提供了物理层和应用层之间的联系,和用于网路传输的数据格式化打包功能。它同时支持异步和同步数据。

异步数据

为了保证异步数据包的可靠接收,当一个异步数据包后,接收端给发送端发送一个确认信息,如图6.56所示。然而,这种传输贷款不能保证。所以这种传输方式用于命令、非实时数据和无差错数据的传输。

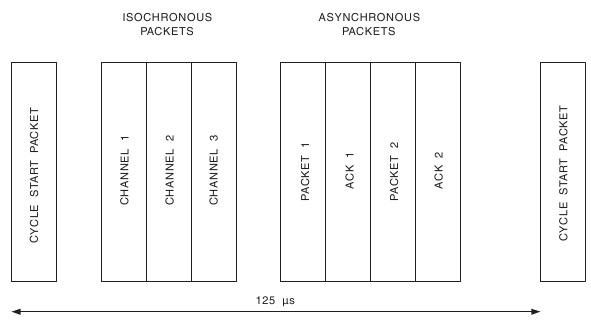

图6.56 IEEE1394同步和异步数据包

异步数据包的传输延迟得不到保证,它依赖于网络状况。但是,发送端在接收的确认数据包之前会不断的重发数据。

异步数据即发送给网络中的一个节点,也可以发送给网络中的所有节点,但是不能广播给总线中的节点的一个子集。

异步数据包的最大长度是:

512*(n/100)字节

n = 网络速度,单位是Mbps

同步数据

同步通信有确定的带宽,最高速度可以达到网络带宽的80%。可以使用最多63个独立通道,虽然1394开放主控制器接口(OHCI)现在只支持4~32个通道。由于同步传输数据包的最大传输延迟是克计算的和可以同时传输给多个目标设备,所以这种类型的通信用于实时影音数据传送。但是发送端可以不重发数据包。

同步数据包的最大长度是:

1024*(n/100)字节

n = 网络速度,单位是Mbps

同步操作确保每个时间片是125μs。由于时间间隙是保证的,并且同步通信的优先级高于异步通信,所以同步通信的带宽是可以保证的。

一旦同步通道被建立,发送设备在每个同步周期中保证拥有所需要的总线控制时间。在一个特定的通道中只有一个设备可以发送数据,但是通道中的所有设备都可以接收数据。只要容量可用一个设备可以使用多个通道。

传输层

传输层指示异步写入、读取和命令锁定。锁定结合了读写通过产生发送端和接收端之间的一个来回路由,包括接收端处理。

总线管理层

总线管理层功能是控制网络的物理层、链路层和传输层。

数字传输内容保护

为了排除未授权的内容拷贝,DTCP系统被开发。虽然最初设计用于1394,但它能应用于任何支持双向通信的数字网络,如USB和以太网。

DTCP支持设备认证,内容加密和可再生(都不应受设备的影响)。数字传输授权管理(DTLA)授权内容保护系统和分发密钥和设备认证。

DTCP内容保护的4个元素

1. 拷贝控制信息(CCI)

2. 认证和密钥交换

3. 内容加密

4. 系统可再生

拷贝信息控制(CCI)

CCI允许内容的拥有者规定他们的内容可以被怎样使用,如“不能拷贝”,“可以拷贝一次”,“拷贝次数用完”和“自由拷贝”。DTCP能在设备之间的安全通信拷贝控制信息。两种不同的CCI机制被支持:嵌入式 和加密模式标识。

嵌入式CCI位于数据流中。篡改内容流使得到不正确的解密结果,保证了嵌入CCI的完整性。

加密模式标识(EMI)提供了安全性,但容易获得,在同步传输包的包头的同步位的最高两位传输CCI信息。设备可以在不解码内容的情况下在内容流中迅速确定CCI。如果两个EMI位被篡改,加密和解密模式不匹配,导致不能正确揭秘内容。

认证和密钥交换

在共享内容之前,器件必须验证其它器件是否是认证的。DTCP可以选择两种认证之一:完全和受限。完全认证可以使用系统中所有保护的内容。受限认证可以仅使用系统中的“一个拷贝”和“不能再拷贝”的保护内容。

完全认证

DTLA向兼容设备派发一个统一的公共/私有密钥对和一个设备证书,它们被存于器件内部以防泄漏。除此之外,器件还存储它们必要的常数和密钥。

完全认证使用基于数字签名的密钥和密钥交换(DH)算法。DSS是一种完整验证的数字签名和验证签名数据文档方法。DH密钥交换被用于建立控制通道对称密钥,它允许多个设备生成共享密钥。

最初,接收端向发送端发送一个请求交换设备的证书和随机数。然后,每个设备计算一个DH密钥交换第一阶段数据。接下来设备交换带如下所示的签名信息:

1. 其它设备的随机数

2. DH密钥交换第一阶段数据

3. 重现最新系统版本号信息和重现设备存储的信息(SRM)

设备使用其它设备的公钥验证签名信息来验证信息没有经过修改和验证全部其它器件的证书。每个器件还检查嵌入于系统重生信息(SRM)的过期证书列表(CRL),来验证其他器件的证书没有注销,为了不破坏它的安全性。如果没有任何错误,两个设备互相验证成功并建立验证密钥。

受限认证

受限认证可以用于发送端和接收端交换“一次拷贝”和“拷贝用完”的内容。它依赖于一个共同的密钥来相应随机促发。

源端向接收端启动一个请求,查询接收端的器件ID,并发送一随机促发。接收端在收到的发送端的促发后,计算出响应并发送给源端。

源端比较使用服务密钥和接收端ID产生的本地信息和接收到的响应信息。如果和本地计算结果匹配,接收端就被验证和授权。然后源端和接收端各自计算授权密钥。

内容加密

为了保证互操作性,所有兼容设备必须支持56为M6基本密码。其它内容保护可以使用额外的可选密钥。

系统可再生

支持完全认证的设备可以接收和处理由DTLA生成的SRM内容和内容分发。系统可再生被用来注销受损器件的IDs来确保长期系统稳定性

SRM可以通过其它兼容设备来更新,它们可以通过预录的媒介或具有外部通信能力(因特网,电话,电缆,网络等)的兼容设备获得更新列表。

操作例子

在这个例子中,源端被指示传送一个拷贝保护的系统流内容。

源端启动发送标记为拷贝保护的内容,包括“一次拷贝”,“禁止拷贝”,“不能再拷贝”或“自由拷贝”。

在收到内容流之后,接收端确认拷贝保护状态。如果被标记为“禁止拷贝”,接收端向发送端请求启动完全认证。如果内容标记为“一次拷贝”或“不能再拷贝”,如果接收端支持完全认证,则发送完全认证请求,否则发送受限认证请求。

当源端接收到认证请求时,它根据请求认证的类型继续认证过程。如果请求的是完全认证,但是源端只支持受限认证,那么使用受限认证。

一旦设备完成整个认证过程,内容通道加密密钥(内容密钥)在它们之间交换。这个密钥被用于源端设备加密内容,接收端解密内容。

1394开放式主控器接口(OHCI)

1394开放式主控器接口(OHCI)是一个应用于1394链路层,增加额外特性能支持传输层和总线管理层的规范。它提供连接1394网络的标准化的途径。

家庭影院互联(HAVi)

家庭影院互联(HAVi)是1394的另一层协议。1394网络中不管是否存在PC主机,HAVi提供1394设备的即插即用的互联特性。

串行总线协议(SBP-2)

ANSI串行总线协议2(SBP-2)定义了在1394总线上的设备,如DVD播放机,打印机,扫描仪,硬盘驱动器和其它设备,传输命令和状态数据包的标准途径。

IEC61883规范

某些类型的同步信号,如MPEG-2和IEC61834,SMPTE314M和ITU-R BT.1618数字视频(DV)标准,使用规定的数据传输协议和格式。当这种数据在1394网络同步发送时,特殊的组包技术被使用。

IEC61883系列规范详细定义了在1394总线上传输各种应用数据的规范:

IEC 61883-1=通用规范

IEC 61883-2=SD-DVR数据传送于25Mbps连续比特率

IEC 61883-3=HD-DVR数据传输

IEC 61883-4=MPEG-TS流数据发送比特率并发最高到44Mbps

IEC 61883-5=SDL-DVCR数据传输

IEC 61883-6=音频和音乐数据传输

IEC 61883-7=ITU-R BO.1294 系统B数据传输

IEC 61883-1

IEC 61883-1定义在1394总线上传输数字音频和视频数据的通用架构。它描述了数字音频和数字视频数据的通用数据包格式,数据流管理和连接管理,还有控制命令的通用传输规则。

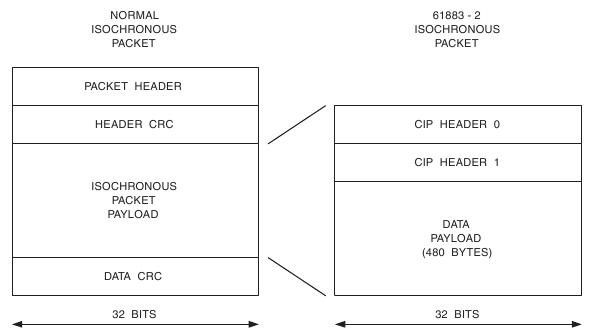

一个普通同步包(CIP)头被置于同步数据包的数据域开始处,如图6.57所示。它指示了数据域的源节点,数据块尺寸,数据块计数,时间戳,实时数据内容类型等。

连接管理进程(CMP)也被定义用于使用同步连接的设备之间。

除此之外,定义一个功能控制协议(FCP),它用于1394异步数据交换控制命令。

图6.57 61883-2同步包格式

IEC 61883-2

IEC 61883-1和SMPTE 396M定义了1394总线上的IEC61834,SMPTE 314M和ITU-R BT.1618数字视频(DV)标准的CIP头,数据包格式和发送时序。支持有效分辨率是720×480(每秒29.97帧)和720×576(每秒25帧)。

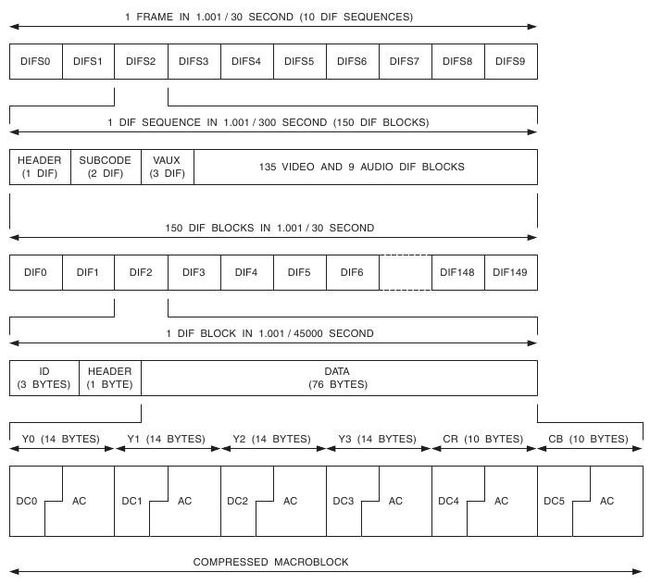

数据包长度是488字节,由8字节的CIP头和480字节的DV数据组成,如图6.57所示。图6.58显示了数据帧结构。

一帧720×480 4:1:1 YCbCr的数据压缩到103,950字节,压缩率是4.9:1。包括前部的开销和音频开销,数据增加到120,000字节。

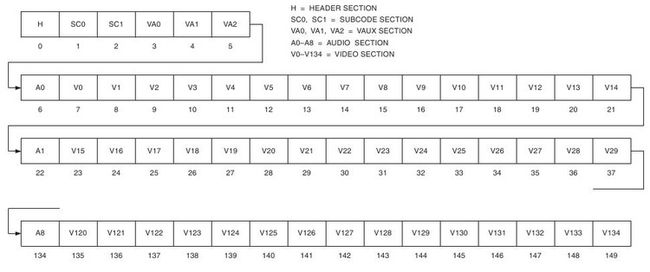

一个压缩的720×480帧被分成10个DIF(帧中数据)序列。每个DIF序列包括150个每包80字节的DIF块,使用如下:

135个视频DIF块

9个音频DIF块

6个DIF块用于包头,子码和视频辅助数据信息

图6.58 IEC 61834,SMPTE 314M和ITU-R BT.1618的720×576系统(4:1:1YCbCr)数据包格式

图6.59 IEC 61834,SMPTE 314M和ITU-R BT.1618 详情的DIF序列(25Mbps)

图6.59所示是DIF序列的详细架构。音频DIF块包含音频数据和音频辅助数据(AAUX)。IEC61834支持4通道32kHz 12比非特线性音频信号,或2通道48,44.1或32kHz 16比特音频信号。SMPTE 314M和ITU-R BT.1618 25Mbps支持2路48kHz 16比特音频信号,而50Mbps版本支持4路。视频辅助数据(VAUX)DIF块包括录制日期和时间,镜头光圈,快门速度,颜色平衡和其它摄像机设置数据。子码DIF块存储多种信息,其中最重要的是时间码。

每一个视频DIF块包括80字节压缩的宏块数据:

3字节的DIF块ID信息

1字节的头数据,包括量化数值(QNO)和块状态(STA)

Y0,Y1,Y2和Y3每个14字节。

Cb和Cr每个10字节

作为在1394网络上传输每包488字节的包,视频帧的开始是确定的。一旦一个帧的开始被监测到,一完整的DV帧由包含由250个有效包数据包组成一组;每包包含6个DIF数据块。每组中的第15个数据包是空包,应该被丢弃。一旦缓存中250个有效的包,丢弃CIP头。如果都没出问题,你就有一个缓存帧,它包含一个120,000字节的DV帧。

720×576帧可能使用4:2:0YCbCr格式(IEC 61834)或4:1:1YCbCr格式(SMPTE 314M和ITU-R BT.1618),并需要12个DIF序列。一帧720×576的数据压缩到124,740字节。包括前部的开销和音频开销,数据增加到144,000字节,需要传送30包。

注意,由于数字传输不要求纠错操作,所以传送于1394网络的数据组织不同于现实中的DV数据记录格式。除此之外,虽然图5.59中的视频数据块是按顺序编号的,但是视频数据块的传输不是从左到右,从上到下对应的。为了减少出错和错误隐藏,宏块压缩是被重排的。音频数据也是重排的。数据传输和存储的重排顺序是一致的。

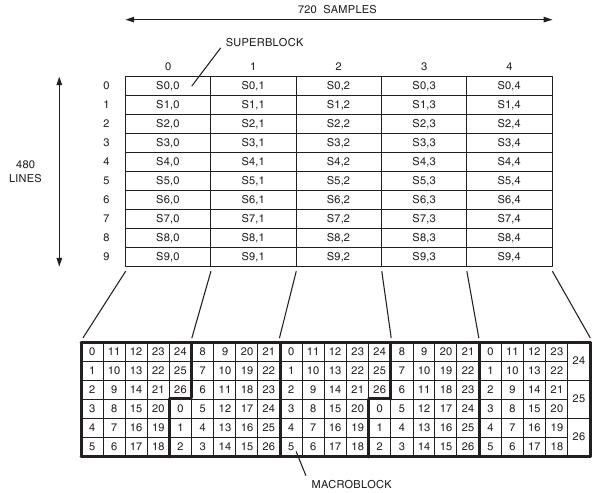

为了说明视频数据的重排,DV视频帧被组织成50个超级块,每个超级块由27个压缩宏块组成,如图6.60所示。每5个超级块(每个来自超级块的一列)组成一个DIF序列。表6.42说明了DIF块的发送顺序。DV数据架构的其它信息在第11章中说明。

IEC 61883-4

IEC 61883-4定义了在1394网络上传输MPEG-2传送流的CIP头,数据格式和发送时序。

每个同步包传送整数个192字节(188字节MPEG-2数据加4字节时间戳)的数据包是最高效的,如图6.61所示。然而,MPEG数据速率很少是同步数据速率的整数倍。这样,将MPEG数据包分成最大24字节较小的分量以最大化利用有效带宽是更有效率的。发送端使用数据块的整数倍(0,1,2,4或8倍)填充到一个同步数据包中,并加8字节的CIP头。

图6.60 超级块和宏块的关系(720×480,4:1:1 YCbCr)

图6.61 61883-4 同步包格式

| DIF序列编号 |

视频DIF块编号 |

压缩的宏块 |

DIF序列编号 |

视频DIF块编号 |

压缩的宏块 |

||

| 超级块编号 |

宏块编号 |

超级块编号 |

宏块编号 |

||||

| 0 |

0 |

2,2 |

0 |

… |

|||

| 1 |

6,1 |

0 |

n-1 |

0 |

1,2 |

0 |

|

| 2 |

8,3 |

0 |

1 |

5,1 |

0 |

||

| 3 |

0,0 |

0 |

2 |

7,3 |

0 |

||

| 4 |

4,4 |

0 |

3 |

n-1,0 |

0 |

||

| … |

4 |

3,4 |

0 |

||||

| 133 |

0,0 |

26 |

… |

||||

| 134 |

4,4 |

26 |

133 |

n-1,0 |

26 |

||

| 1 |

0 |

3,2 |

|

134 |

3,4 |

26 |

|

| 1 |

7,1 |

0 |

|

||||

| 2 |

9,3 |

0 |

|||||

| 3 |

1,0 |

0 |

|||||

| 4 |

5,4 |

0 |

|||||

| … |

|||||||

| 133 |

1,0 |

26 |

|||||

| 134 |

5,4 |

26 |

|||||

注:1.对于480-行系统,n=10,对于576-行系统,n=12

表6.2 25Mbps的视频DIF块和压缩宏块

50Mbps DV

和25Mbps DV格式一样,50Mbps DV格式支持720×480i 30和720×576i 25数据源。然而50Mbps DV使用4:2:2 YCbCr格式而不是4:1:1 YCbCr格式。

如前面讨论的,25Mbps DV流的源数据包长度是480字节(包括6个DIF块)。每包480个字节的250个数据包(对于576i 25系统是300个包)传送于25Mbps通道。

50Mbps DV流的源数据包包括960个字节(包括12个DIF块)。每个包含960个字节数据包的前面125个包(对于对于576i 25系统是150个包)传送于25Mbps通道,接下来的25个包(对于对于576i 25系统是150个包)传送于第二个25Mbps通道。

100Mbps DV

100Mbps DV流支持1920×1080i 30,1920×1080i 25和1280×720p 60格式的视频源。1920×1080i 30视频源横向变换为1280×1080i 30。1920×1080i 25视频源横向变换为1440×1080i 25。1280×760p 60视频源横向变换为960×720p 60。使用4:2:2 YCbCr格式。

100Mbps DV流的源数据包包括1920个字节(包括24个DIF块)。每个包含1920个字节数据包的前面63个包(对于对于1080i 25系统是75个包)传送于25Mbps通道,接下来的62个包(对于对于1080i 25系统是75个包)传送于第二个25Mbps通道,接下来的63个包(对于对于1080i 25系统是75个包)传送于第三个25Mbps通道,最后的62个包(对于对于1080i 25系统是75个包)传送于第四个25Mbps通道。

数字摄像机规范

1394贸易协会制定了基于1394的数字摄像机规范。这样避免了执行完整IEC 61883规范高的芯片和软件成本。

7种分辨率被定义用于支持宽范围的视频格式

160×120 4:4:4 YCbCr

320×240 4:2:2 YCbCr

640×480 4:1:1,4:2:2 YCbCr,24位RGB

800×600 4:2:2 YCbCr,24位RGB

1024×768 4:2:2 YCbCr,24位RGB

1280×960 4:2:2 YCbCr,24位RGB

1600×1200 4:2:2 YCbCr,24位RGB

支持的帧频为每秒1.875,3.75,7.5,15,30和60帧。

同步包被用来在1394网络上传输非压缩的数字视频数据。

参考资料

1. 1394-based Digital Camera Specification, Version 1.20, July 23, 1998.

2. Digital Transmission Content Protection Specification, Volume 1 (Informational Version), July 25, 2000.

3. Digital Visual Interface (DVI), April 2, 1999.

4. EBU Tech. 3267-E, 1992, EBU Interfaces for 625-Line Digital Video Signals at the 4:2:2 Level of CCIR Recommendation 601, European Broadcasting Union, June, 1991.

5. IEC 61883–1, 2003, Consumer Audio/Video Equipment—Digital Interface—Part 1: General.

6. IEC 61883–2, 1998, Consumer Audio/Video Equipment—Digital Interface—Part 2: SD-DVCR Data Transmission.

7. IEC 61883–3, 1998, Consumer Audio/Video Equipment—Digital Interface—Part 3: HD-DVCR Data Transmission.

8. IEC 61883–4, 1998, Consumer Audio/Video Equipment—Digital Interface—Part 4: MPEG-2 TS Data Transmission.

9. IEC 61883–5, 1998, Consumer Audio/Video Equipment—Digital Interface—Part 5: SDL-DVCR Data Transmission.

10. ITU-R BT.656–4, 1998, Interfaces for Digital Component Video Signals in 525-Line and 625-Line Television Systems Operating at the 4:2:2 Level of Recommendation ITU-R BT.601.

11. ITU-R BT.799–3, 1998, Interfaces For Digital Component Video Signals in 525-Line and 625-Line Television Systems Operating at the 4:4:4 Level of Recommendation ITU-R BT.601 (Part A).

12. ITU-R BT.1302, 1997, Interfaces for Digital Component Video Signals in 525-Line and 625-Line Television Systems Operating at the 4:2:2 Level of ITU-R BT.601.

13. ITU-R BT.1303, 1997, Interfaces For Digital Component Video Signals in 525-Line and 625-Line Television Systems Operating at the 4:4:4 Level of Recommendation ITU-R BT.601 (Part B).

14. ITU-R BT.1304, 1997, Checksum for Error Detection and Status Information in Interfaces Conforming to ITU-R BT.656 and ITU-R BT.799.

15. ITU-R BT.1305, 1997, Digital Audio and Auxiliary Data as Ancillary Data Signals in Interfaces Conforming to ITU-R BT.656 and ITU-R BT.799.

16. ITU-R BT.1362, 1998, Interfaces For Digital Component Video Signals in 525-Line and 625-Line Progressive Scan Television Systems.

17. ITU-R BT.1364, 1998, Format of Ancillary Data Signals Carried in Digital Component Studio Interfaces.

18. ITU-R BT.1365, 1998, 24-Bit Digital Audio Format as Ancillary Data Signals in HDTV Serial Interfaces.

19. ITU-R BT.1366, 1998, Transmission of Time Code and Control Code in the Ancillary Data Space of a Digital Television Stream According to ITU-R BT.656, ITU-R BT.799, and ITU-R BT.1120.

20. ITU-R BT.1381–1, 2001, Serial Digital Interface-based Transport Interface for Compressed Television Signals In Networked Television Production Based On Recommendations ITU-R BT.656 and ITU-R BT.1302.

21. ITU-R BT.1577, 2002, Serial digital interface-based transport interface for

compressed television signals in networked television production based on Recommendation ITU-R BT.1120.

22. ITU-R BT.1616, 2003, Data stream format for the exchange of DV-based audio, data and compressed video over interfaces complying with Recommendation ITU-R BT.1381.

23. ITU-R BT.1617, 2003, Format for transmission of DV compressed video, audio and data over interfaces complying with Recommendation ITU-R BT.1381.

24. ITU-R BT.1618, 2003, Data structure for DV-based audio, data and compressed video at data rates of 25 and 50 Mbit/s.

25. ITU-R BT.1619, 2003, Vertical ancillary data mapping for serial digital interface.26. ITU-R BT.1620, 2003, Data structure for DV-based audio, data and compressed video at a data rate of 100 Mbit/s.

27. Kikuchi, Hidekazu et. al., A 1-bit Serial Interface Chip Set for Full-Color XGA Pic-tures, Society for Information Display, 1999.

28. Kikuchi, Hidekazu et. al., Gigabit Video Interface: A Fully Serialized Data Trans-mission System for Digital Moving Pictures, International Conference on Consumer Electronics, 1998.

29. Open LVDS Display Interface (OpenLDI) Specification, v0.95, May 13, 1999.30. SMPTE 125M–1995, Television—Compo-nent Video Signal 4:2:2—Bit-Parallel Digi-tal Interface.

31. SMPTE 240M–1999, Television—Signal Parameters—1125-Line High-Definition Production Systems.

32. SMPTE 244M–2003, Television—System M/NTSC Composite Video Signals—Bit-Parallel Digital Interface.

33. SMPTE 259M–1997, Television—10-Bit 4:2:2 Component and 4FSC

Composite Digi-tal Signals—Serial Digital Interface.

34. SMPTE 260M–1999, Television—1125/60 High-Definition Production System—Digital Representation and Bit-Parallel Interface.

35. SMPTE 266M–2002, Television—4:2:2 Digital Component Systems—Digital Verti-cal Interval Time Code.

36. SMPTE 267M–1995, Television—Bit-Par-allel Digital Interface—Component Video Signal 4:2:2 16 9 Aspect Ratio.

37. SMPTE 272M–1994, Television—Format-ting AES/EBU Audio and Auxiliary Data into Digital Video Ancillary Data Space.

38. SMPTE 274M–2003, Television—1920 1080 Image Sample Structure, Digital Rep-resentation and Digital Timing Reference Sequences for Multiple Picture Rates.

39. SMPTE 291M–1998, Television—Ancil-lary Data Packet and Space Formatting.

40. SMPTE 292M–1998, Television—Bit-Serial Digital Interface for High-Definition Televi-sion Systems.

41. SMPTE 293M–2003, Television—720 483 Active Line at 59.94-Hz Progressive Scan Production—Digital Representation.

42. SMPTE 294M–2001, Television—720 483 Active Line at 59.94 Hz Progressive Scan Production—Bit-Serial Interfaces.

43. SMPTE 296M–2001, Television—1280 720 Progressive Image Sample Structure, Analog and Digital Representation and Analog Interface.

44. SMPTE 305.2M–2000, Television—Serial Data Transport Interface (SDTI).

45. SMPTE 314M–1999, Television—Data Structure for DV-Based Audio, Data and Compressed Video—25 and 50 Mb/s.

46. SMPTE 326M–2000, Television—SDTI Content Package Format (SDTI-CP).

47. SMPTE 334M–2000, Television—Vertical Ancillary Data Mapping for Bit-Serial Interface.

48. SMPTE 344M–2000, Television—540 Mbps Serial Digital Interface.

49. SMPTE 348M–2000, Television—High Data-Rate Serial Data Transport Interface (HD-SDTI).

50. SMPTE 370M–2002, Television—Data Structure for DV-Based Audio, Data and Compressed Video at 100 Mb/s 1080/60i, 1080/50i, 720-60p.

51. SMPTE 372M–2002, Television—Dual Link 292M Interface for 1920 1080 Pic-ture Raster.

52. SMPTE 396M–2003, Television—Packet Format and Transmission Timing of DV-Based Data Streams over IEEE 1394.

53. SMPTE RP-165–1994, Error Detection Checkwords and Status Flags for Use in Bit-Serial Digital Interfaces for Television.

54. SMPTE RP-174–1993, Bit-Parallel Digital Interface for 4:4:4:4 Component Video Signal (Single Link).

55. SMPTE RP-175–1997, Digital Interface for 4:4:4:4 Component Video Signal (Dual Link).

56. SMPTE RP-168–2002, Definition of Vertical Interval Switching Point for Synchronous Video Switching.

57. SMPTE RP-188–1999, Transmission of Time Code and Control Code in the

Ancillary Data Space of a Digital Television Data Stream.

58. SMPTE RP-208–2002, Transport of VBI Packet Data in Ancillary Data Packets.

59. Teener, Michael D. Johas, IEEE 1394-1995 High Performance Serial Bus, 1394 Developer’s Conference, 1997.

60. VESA DFP 1.0: Digital Flat Panel (DFP) Standard.

61. VESA Video Interface Port (VIP), Version 2, October 21, 1998.

62. VMI Specification, v1.4, January 30, 1996.

63. Wickelgren, Ingrid J., The Facts about FireWire, IEEE Spectrum, April 1997.