硬件工程师面试经历2015---笔试篇

今年就业形势:今年形势依旧不景气,英特尔硬件部门基本不招人,思科硬件部门和信号完整性方面也不招人,EMC,IBM,AMD硬件开发也没有名额,可能会有校招,但一般是噱头做广告。英伟达倒是搞的轰轰烈烈,最后也没招人。后面的同学不要对这些公司抱太多希望。

从8月份开始起到现在找工作花了3个多月,慢慢的也接近尾声了,因此我考虑着花点时间把这段时间的笔试面试好好总结一下,也供正在找工作或者以后即将找工作的小伙伴们作为参考。

下面主要说一下我笔试面试公司的过程,本篇主要侧重笔试(面试稍后补上),按时间先后顺序:

1 、华为:

硬件没有笔试,首先是一面,技术面,大概只有15分钟,然后性格测试(会刷人),但一般性格测试可以做两遍。最后综合面试了,一般大概也只有一刻钟。

2、中兴:

有笔试,然后技术面,2对1,两个面试官会轮流问问题,大概20分钟,紧接着综合面,有英语,大概也要20分钟。的并且笔试一般会和射频,天线,微波,通信的一起考,所以卷子一般只用做自己熟悉的部分就好了。CMOS不用输入管脚该怎么处理(不能悬空)。串联负反馈和并联负反馈的作用。PCB走线特性阻抗的影响因素(线宽,介电常数,铜箔厚度,PCB板材等)。差分信号线阻抗匹配一般是(100欧姆~120欧姆)。4G LTE基础知识的考察。达林顿管连接判断和计算。轨到轨运放的基础知识。对光接入网知识的理解(大题)。OFDM系统中峰均比的解释以及解决办法(大题)。用两个MOS管搭一个开关电路(大题)。整体而言都是基础题目。

3、 英伟达:

英伟达是发一份word的笔试题到邮箱,然后限定两个小时做好再发过去,大概10个大题,主要是数字电路方面的。但今年英伟达基本不招人。题目有解释什么是非稳态,以及怎么消除。信号的串扰有什么危害,怎么解决。用2:1MUX构成与门和或门(连一根线就可以了)。给一个数字电路的框图化简。其余的题目我贴几个在下文,大家可以试着做做。应该说好好看看数电,可以做出一大半出来。

3). Given a list (5, 1, 17, 8), write aprocedure to return a sorted list in ascending order (1,5,8,17).

5). Please use Binary Gray Code to designa 4 bits 10 states code (0 1 2 3 4 5 6 7 8 9, total 10 states)

7). Please implement following functionswith a 2:1 MUX.

Y=A&B; Y=A||B;

4 、百度:

硬件就一个岗位,笔试主要是FPGA方向的,但笔试过后基本都没通知了。百度硬件目前主要也只在北京招人。百度这两年的笔试题有很大的相似处,具体的笔试题可以看我上一篇博客。

5 、CVTE:

(18w)这家公司比较奇特,首先不让投简历,他有一系列测评,包括逻辑,数字,硬件基础知识的题目,只有通过了才有资格投简历。网上测试的题目很基础。然后,一面是一对三,面试官会问一些问题,让大家依次回答,不涉及技术,一面一般刷掉三分之二的人。笔试题有对采样定理的描述。给一个线性电源计算效率。还有两个稳压管并联,问输出。三极管放大状态特点,和计算。单片机工作的几个要素。给三个电压问是什么三极管。几种功放性能的比较。LC谐振电路。恒流源和恒压源的比较。三端集成稳压器的计算。

6 、思科:

今年没有硬件岗位,投了一个硬件支持的岗位,笔试时发现都是软件的题目,一共六部分,选择作两部分,C/C++,数据库,操作系统,Python, 网络,JAVA。并且答题要求挺坑的,答对一题得1分,答错一题扣0.5分。招人很少,题目大部分都不会,做了炮灰。

7、 阿尔卡特朗讯:

笔试,主要是高速电路设计,信号完整性方面的题目,然后技术面,2对1,大概25分钟,有英语。最后HR面,英语聊天十分钟,但也有做自我介绍,项目之类的,因人而异。

解决串扰问题(3W规则)。电磁干扰EMC。OC门要加上拉电阻原因。振铃的考察。Watchdog的原理。LVDS电平的特点以及优势(大题)。IIC总线的verilog实现并画出时钟的对应波形(告诉从设备地址,寄存器地址,写入数据)那么顺序是:起始位—从设备地址—ACK位—寄存器地址—ACK位—写入数据—ACK位—停止位。

给一个CPU和几片存储器让画出连接图(大题)。

DC/DC噪声产生的原因,MOS管反接肖特基二极管的作用(大题)。

8 、斐讯:

(8k*13, 包吃住)模电和数电的基础题,很简单。笔试过了就面试,由于和其他公司冲突,邀请了两次我都没去面试。

串联两个稳压管问输出电压。锁存器的作用。ADC每提高1bit, 抗干扰能力可以提高6db。三极管放大电路三种组态的优缺点。给一个电容的容值和ESL问滤波范围。三极管给出电压,让判断每一极。与或非门的考察。什么是电感饱和。存储电路的设计。复位电路并联二极管的作用(为电容提供泄放电压的通道)。积分运放电路输入输出的计算。

9 、联影:

国家扶持的,感觉前途还不错,首先笔试,题目很基础。但因为上海是最后一站,一般岗位也只要一两个人,所以上海这边也是走走过场,没怎么要人面试。串行通信协议种类。陶瓷电容,钽电容,铝电解电容容值对比。CMOS输入输出逻辑电平。共模抑制比作用。锁相环的组成。TTL和CMOS电平的对比。然后给出一个情景让画出卡罗图化简,并且画出逻辑电路。画出一个单片机的外围结构电路,有开门狗,存储电路,复位电源等等。最后一个三极管放大电路计算。贴出题目如下:

10、 环旭电子:

(据说10k*13, 包住,有中餐)两面,先笔试,在面试。笔试也主要考基础。但对公司做的东西没什么兴趣。

笔试主要是:温度升高,二极管导通电压将(减小)。三极管放大截止电路的判断。存储电路的考察。二极管单向导通电路的考察。眼图的作用,怎么观察。解释建立时间和保持时间。

11 、菲尼萨:

没有笔试,就两轮面试,技术面和HR面大概各50分钟。

12 、兆芯:

部分职位有笔试,我投的岗位没有笔试,四轮面试。总共用了3个小时。混合电路设计有笔试题。

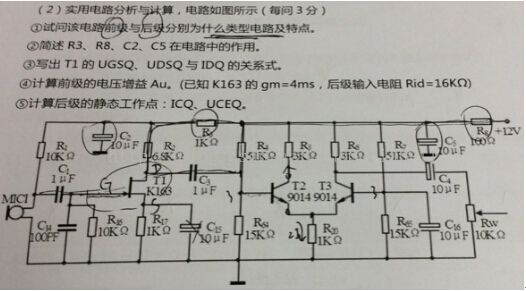

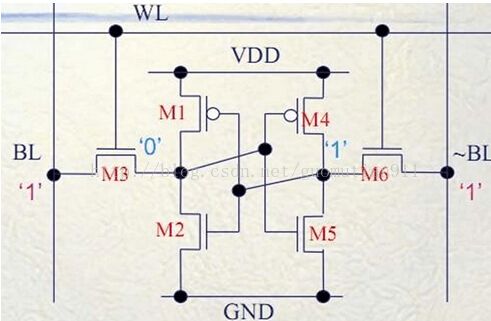

SRAM最小电路的分析和改进。如下图这个电路工作原理。

解释建立时间保持时间。用最少资源写16为加法器(FPGA)。

用静态和动态的mos管画或非门和非门。密勒效应和应用。

MOS管电流源噪声的分析。还有几个IC电路设计的不太会。

13 、中电集团36所:

一轮面试。很简单的问题。

14 、国家核电:

先面试,在体检,在笔试,笔试大概3小时。

15、中国银行:

笔试,4小时。然后面试。

16 、中国农业银行:

笔试3小时,然后面试。

17 、上海银行:

笔试1小时,少量逻辑题目,然后就是性格测试,然后面试。

大概就写到这里吧。想到其他的再补充。总结的话,要通过笔试,模电数电一定要好好看看,二极管,三极管,运放的计算一般是必考。数电里面画与非门,或非门,化简,触发器也经常考。还有就是DC/DC,LDO也会有所涉及。另外存储器一般也作为大题出现,应该注意。最后PCB布板,高速电路中阻抗匹配,串扰,反射振铃有时也会出现。

作者:http://bbs.ednchina.com/BLOG_ARTICLE_3025693.HTM