FPGA学习笔记之数字电路篇

第一章 数字电路的基础知识

1.1 数字电路和模拟电路

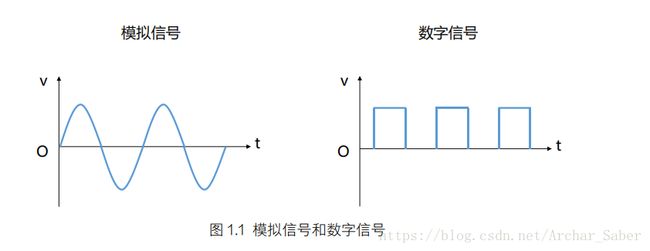

模拟信号,就是指随时间连续变化的信号。数字信号,就是指该信号无论从时间上还是从大小上看其变化都是不连续的。

1.2 数制与编码

1.3 逻辑代数

1.4 一般的Verilog语法结构

module 模块名

(

端口名1,端口名2,端口名3,....

)

端口类型说明(input,output,inout);

参数定义(可选);

数据类型定义(wire,reg等)

实例引用低层次模块和基本门级元件;

连续赋值语句(assign);

过程赋值语句(initial和always);

功能描述语句;

任务和函数;

endmodule

1.4 与门电路的verilog

module yumen

(

A,B,Y

);

input A;

input B;

output Y;

assign Y=A&&B; #assign是针对wire变量的一种连续赋值语句

endmodule引用低层次模块的描述方法实现与门电路

module yumen

(

A,B,Y

);

input A;

input B;

output Y;

and (Y,A,B);

endmodule利用过程赋值语句来描述与门电路

module yumen

(

A,B,Y

);

input A;

input B;

output Y;

reg Y;

always @(A,B)

Y=A&&B;

endmodule第二章 组合逻辑电路的分析和设计

2.1 九条基本定律

2.2 三变量最小项

2.3 格雷码

二进制转格雷码:

(1)二进制第一位和第二位进行异或,得到的结果就是格雷码的第一位。

(2)二进制第二位和第三位进行异或,得到的结果就是格雷码的第二位。

(3)二进制第三位和第四位进行异或,得到的结果就是格雷码的第三位。

(4)二进制第四位保持不变,就是格雷码的第四位。

格雷码转二进制:

(1)格雷码第四位保持不变,作为二进制的第四位。

(2)格雷码的第三位和第四位异或,作为二进制的第三位。

(3)格雷码的第二位和第三位异或,作为二进制的第二位。

(4)格雷码的第一位和第二位异或,作为二进制的第一位。

2.3 组合逻辑电路的设计

实际逻辑问题转化为真值表,在写出逻辑表达式,然后化简成为最简表达式,画出逻辑图。

2.4 竞争和冒险

逻辑竞争,逻辑冒险和功能竞争,功能冒险。

功能竞争,就是当多个变量经过两条以上的路径到达输出端时,同样也会产生竞争。在具有功能竞争的组合电路中,也同样会产生冒险。

逻辑竞争和逻辑冒险针对的是单个变量。

2.5 逻辑冒险的识别和消除

1.逻辑冒险的识别

如果逻辑表达式能转换为原变量和其反变量的乘积,则该电路存在1型冒险。

如果逻辑表达式能转换为原变量和其反变量的和,则该电路存在0型冒险。

输入变量在相邻卡诺图的相邻处发生变化。简单的说就是化简时,有相切的圆圈。

2.逻辑冒险的消除

增加冗余项。

2.6 功能冒险的识别与消除

1.功能冒险的识别

若电路具有下列三点,则其输出可能产生功能冒险:

(1)有两个以上变量同时发生变化(如果仅有一个输入变量发生变化则无功能冒险)

(2)变化前后,输出稳态值保持不变。

(3)在由n(n大于等于2)个变量发送变化的2^n个方格中,既要有0,又要有1(如果对应2^n个变量取值组合的输出值全1或全0,电路是不会产生功能冒险的)。

2.功能冒险的消除

增加选通信号或者增加输出滤波电容方法。